Technologie industrielle

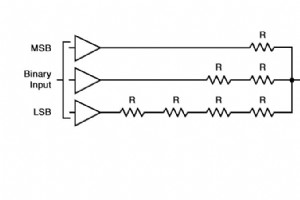

Le circuit DAC R/2R est une alternative au DAC à entrée pondérée binaire (R/2nR) qui utilise moins de valeurs de résistance uniques. DAC R/2R vs. DAC R/2nR Un inconvénient de lancienne conception DAC était son exigence de plusieurs valeurs de résistance dentrée précises :une valeur unique par bit

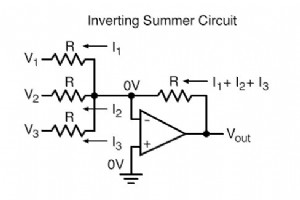

Quest-ce quun circuit DAC R/2nR ? Le circuit R/2nR DAC, également connu sous le nom dentrée pondérée binaire DAC, est une variante du circuit dampli-op sommateur inverseur. (Notez que les circuits « de sommation » sont parfois également appelés circuits « dété ».) Si vous vous en souvenez, le circ

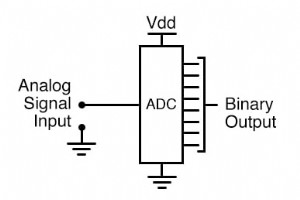

La connexion de circuits numériques aux capteurs est simple si les capteurs sont eux-mêmes numériques par nature. Les commutateurs, les relais et les encodeurs sont facilement interfacés avec les circuits de porte en raison de la nature marche/arrêt de leurs signaux. Cependant, lorsque des appareil

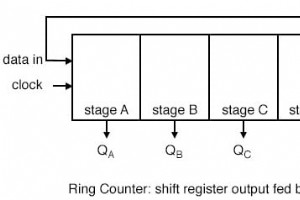

Si la sortie dun registre à décalage est renvoyée à lentrée. un compteur de sonneries en résulte. Le modèle de données contenu dans le registre à décalage recirculera tant que les impulsions dhorloge seront appliquées. Par exemple, le modèle de données se répétera toutes les quatre impulsions dhorl

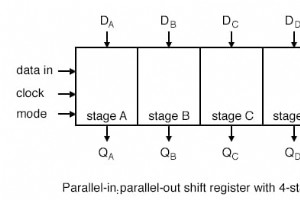

Le but du registre à décalage entrée/sortie parallèle est de prendre des données parallèles, de les décaler, puis de les sortir comme indiqué ci-dessous. Un registre à décalage universel est un appareil à tout faire en plus de la fonction dentrée/sortie parallèle. Ci-dessus, nous appliquons

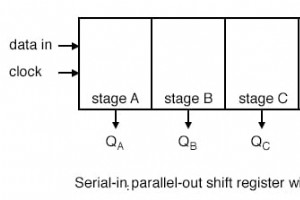

Un registre à décalage dentrée série et de sortie parallèle est similaire au registre à décalage dentrée série et de sortie série en ce sens quil transfère les données dans des éléments de stockage internes et décale les données au niveau de la sortie série, de la sortie des données, de la broche.

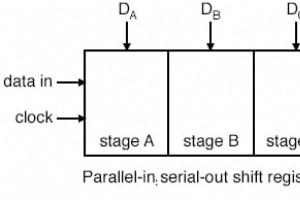

Les registres à décalage dentrée/sortie parallèle font tout ce que font les précédents registres à décalage dentrée/sortie série, ainsi que les données dentrée à tous les étages simultanément. Le registre à décalage entrée parallèle/sortie série stocke les données, les décale horloge par horloge et

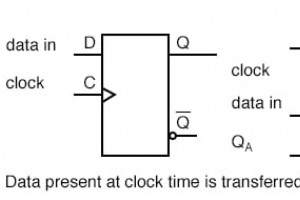

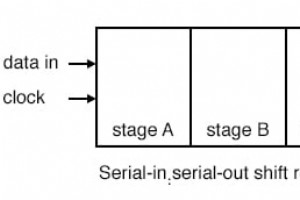

Les registres à décalage dentrée et de sortie série retardent les données dun temps dhorloge pour chaque étape. Ils stockeront un peu de données pour chaque registre. Un registre à décalage dentrée et de sortie série peut avoir une longueur de 1 à 64 bits, plus long si les registres ou les packages

Les registres à décalage, comme les compteurs, sont une forme de logique séquentielle . La logique séquentielle, contrairement à la logique combinatoire, nest pas seulement affectée par les entrées présentes, mais aussi par lhistorique antérieur. En dautres termes, la logique séquentielle se souvi

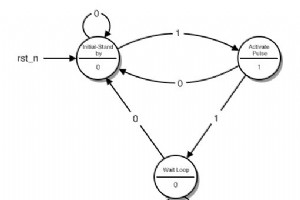

Jusquà présent, chaque circuit présenté était une combinatoire circuit. Cela signifie que sa sortie ne dépend que de ses entrées de courant. Les entrées précédentes pour ce type de circuits nont aucun effet sur la sortie. Cependant, il existe de nombreuses applications où il est nécessaire que nos

Incomplet

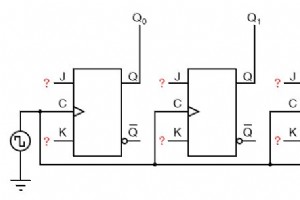

Quest-ce quun Synchrone Compteur ? Un compteur synchrone , contrairement à un compteur asynchrone , est celui dont les bits de sortie changent détat simultanément, sans ondulation. La seule façon de construire un tel circuit de compteur à partir de bascules J-K est de connecter toutes les entrées

Dans la section précédente, nous avons vu un circuit utilisant une bascule J-K qui comptait à rebours dans une séquence binaire de deux bits, de 11 à 10 à 01 à 00. Puisquil serait souhaitable davoir un circuit qui puisse compter en avant et pas seulement en arrière, il serait intéressant dexaminer

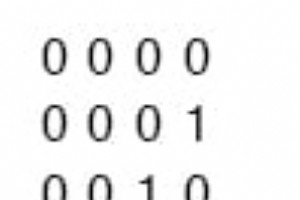

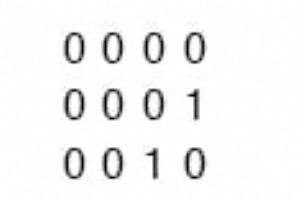

Si nous examinons une séquence de comptage binaire à quatre bits de 0000 à 1111, un modèle défini sera évident dans les « oscillations » des bits entre 0 et 1 : Notez comment le bit le moins significatif (LSB) bascule entre 0 et 1 pour chaque étape de la séquence de comptage, tandis que chaque bi

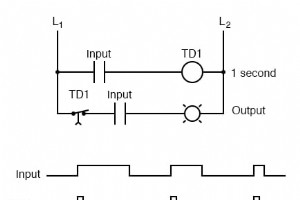

Nous avons déjà vu un exemple de multivibrateur monostable utilisé :le détecteur dimpulsions utilisé dans le circuit des bascules, pour activer la partie de verrouillage pendant une brève période lorsque le signal dentrée dhorloge passe de bas à haut ou de haut à bas . Le détecteur de pouls est cla

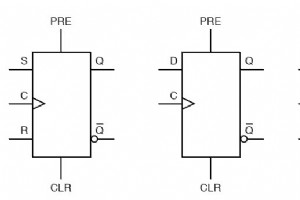

Les entrées de données normales vers une bascule (D, S et R, ou J et K) sont appelées entrées synchrones car elles nont deffet sur les sorties (Q et non-Q) quen pas, ou en synchronisation, avec les transitions du signal dhorloge. Ces entrées supplémentaires que je porte maintenant à votre attention

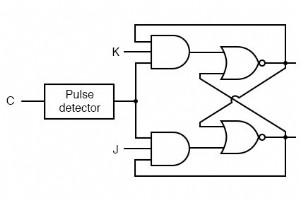

Une autre variation sur un thème de multivibrateurs bistables est la bascule J-K. Il sagit essentiellement dune version modifiée dune bascule S-R sans état de sortie « invalide » ou « illégal ». Regardez attentivement le diagramme suivant pour voir comment cela est accompli : Les entrées J et

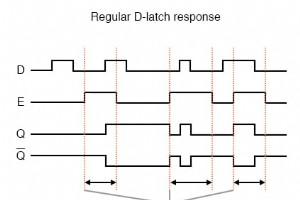

Jusquà présent, nous avons étudié les circuits de verrouillage S-R et D avec entrées dactivation. La bascule ne répond aux entrées de données (S-R ou D) que lorsque lentrée dactivation est activée. Dans de nombreuses applications numériques, cependant, il est souhaitable de limiter la réactivité dun

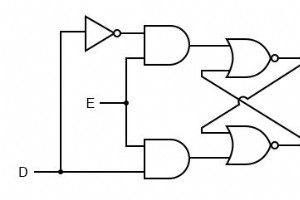

Étant donné que lentrée dactivation sur une bascule SR fermée fournit un moyen de verrouiller les sorties Q et non-Q sans tenir compte de létat de S ou R, nous pouvons éliminer lune de ces entrées pour créer un circuit de verrouillage multivibrateur sans entrée « illégale ». états. Un tel circuit e

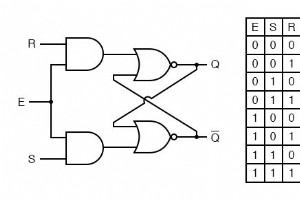

Il est parfois utile dans les circuits logiques davoir un multivibrateur qui ne change détat que lorsque certaines conditions sont remplies, quels que soient ses états dentrée S et R. Lentrée conditionnelle est appelée enable , et est symbolisé par la lettre E. Étudiez lexemple suivant pour voir co

Technologie industrielle