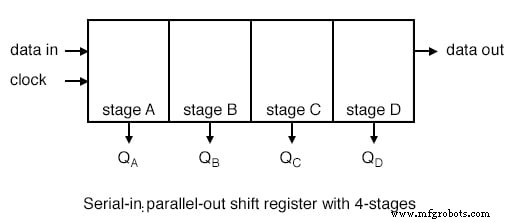

Registres à décalage :conversion d'entrée série et sortie parallèle (SIPO)

Un registre à décalage d'entrée série et de sortie parallèle est similaire au registre à décalage d'entrée série et de sortie série en ce sens qu'il transfère les données dans des éléments de stockage internes et décale les données au niveau de la sortie série, de la sortie des données, de la broche.

Il est différent en ce sens qu'il met à disposition en sorties tous les étages internes. Par conséquent, un registre à décalage à entrée série et sortie parallèle convertit les données du format série au format parallèle.

Un exemple d'utilisation d'un registre à décalage d'entrée série et de sortie parallèle

Si quatre bits de données sont décalés de quatre impulsions d'horloge via un seul fil à l'entrée de données, ci-dessous, les données deviennent disponibles simultanément sur les quatre sorties QA à QD après la quatrième impulsion d'horloge.

L'application pratique du registre à décalage à entrée série et sortie parallèle consiste à convertir les données du format série sur un seul fil au format parallèle sur plusieurs fils.

Allumons quatre LED (diodes électroluminescentes) avec les quatre sorties (QA QB QC QD ).

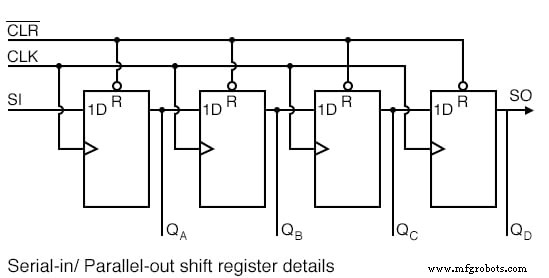

Les détails ci-dessus du registre à décalage à entrée série et sortie parallèle sont assez simples. Il ressemble à un registre à décalage d'entrée et de sortie série avec des prises ajoutées à chaque sortie d'étage.

Les données série sont transférées à SI (Entrée série). Après un nombre d'horloges égal au nombre d'étages, le premier bit de donnée apparaît en SO (QD ) dans la figure ci-dessus.

En général, il n'y a pas de broche SO. La dernière étape (QD ci-dessus) sert de SO et est cascadé au prochain package s'il existe.

Entrée série, sortie parallèle vs. entrée série, sortie série Shift Register

Si un registre à décalage à entrée série et sortie parallèle est si similaire à un registre à décalage à entrée série et sortie série, pourquoi les fabricants s'embêtent-ils à proposer les deux types ?

Pourquoi ne pas simplement proposer le registre à décalage à entrée série et sortie parallèle ?

La réponse est qu'ils n'offrent en fait que le registre à décalage d'entrée série et de sortie parallèle, tant qu'il n'a pas plus de 8 bits.

Notez que les registres à décalage d'entrée et de sortie série ont des longueurs supérieures à 8 bits, de 18 à 64 bits.

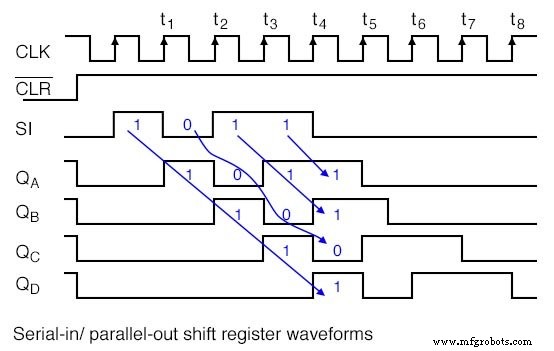

Il n'est pas pratique d'offrir un registre à décalage à entrée série et sortie parallèle 64 bits nécessitant autant de broches de sortie. Voir les formes d'onde ci-dessous pour le registre à décalage ci-dessus.

Le registre à décalage a été effacé avant toute donnée par CLR' , un signal bas actif, qui efface toutes les bascules de type D dans le registre à décalage.

Notez les données de série 1011 patron présenté au SI saisir. Ces données sont synchronisées avec l'horloge CLK .

Ce serait le cas s'il était déplacé à partir de quelque chose comme un autre registre à décalage, par exemple, un registre à décalage à entrée parallèle et sortie série (non illustré ici).

Sur la première horloge à t1 , les données 1 au SI est décalé de D à Q du premier étage de registre à décalage. Après t2 ce premier bit de données est à QB .

Après t3 c'est à QC . Après t4 c'est à QD . Quatre impulsions d'horloge ont déplacé le premier bit de données jusqu'au dernier étage QD .

Le deuxième bit de données a 0 est à QC après la 4ème horloge. Le troisième bit de données a 1 est à QB . La quatrième donnée bit un autre 1 est à QA .

Ainsi, le modèle d'entrée de données série 1011 est contenu dans (QD QC QB QR ). Il est désormais disponible sur les quatre sorties.

Il sera disponible sur les quatre sorties juste après l'horloge t4 juste avant t5 .

Ces données parallèles doivent être utilisées ou stockées entre ces deux moments, ou elles seront perdues en raison du décalage du QD étape sur les horloges suivantes t5 à t8 comme indiqué ci-dessus.

Périphériques à entrée série et sortie parallèle

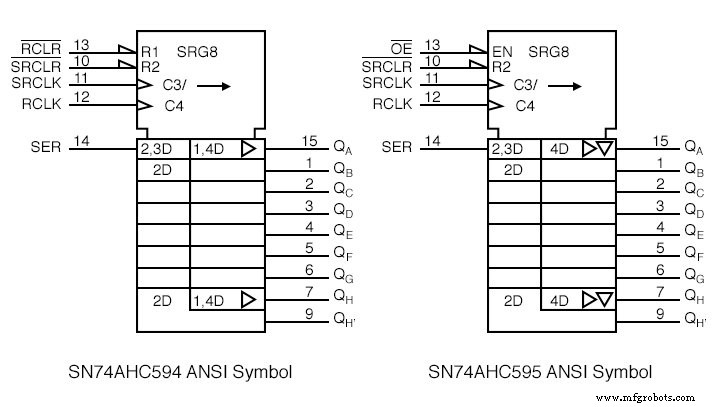

Examinons de plus près les registres à décalage d'entrée série et de sortie parallèle disponibles sous forme de circuits intégrés, avec l'aimable autorisation de Texas Instruments.

Pour les fiches techniques complètes des appareils, suivez les liens.

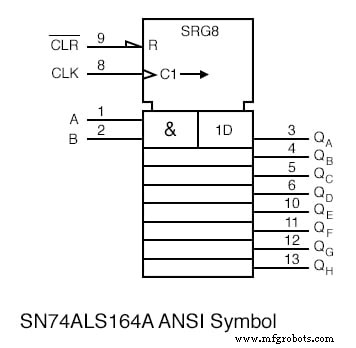

- SN74ALS164A registre à décalage 8 bits entrée/sortie parallèle

- SN74AHC594 registre à décalage 8 bits entrée/sortie parallèle avec registre de sortie

- SN74AHC595 registre à décalage 8 bits entrée/sortie parallèle avec registre de sortie

- CD4094 registre à décalage 8 bits entrée série/sortie parallèle avec registre de sortie

Le 74ALS164A est presque identique à notre schéma précédent à l'exception des deux entrées série A et B .

L'entrée inutilisée doit être tirée vers le haut pour activer l'autre entrée. Nous ne montrons pas toutes les étapes ci-dessus.

Cependant, toutes les sorties sont indiquées sur le symbole ANSI ci-dessous, avec les numéros de broche.

Le CLK l'entrée dans la section de contrôle du symbole ANSI ci-dessus a deux fonctions internes C1 , contrôle de tout ce dont le préfixe est 1 .

Ce serait le pointage des données à 1D . La deuxième fonction, la flèche après la barre oblique (/) est le décalage vers la droite (vers le bas) des données dans le registre à décalage.

Les huit sorties sont disponibles à droite des huit registres sous la section de contrôle. Le premier étage est plus large que les autres pour accueillir le A&B saisie.

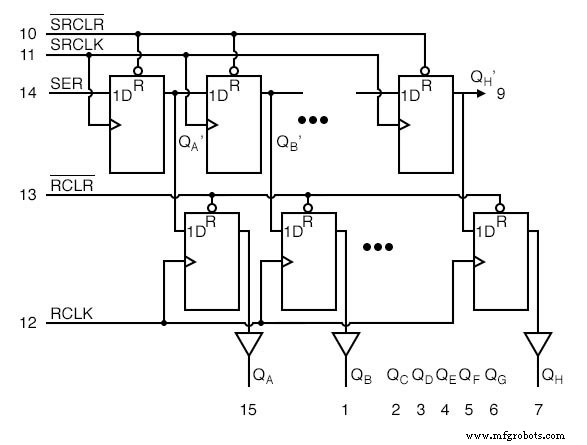

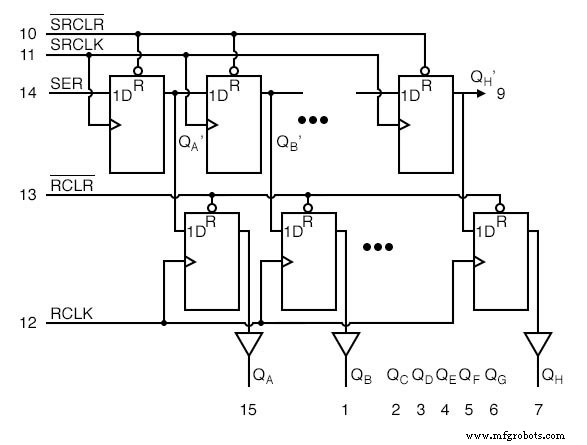

Le schéma logique interne ci-dessus est adapté de la fiche technique TI (Texas Instruments) du 74AHC594. Les FF de type « D » dans la rangée supérieure comprennent un registre à décalage à entrée série et sortie parallèle.

Cette section fonctionne comme les appareils décrits précédemment. Les sorties (QA ' QB ' à QH ' ) de la moitié du registre à décalage de l'appareil alimentent en parallèle les FF de type « D » dans la moitié inférieure. QH ' (broche 9) est déplacé vers n'importe quel package de périphérique en cascade en option.

Un seul front d'horloge positif à RCLK transférera les données de D à Q des FF inférieurs. Tous les 8 bits sont transférés en parallèle vers le registre de sortie (une collection d'éléments de stockage).

Le but du registre de sortie est de maintenir une sortie de données constante pendant que de nouvelles données sont déplacées dans la section supérieure du registre à décalage.

Ceci est nécessaire si les sorties pilotent des relais, des vannes, des moteurs, des solénoïdes, des avertisseurs sonores ou des avertisseurs sonores. Cette fonction peut ne pas être nécessaire lors de la conduite de LED tant que le scintillement pendant le changement de vitesse n'est pas un problème.

Notez que le 74AHC594 a des horloges séparées pour le registre à décalage (SRCLK ) et le registre de sortie ( RCLK ). De plus, le levier de vitesses peut être effacé par SRCLR et, le registre de sortie par RCLR .

Il est souhaitable de mettre les sorties dans un état connu à la mise sous tension, en particulier si vous commandez des relais, des moteurs, etc. Les formes d'onde ci-dessous illustrent le décalage et le verrouillage des données.

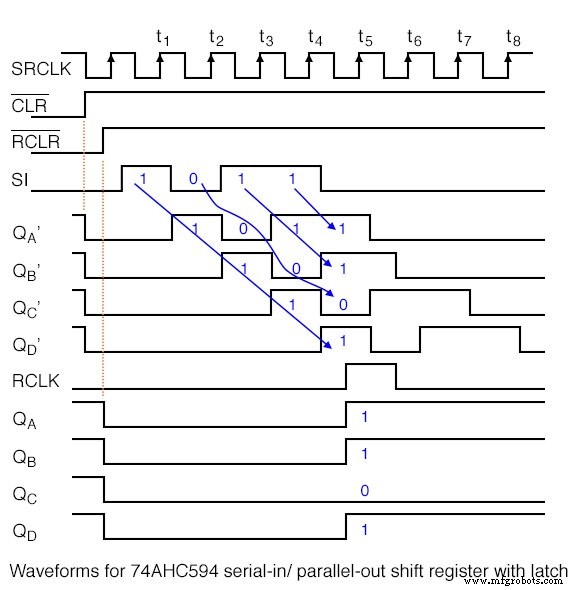

Les formes d'onde ci-dessus montrent le décalage de 4 bits de données dans les quatre premiers étages de 74AHC594, puis le transfert parallèle vers le registre de sortie.

En réalité, le 74AHC594 est un registre à décalage de 8 bits, et il faudrait 8 horloges pour décaler 8 bits de données, ce qui serait le mode de fonctionnement normal.

Cependant, les 4 bits que nous montrons permettent d'économiser de l'espace et illustrent adéquatement l'opération.

On efface le registre à décalage une demi-horloge avant t0 avec SRCLR’=0 . SRCLR' doit être relâché haut avant de changer de vitesse.

Juste avant t0 le registre de sortie est effacé par RCLR'=0 . Elle aussi est publiée ( RCLR’=1 ).

Données de série 1011 est présenté à la broche SI entre les horloges t0 et t4 . Il est décalé par les horloges t1 t2 t3 t4 apparaissant aux étapes de changement interne QA ' QB ' QC ' QD ' .

Ces données sont présentes à ces étapes entre t4 et t5 . Après t5 les données souhaitées (1011 ) ne sera pas disponible sur ces étages de changement de vitesse internes.

Entre t4 et t5 nous appliquons une approche positive RCLK transfert de données 1011 pour enregistrer les sorties QA QB QC QD .

Ces données seront gelées ici en tant que données supplémentaires (0 s) se déplace au cours de la SRCLK suivante s (t5 à t8 ). Il n'y aura pas de changement de données ici jusqu'à un autre RCLK est appliqué.

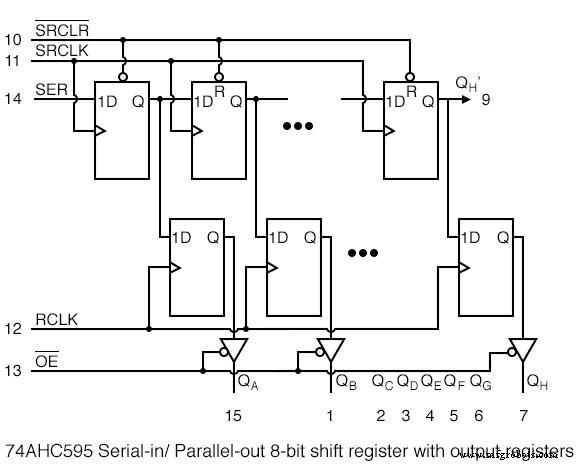

Le 74AHC595 est identique au ‘594 sauf que le RCLR’ est remplacé par un OE’ activation d'un tampon à trois états à la sortie de chacun des huit bits du registre de sortie.

Bien que le registre de sortie ne puisse pas être effacé, les sorties peuvent être déconnectées par OE'=1 .

Cela permettrait aux résistances pull-up ou pull-down externes de forcer tout relais, solénoïde ou pilote de vanne à un état connu lors d'une mise sous tension du système.

Une fois que le système est sous tension et, disons, qu'un microprocesseur a déplacé et verrouillé les données dans le '595, l'activation de la sortie peut être affirmée (OE'=0 ) pour piloter les relais, les solénoïdes et les vannes avec des données valides, mais pas avant.

Ci-dessus se trouvent les symboles ANSI proposés pour ces appareils. C3 synchronise les données dans l'entrée série (SER externe ) comme indiqué par le 3 préfixe de 2,3D .

La flèche après C3/ indique le décalage vers la droite (vers le bas) du registre à décalage, les 8 étapes à gauche du symbole « 595 sous la section de contrôle.

Les 2 préfixe de 2,3D et 2D indique que ces étapes peuvent être réinitialisées par R2 (externe SRCLR’ ).

Le 1 préfixe de 1,4D sur le '594 indique que R1 (externe RCLR’ ) peut réinitialiser le registre de sortie, qui se trouve à droite de la section du registre à décalage.

Le '595 , qui a un EN à l'OE’ externe ne peut pas réinitialiser le registre de sortie. Mais, le FR active les tampons de sortie à trois états (triangle inversé).

Le triangle pointant vers la droite des deux '594 et'595 indique la mise en mémoire tampon interne. Tant le '594 et'595 les registres de sortie sont cadencés par C4 comme indiqué par 4 de 1,4D et 4D respectivement.

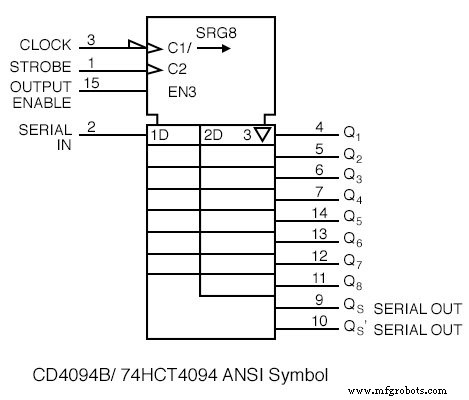

Le CD4094B est un 3 à 15VDC alternative de registre à décalage à verrouillage capable aux précédents dispositifs 74AHC594.

HORLOGE , C 1, transfère les données à SERIAL IN comme l'implique le 1 préfixe de 1D .

C'est aussi l'horloge du registre à décalage droit (moitié gauche du corps du symbole) comme indiqué par le /(flèche droite) de C1 /(flèche) à l'HORLOGE saisie.

STROBOSCOPIQUE , C2 est l'horloge du registre de sortie 8 bits à droite du corps du symbole. Les 2 de 2D indique que C2 est l'horloge du registre de sortie.

Le triangle inversé dans le loquet de sortie indique que la sortie est tristatée, étant activée par EN3 .

Les 3 précédant le triangle inversé et le 3 de EN3 sont souvent omis, car tout activer (FR ) est compris pour contrôler les sorties à trois états. QS et QS ' sont des sorties non verrouillées de l'étage de registre à décalage.

QS peut être cascadé sur SERIAL IN d'un appareil suivant.

Applications pratiques

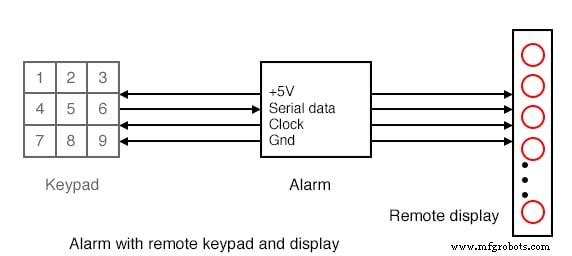

Une application réelle du registre à décalage à entrée série et sortie parallèle consiste à sortir des données d'un microprocesseur vers un indicateur de panneau distant.

Ou, un autre périphérique de sortie distant qui accepte les données au format série.

La figure « Alarme avec clavier à distance » est répétée ici à partir de la section entrée parallèle, sortie série avec l'ajout de l'affichage à distance.

Ainsi, on peut afficher, par exemple, l'état des boucles d'alarme connectées au boîtier d'alarme principal.

Si l'alarme détecte une fenêtre ouverte, elle peut envoyer des données série à l'affichage à distance pour nous en informer.

Le clavier et l'affichage seraient probablement contenus dans le même boîtier distant, séparé du boîtier d'alarme principal. Cependant, nous ne regarderons que le panneau d'affichage dans cette section.

Si l'affichage était sur la même carte que l'alarme, nous pourrions simplement faire passer huit fils aux huit LED avec deux fils pour l'alimentation et la terre.

Ces huit fils sont beaucoup moins souhaitables à long terme pour un panneau distant. En utilisant des registres à décalage, nous n'avons besoin que de cinq fils d'horloge, des données série, un stroboscope, l'alimentation et la terre.

Si le panneau n'était qu'à quelques centimètres de la carte principale, il pourrait toujours être souhaitable de réduire le nombre de fils dans un câble de connexion pour améliorer la fiabilité.

De plus, nous utilisons parfois la plupart des broches disponibles sur un microprocesseur et devons utiliser des techniques série pour augmenter le nombre de sorties.

Certains périphériques de sortie de circuits intégrés, tels que les convertisseurs numérique-analogique, contiennent des registres à décalage à entrée série et sortie parallèle pour recevoir les données des microprocesseurs.

Les techniques illustrées ici sont applicables à ces pièces.

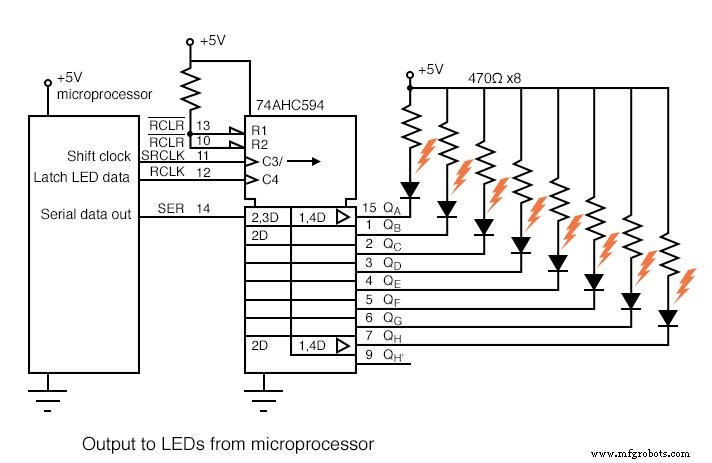

Nous avons choisi le registre à décalage à entrée série et sortie parallèle 74AHC594 avec registre de sortie; cependant, cela nécessite une broche supplémentaire, RCLK , pour charger en parallèle les données transférées sur les broches de sortie.

Cette broche supplémentaire empêche les sorties de changer pendant que les données se déplacent. Ce n'est pas vraiment un problème pour les LED. Mais, ce serait un problème si vous conduisez des relais, des vannes, des moteurs, etc.

Le code exécuté dans le microprocesseur commencerait par 8 bits de données à sortir. Un bit serait sorti sur la broche "Sortie de données série", entraînant SER de la télécommande 74AHC594.

Ensuite, le microprocesseur génère une transition de bas en haut sur "Shift clock", entraînant SRCLK du registre à décalage ‘595.

Cette horloge positive décale le bit de données à SER de « D » à « Q » du premier étage de registre à décalage.

Cela n'a aucun effet sur le QA LED à ce moment en raison du registre de sortie interne de 8 bits entre le registre à décalage et les broches de sortie (QA à QH ).

Enfin, "Shift clock" est ramené à un niveau bas par le microprocesseur. Ceci termine le décalage d'un bit dans le « 595.

La procédure ci-dessus est répétée sept fois de plus pour terminer le décalage de 8 bits de données du microprocesseur dans le registre à décalage à entrée série et sortie parallèle 74AHC594.

Pour transférer les 8 bits de données dans le registre à décalage interne '595 vers la sortie, le microprocesseur doit générer une transition de bas en haut sur RCLK , l'horloge du registre de sortie.

Cela applique de nouvelles données aux LED. Le RCLK doit être ramené à un niveau bas en prévision du prochain transfert de données 8 bits.

Les données présentes à la sortie du '595 resteront jusqu'à ce que le processus des deux paragraphes ci-dessus soit répété pour un nouveau 8 bits de données.

En particulier, de nouvelles données peuvent être déplacées dans le registre à décalage interne '595 sans affecter les LED. Les LED ne seront mises à jour avec de nouvelles données qu'avec l'application du RCLK front montant.

Et si nous avons besoin de piloter plus de huit LED ? Cascadez simplement un autre 74AHC594 SER épingler au QH ' du levier de vitesses existant.

Parallèlement à la SRCLK et RCLK épingles. Le microprocesseur aurait besoin de transférer 16 bits de données avec 16 horloges avant de générer un RCLK alimenter les deux appareils.

Les indicateurs LED discrets, que nous montrons, pourraient être des LED à 7 segments. Cependant, il existe des appareils LSI (Large Scale Integration) capables de piloter plusieurs chiffres à 7 segments.

Cet appareil accepte les données d'un microprocesseur dans un format série, entraînant plus de segments de LED qu'il n'a de broches en multiplexant les LED.

FICHES DE TRAVAIL CONNEXES :

- Feuille de travail des registres à décalage

Technologie industrielle

- Déphasage

- Conversion octale et hexadécimale en décimal

- Conversion à partir de la numération décimale

- Conversion de types C#

- La pandémie accélère le passage à l'impression 3D

- C# - Conversion de types

- Revêtement de conversion de film chimique pour tôle

- Conversion étoile à delta et delta à étoile. Transformation Y-Δ

- Qu'est-ce que le revêtement de passivation et de conversion | CNCLATHING Services de finition de surface