Transistors à effet de champ InSe bidimensionnels hautes performances avec un nouveau contact ohmique en sandwich pour les nœuds inférieurs à 10 nm :une étude théorique

Résumé

Le transistor à effet de champ (FET) bidimensionnel (2D) basé sur InSe a montré une mobilité de porteur remarquable et un rapport marche-arrêt élevé dans les rapports expérimentaux. Les études théoriques ont également indiqué que les hautes performances peuvent être bien préservées aux nœuds inférieurs à 10 nm dans la limite balistique. Cependant, l'expérience expérimentale et les calculs théoriques ont montré que l'obtention d'une résistance ohmique de haute qualité est devenue le principal facteur limitant du FET 2D hautes performances. Dans ce travail, nous avons proposé un nouveau contact ohmique en sandwich avec de l'indium pour InSe FET et évalué de manière exhaustive ses performances à partir de vues du matériau et du dispositif basées sur des méthodes ab initio. Les propriétés du matériau indiquent que tous les problèmes fondamentaux du contact ohmique, y compris la barrière tunnel, la barrière Schottky et le dopage efficace, sont bien concernés par l'introduction de la structure en sandwich, et une excellente résistance de contact a été obtenue. Au niveau des performances de l'appareil, des appareils avec une longueur de grille de 7, 5 et 3 nm ont été étudiés. Toutes les mesures des dispositifs à contact pris en sandwich dépassent de loin les exigences de la feuille de route technologique internationale pour les semi-conducteurs (ITRS) et présentent une promotion évidente par rapport aux structures conventionnelles. Une augmentation maximale du courant avec 69,4 %, 50 % et 49 % est obtenue pour les appareils avec une longueur de grille de 7, 5 et 3 nm, respectivement. Pendant ce temps, une réduction maximale du retard intrinsèque avec 20,4 %, 16,7 % et 18,9 % est atteinte. De plus, une référence du produit de retard d'énergie (EDP) par rapport à d'autres FET 2D est présentée. Tous les FET InSe avec contact ohmique en sandwich surpassent MoS2 FET ainsi que les exigences de l'ITRS 2024. Le meilleur résultat approche la limite supérieure du FET BP idéal, dénotant une prépondérance supérieure des structures en sandwich pour les FET InSe dans la prochaine génération de technologie de semi-conducteurs à oxyde métallique complémentaire (CMOS).

Introduction

Les semi-conducteurs bidimensionnels (2D) ont suscité un grand intérêt pour les dispositifs électroniques en raison de leurs applications attrayantes pour la prochaine génération de la technologie des semi-conducteurs à oxyde métallique complémentaire (CMOS) [1, 2]. Leur épaisseur ultra-mince et leur bonne propriété diélectrique peuvent fournir un excellent contrôle de grille électrostatique pour supprimer les effets de canal court bien connus [3]. De plus, comme peu de couches de matériaux 2D possèdent généralement une surface lisse avec un manque de liaisons pendantes, la mobilité des porteurs de supériorité des matériaux 2D peut être bien préservée dans les systèmes de corps ultrafins par rapport aux semi-conducteurs conventionnels [4]. À l'exception du graphène sans espace, la plupart des semi-conducteurs 2D synthétisés comme les dichalcogénures de métaux de transition (TMD), le phosphore noir (BP) et le séléniure d'indium (InSe) possèdent une bande interdite nulle et se sont avérés adaptés aux transistors à effet de champ (FET ). Les FET basés sur les TMD ont montré un rapport on-off élevé allant jusqu'à 10 8 et un faible courant de fuite dans les dispositifs à canaux courts, bénéficiant de la masse effective élevée [5]. Les FET basés sur BP ont présenté des caractéristiques de courant et de commutation exceptionnelles [6], en raison de la grande mobilité de ~ 1000 cm 2 /V s et propriété de transport anisotrope [7]. Récemment, il a été démontré que l'InSe présentait une mobilité de supériorité de ~ 2000 cm 2 /V s à température ambiante [8, 9], et FET basé sur InSe a révélé un rapport marche-arrêt élevé de 10 8 [dix]. Les calculs du premier principe ont également identifié que le FET InSe peut être bien réduit à moins de 10 nm dans la limite balistique [11, 12]. Cependant, en raison de la négligence de la résistance de contact et de l'hypothèse d'un fort dopage, l'approche de la limite théorique reste un défi dans les applications réelles. En fait, comme une méthode de dopage fiable et un moyen d'obtenir un contact ohmique de haute qualité font toujours défaut, les FET basés sur des matériaux 2D, y compris l'InSe, sont généralement des FET à barrière Schottky (SB) [13,14,15,16]. Le SB au niveau des régions actives donne une grande résistance de contact et un faible niveau de dopage dégrade davantage la densité de courant. Atteindre une faible résistance de contact avec des régions actives suffisamment dopées est devenu le principal facteur limitant pour le FET à base de matériaux 2D (FET 2D) pour atteindre des performances élevées [17,18,19].

Visant les problèmes ci-dessus, nous avons proposé un nouveau contact ohmique en sandwich pour InSe FET. L'indium a été choisi comme métal d'électrode, car des études expérimentales et théoriques récentes suggèrent que l'indium peut être un candidat prometteur pour l'InSe FET pour obtenir de bonnes performances [20,21,22]. Nous avons évalué théoriquement la qualité de contact ohmique et les performances des dispositifs avec une longueur de grille de 7, 5 et 3 nm suivant le cadre de l'International Technology Roadmap for Semiconductors 2013 (ITRS) [23]. Il convient de noter que bien que l'ITRS ait été remplacé par l'International Roadmap for Devices and Systems (IRDS) [24], l'ITRS2013 présente une tendance de mise à l'échelle claire pour les transistors et a toujours été adopté dans des études récentes [25, 26]. Ce manuscrit est organisé comme suit :tout d'abord, les propriétés électriques des contacts pris en sandwich et conventionnels (en haut) sont étudiées. Deuxièmement, les mesures de performance des appareils telles que le courant à l'état passant et le retard intrinsèque sont évaluées et comparées aux exigences de l'ITRS. Enfin, la référence du produit de retard de puissance par rapport au retard intrinsèque est présentée pour comparer avec d'autres dispositifs basés sur des matériaux 2D.

Méthodes

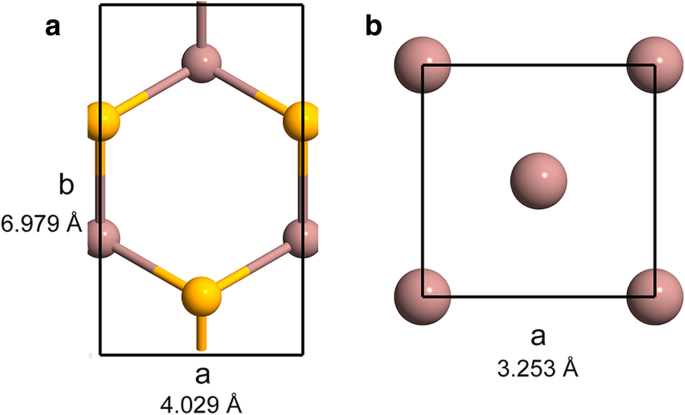

Toutes les structures atomiques ont été optimisées par VASP [27]; Une coupure d'énergie de 335 eV a été utilisée pendant tous les calculs. La cellule unitaire de l'InSe a été relâchée avec un critère de contrainte de 0,01 eV/Å dans le cadre du MetaGGA du SCAN [28]. Les paramètres de réseau de l'indium métallique ont été obtenus à partir du manuel de chimie et de physique [29]. Comme le montre la figure 1, la constante de réseau de l'InSe est de 4,029 , ce qui est en très bon accord avec les rapports expérimentaux [30, 31].

Vue de dessus de la maille élémentaire de l'InSe (a ) et l'indium (b ), respectivement

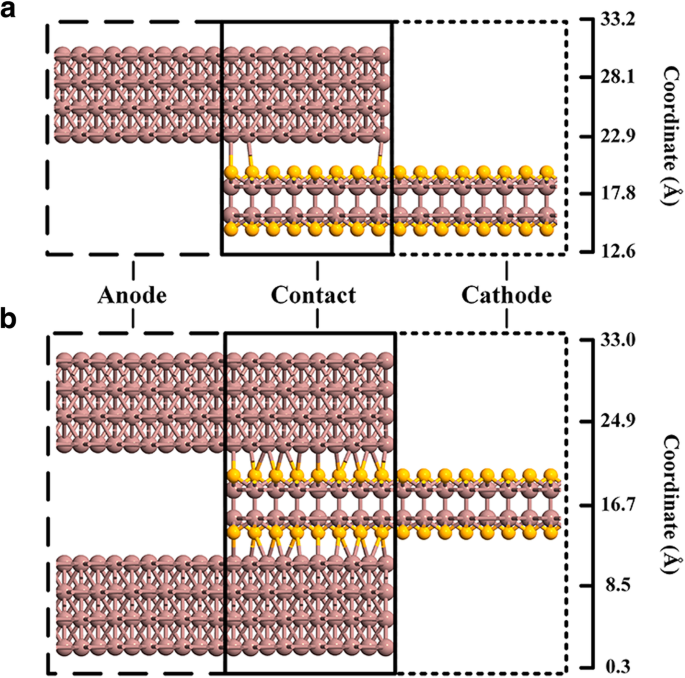

La structure initiale de l'indium sur InSe a été construite avec 4 × 1 × 1 et 5 × 2 × 1 cellules unitaires de surface d'InSe et d'indium (001), respectivement. La déformation absolue moyenne était de 1,32%, ce qui est suffisant pour préserver les propriétés intrinsèques du matériau. Comme le montrent les figures 2a, b, la structure en sandwich a été construite avec des couches d'indium/InSe/indium, l'indium des côtés inférieur et supérieur a une symétrie miroir avec le centre de l'InSe. Les deux structures hybrides ont été relaxées avec la fonctionnelle de van der Waals (vdW) d'optb88 avec un critère de force sur chaque atome inférieur à 0,02 eV/Å [32, 33]. La surface de contact finale est de 16,19 × 6,41 . La résistance du contact ohmique a ensuite été évaluée par un dispositif à deux sondes comme le montre la figure 2a, b. Éliminant la résistance inutile du semi-conducteur hors des régions de contact, l'InSe dans la cathode était fortement dopé avec 1 × 10 14 e/cm 2 pour les contacts supérieurs et pris en sandwich.

Structures atomiques de contact et dispositif à deux sondes associé utilisés pour l'évaluation de la résistance de contact. un , b sont pour les contacts supérieurs et pris en sandwich, respectivement. Les coordonnées indiquent l'emplacement des atomes dans la direction hors du plan

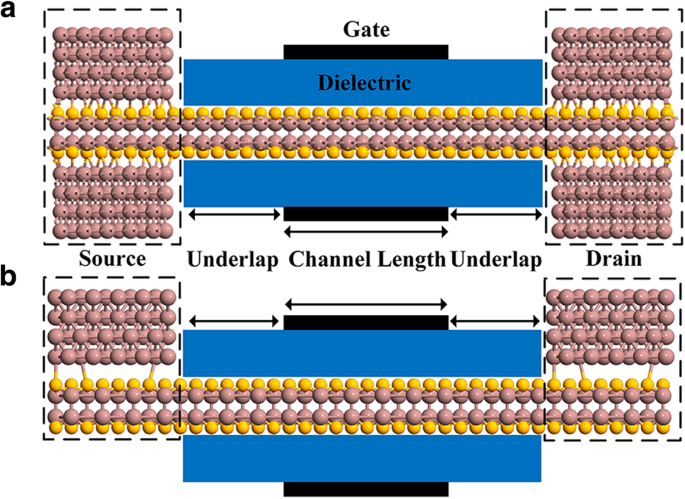

En ce qui concerne l'évaluation des performances du dispositif, la géométrie du FET InSe avec des contacts ohmiques pris en sandwich et supérieur est illustrée aux figures 3a, b, respectivement. Tous les noms de périphériques et de nœuds suivent les exigences de l'ITRS et de l'IRDS, respectivement. Les paramètres de l'appareil sont répertoriés dans le tableau 1. Pour supprimer l'effet tunnel intrabande, 1 nm de sous-couche (UL) a été appliqué à une longueur de grille de 3 nm. Contrairement à la modélisation de contact ohmique, aucune des pièces des dispositifs n'a été dopée intentionnellement. Les dispositifs ont été construits en fusionnant la source, le drain et le canal dans le sens du transport. Le canal et ses deux interfaces avec les régions actives ont en outre été relaxés avec une source et un drain fixes. Toutes les simulations étaient basées sur la théorie de la fonction de Green hors équilibre (NEGF) et réalisées par QuantumATK avec un calcul entièrement cohérent [34,35,36], qui était généralement utilisé pour concevoir et étudier des transistors à des nœuds inférieurs à 10 nm [17 , 37,38,39]. Un ensemble de base polarisé double zêta a été utilisé avec une coupure mécanique de 90 Rydberg. Le maillage de points k du pack de Monkhorst a été échantillonné avec une densité de 8/Å −1 × 11/Å −1 × 180/Å −1 . Le solveur de gradient conjugué parallèle est choisi comme solveur de Poisson pour des raisons d'efficacité. Le courant de tous les appareils peut alors être obtenu en résolvant la formule de Landauer-Büttiker [40] :

$$ I\left({V}_{\mathrm{Bias}}\right)=\frac{2e}{h}\int T\left(E,{V}_L,{V}_R\right)\ left[{f}_{\mathrm{R}}\left(E,{V}_R\right)-{f}_L\left(E,{V}_L\right)\right] dE $$

Géométries des FET InSe avec sandwich (a ) et en haut (b ) contacts

Où,V Biais est le biais et peut être obtenu par :V Biais = V R ‐ V L , T (E , V L , V R ) est le coefficient de transmission des porteuses, f R (E , V R ) et f L (E , V L ) sont la fonction de distribution de Fermi-Dirac pour la cathode (drain) et l'anode (source), respectivement.

Résultats et discussion

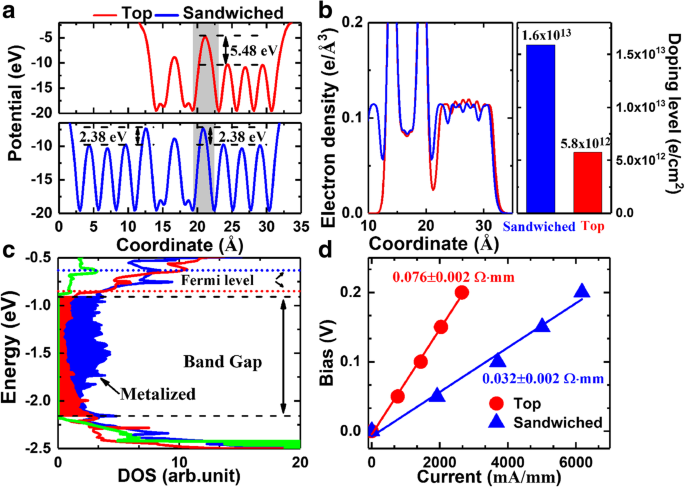

En général, il existe trois facteurs clés corrélés à la qualité de contact ohmique dans les matériaux 2D [18], à savoir la barrière tunnel et la distance qui est dérivée de l'écart vdW, du chevauchement orbital entre l'électrode et le semi-conducteur, ainsi que la hauteur SB. Tout d'abord, la barrière tunnel et la distance ont été décrites par le potentiel effectif représenté sur la figure 4a. Par rapport au contact supérieur, l'introduction d'un contact en sandwich fournit non seulement un chemin de transport supplémentaire sur le côté inférieur, mais entraîne également une diminution de la barrière tunnel de 5,48 à 2,38 eV, entraînant une réduction de 56,6 %. Pendant ce temps, la distance interfaciale est également légèrement abaissée avec 0,66 , ce qui indique que la largeur de la barrière tunnel est également réduite. Deuxièmement, le chevauchement orbital peut être évalué à partir de la distribution des charges de cantonnière sur la figure 4b. On peut remarquer que le contact pris en sandwich possède plus d'électrons de cantonnière dans la région interfaciale par rapport au contact supérieur, indiquant un chevauchement orbital plus fort entre l'indium et l'InSe. Cette fonctionnalité permet également d'introduire un effet de dopage dans l'InSe, et le nombre d'électrons en excès peut être calculé en utilisant la population Mulliken. Nous avons extrait le nombre total d'électrons dans l'InSe des structures en sandwich et en contact supérieur, respectivement. Ensuite, le niveau de dopage peut être obtenu en divisant le nombre d'électrons par la surface de la région de contact, car la charge nette d'InSe isolé doit toujours être nulle. Comme le montre le panneau de droite de la figure 4b, le contact pris en sandwich donne un niveau de dopage très élevé de 1,6 × 10 13 e/cm 2 , ce qui est près de 2,8 fois supérieur à celui du contact supérieur. Un niveau aussi élevé a approché l'hypothèse dans les simulations du FET à effet tunnel 2D, qui revendique généralement un niveau de dopage beaucoup plus élevé que le FET métal-oxyde-semi-conducteur. Troisièmement, la densité d'états (DOS) de l'InSe dans des structures vierges, en sandwich et en contact supérieur est illustrée à la figure 4c. Le chevauchement orbital entre l'indium et l'InSe au niveau de la région interfaciale a métallisé la bande interdite de l'InSe, et une prise en sandwich donne un niveau plus élevé. Cette caractéristique améliore considérablement l'injection de porteurs à travers la barrière à effet tunnel vdW au niveau de la région interfaciale, car les états métallisés dans la bande interdite offrent des canaux à effet tunnel supplémentaires. De plus, les niveaux de Fermi sont pincés au-dessus du minimum de la bande de conduction, ce qui entraîne une dégénérescence énergétique d'environ 0,07 et 0,27 eV pour les contacts supérieurs et en sandwich, respectivement. Par conséquent, les SB entre l'indium et l'InSe sont complètement éliminés. Quatrièmement, la résistance de contact ohmique a été calculée sur la base de la courbe de courant de polarisation obtenue à partir des dispositifs à deux sondes, et tous les résultats sont présentés sur la figure 4d. On peut remarquer que les deux contacts sont ohmiques du fait des évolutions linéaires. Au niveau théorique, c'est-à-dire en négligeant la rugosité de surface, les impuretés interfaciales, etc., la structure en sandwich conduit à une valeur de contact très faible de 0,032 ± 0,002 Ω mm, ce qui réduit de plus de la moitié la résistance du contact supérieur. Sur la base des discussions ci-dessus, il est intéressant de noter que le double de la région de contact conduit toujours à une amélioration de plus du double du contact ohmique. Étant donné que le contact supérieur avec l'indium a été récemment confirmé expérimentalement comme étant efficace pour améliorer les performances des dispositifs à base d'InSe [21, 22], la structure en sandwich peut être une solution de contact ohmique attrayante pour les FET InSe.

un Potentiel effectif normal au sens de transport. La coordonnée correspond à l'emplacement des atomes et est définie sur la figure 1. Les régions sombres correspondent à l'espace vdW. b Distribution électronique moyenne dans le plan normale à la direction de transport. Le panneau de droite est le niveau de dopage. La coordonnée correspond à l'emplacement des atomes et est définie sur la figure 1. c DOS de l'InSe. Le vert correspond à l'InSe vierge. d Biais dépendant du courant des deux dispositifs de sonde. Tous les rouges et bleus correspondent respectivement aux contacts supérieurs et pris en sandwich

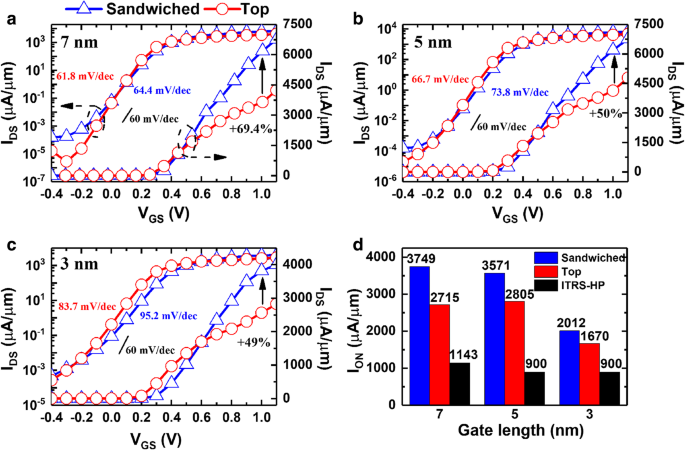

Ensuite, les performances de l'appareil ont été évaluées et les caractéristiques de transfert des nœuds InSe FET à 2019, 2021 et 2024 ont été présentées sur la Fig. 5. On peut observer que l'oscillation sous le seuil (SS) de tous les nœuds est inférieure à 100 mV/déc. , et SS au nœud 2019 présente des caractéristiques de commutation presque idéales de 61,8 et 64,4 mV/déc pour les dispositifs à contact supérieur et pris en sandwich, respectivement, indiquant un contrôle électrostatique exceptionnel dans les FET InSe. De plus, les dispositifs contactés en sandwich conduisent à une amélioration évidente de IDS par rapport aux premiers avec une augmentation maximale de 69,4 %, 50 % et 49 % atteinte aux nœuds 2019, 2021 et 2024, respectivement. De plus, j'ON a été extrait suite à l'exigence de haute performance (HP) dans l'ITRS. Comme le montre la figure 5d, ION de tous les systèmes est bien au-dessus de l'exigence HP. Par rapport aux appareils les plus sollicités, les systèmes en sandwich présentent toujours une promotion de 38,2 %, 27,3 % et 20,5 % pour les nœuds 2019, 2021 et 2024, respectivement.

Caractéristiques de transfert des FET InSe au niveau du nœud. un 2019, b 2021, et c 2024 nœuds, respectivement. d Comparaisons de ION suivant l'exigence HP de l'ITRS

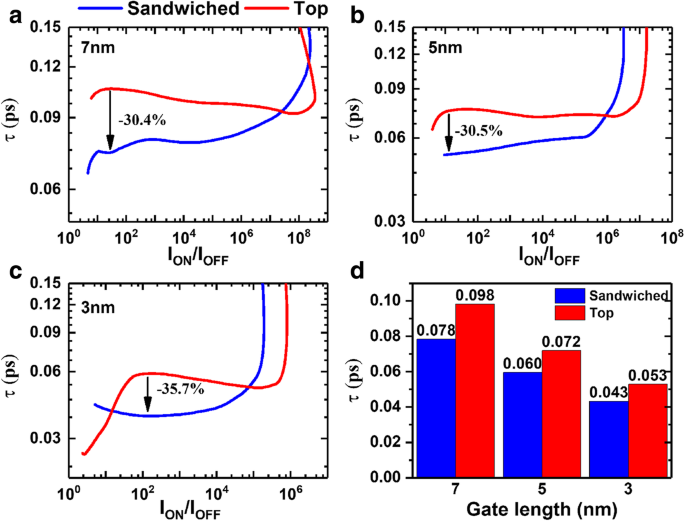

Une autre métrique essentielle du FET est le retard intrinsèque (τ), qui signifie la limite supérieure de la vitesse de commutation dans le circuit logique. Le τ a été obtenu par τ = (QON − QOFF )/ION , où QON et QOFF sont des charges aux états activé et désactivé, respectivement. Les états activé et désactivé sont limités à |VDS |=0,68, 0,64 et 0,64 V pour 2019, 2021 et 2024 nœuds, respectivement. Le retard intrinsèque en fonction du rapport marche-arrêt est illustré à la Fig. 6. Malgré l'évolution non monotone à grand retard qui est dérivée de l'effet tunnel sous de faibles tensions de grille [41], tous les retards sont inférieurs à 0,15 ps et suffisamment abaissés par rapport à l'exigence ITRS de 0,44-0,46 ps. De plus, les appareils à contact pris en sandwich donnent lieu à une réduction de plus de 30 % dans les régions de ION /IOFF ≤ 10 7 , 10 6 , 10 5 pour 2019, 2021 et 2024 nœuds, respectivement. Sur la base des exigences HP illustrées à la figure 6d, les appareils à contact pris en sandwich peuvent toujours favoriser la vitesse de commutation avec 20,4 %, 16,7 % et 18,9 % pour les nœuds 2019, 2021 et 2024, respectivement.

Retard intrinsèque en fonction du rapport marche-arrêt au nœud. un 2019, b 2021, et c 2024 nœuds, respectivement. d Comparaisons du délai intrinsèque suivant l'exigence HP de l'ITRS

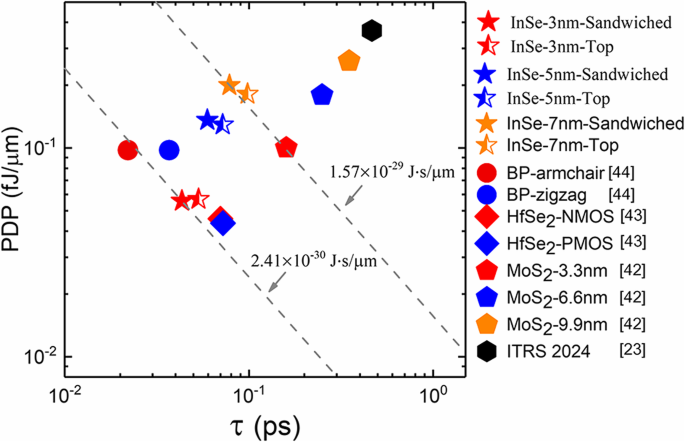

Afin d'évaluer les performances du dispositif de manière plus intuitive, le produit de retard de puissance (PDP) par rapport au retard intrinsèque est extrait. PDP correspond à la consommation d'énergie dans un événement de commutation unique et est défini par PDP = (QON − QOFF )VDS avec tous les paramètres dérivés de l'exigence HP de l'ITRS. Les résultats et la comparaison avec d'autres FET 2D sont présentés sur la figure 7. Premièrement, tous les FET 2D ont été sélectionnés sur la base de la règle selon laquelle ils ont été préalablement vérifiés en tant que transistors dans des rapports expérimentaux, ce qui va encore plus loin pour la technologie CMOS. Deuxièmement, sauf pour l'InSe et le MoS2 [42], tous les autres dispositifs ont été simulés avec un dopage important dans les régions actives et une négligence de la résistance de contact ohmique [43, 44], donc les résultats correspondent à la limite supérieure de performance. Comme on peut le voir, tous les produits à retard d'énergie (EDP) sont inférieurs aux exigences ITRS 2024, indiquant l'avenir attrayant des FET 2D. Le maximum d'EDP appartient au MoS2 FET à 9,9 nm, et le meilleur vient de BP FET. En ce qui concerne les FET InSe, les dispositifs à contact pris en sandwich fonctionnent toujours mieux que ceux à contact supérieur à tous les nœuds. L'EDP le plus élevé des dispositifs à contact pris en sandwich est à une longueur de porte de 7 nm (nœud 2019) et dépasse tous les MoS2 FET. Le plus bas a une longueur de grille de 3 nm (nœud 2024) et s'approche même de la limite supérieure du BP FET dans la direction du fauteuil, ce qui est bien connu pour ses propriétés de transport exceptionnelles. En conséquence, l'EDP du FET InSe signifie que les dispositifs à contact pris en sandwich présentent une compétitivité suffisante parmi les FET 2D.

Produit de retard de puissance par rapport au retard intrinsèque composé d'InSe et d'autres FET 2D. Les lignes directrices en pointillés gris correspondent à des EDP spécifiques

Conclusions

Dans ce travail, un nouveau contact ohmique en sandwich avec l'indium a été proposé pour InSe FET. Le contact ohmique pris en sandwich non seulement double la zone de contact, mais favorise également la qualité de contact plus de deux fois, conduisant à une excellente résistance de contact. Au niveau de performance du dispositif de longueur de grille 7, 5 et 3 nm, les FET InSe avec contact ohmique pris en sandwich présentent une promotion de performance universelle par rapport aux dispositifs conventionnels à contact supérieur. Sous l'exigence de HP de l'ITRS, le courant à l'état passant et le délai intrinsèque sont améliorés de 38,2 à 20,5 % et de 20,4 à 16,7 %, respectivement. Une référence de l'EDP par rapport à d'autres FET 2D révèle également que les FET InSe avec contact ohmique pris en sandwich présentent des avantages par rapport aux autres FET 2D. Notre étude offre une nouvelle voie vers les FET InSe haute performance.

Disponibilité des données et des matériaux

Les ensembles de données utilisés et/ou analysés au cours de la présente étude sont disponibles auprès de l'auteur correspondant sur demande raisonnable.

Abréviations

- 2D :

-

Bidimensionnel

- CMOS :

-

Semi-conducteur à oxyde métallique complémentaire

- TMD :

-

Dichalcogénures de métaux de transition

- BP :

-

Phosphore noir

- InSe :

-

Séléniure d'indium

- FET :

-

Transistors à effet de champ

- SB :

-

Barrière Schottky

- FET 2D :

-

FET basé sur les matériaux 2D

- ITRS :

-

Feuille de route technologique internationale pour les semi-conducteurs

- vdW :

-

van der Waals

- UL :

-

Sous-couche

- NEGF :

-

Fonction de non-équilibre de Green

- DOS :

-

La densité des états

- SS :

-

Balançoire sous le seuil

- HP :

-

Hautes performances

- τ :

-

Retard intrinsèque

- PDP :

-

Produit à retard de puissance

- EDP :

-

Produit à retard d'énergie

Nanomatériaux

- Espaceurs d'air pour puces 10 nm

- Nexam fournira à Diab le Nexamite améliorant les propriétés pour une mousse PET haute performance

- Fibres de carbone activées avec nanostructure hiérarchique dérivées de déchets de gants de coton en tant qu'électrodes hautes performances pour supercondensateurs

- Transistors multicouches à effet de champ SnSe Nanoflake avec contacts Au Ohmic à faible résistance

- Étude d'un nouveau système micellaire ressemblant à un ver amélioré par des nanoparticules

- Évolution de la zone de contact à charge normale pour les surfaces rugueuses :de l'échelle atomique à l'échelle macroscopique

- Dépôt en couche atomique de nano-films d'oxyde d'indium pour transistors à couche mince

- Microarrays mésoporeux VO2 bidimensionnel pour supercondensateur hautes performances

- Transistors à effet de champ ferroélectrique à base de motifs à rayures micrométriques à dominance de nanotubes de carbone à simple paroi avec couche de contrôle des défauts HfO2