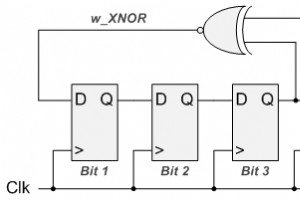

LFSR dans un FPGA – VHDL &Verilog Code Comment fonctionne un registre à décalage à rétroaction linéaire à lintérieur dun FPGA LFSR signifie Linear Feedback Shift Register et cest une conception utile à lintérieur des FPGA. Les LFSR sont simples à synthétiser, ce qui signifie quils nécessitent relat

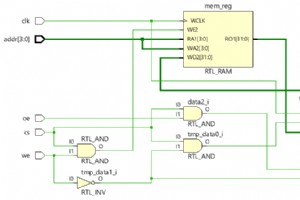

Conception module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe );

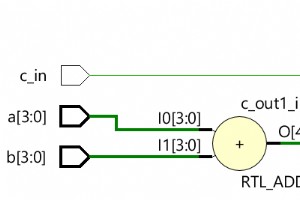

Un additionneur est un composant numérique qui effectue laddition de deux nombres. Cest le composant principal à lintérieur dune ALU dun processeur et est utilisé pour incrémenter les adresses, les index de table, les pointeurs de tampon et dans de nombreux autres endroits où un ajout est nécessaire

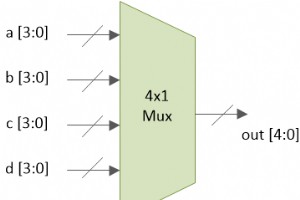

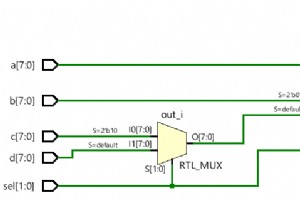

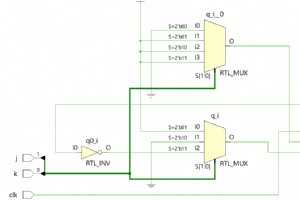

Quest-ce quun mux ou multiplexeur ? Un multiplexeur ou mux en bref, est un élément numérique qui transfère les données de lune des N entrées à la sortie en fonction du signal de sélection. Le cas illustré ci-dessous est lorsque N est égal à 4. Par exemple, un multiplexeur 4 bits aurait N entrées ch

Conception module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; e

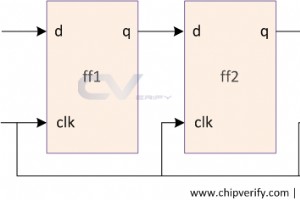

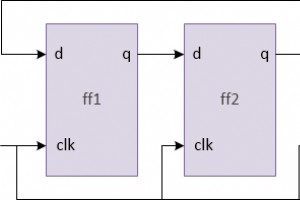

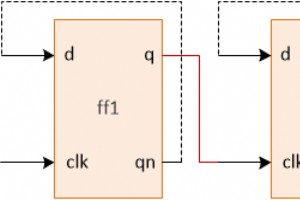

En électronique numérique, un registre à décalage est une cascade de bascules où la broche de sortie q dun flop est connecté à la broche dentrée de données (d) du suivant. Étant donné que tous les flops fonctionnent sur la même horloge, le tableau de bits stocké dans le registre à décalage se décale

Conception module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (i

Conception module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else

Conception module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i

Conception module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+

Une ondulation counter est un compteur asynchrone dans lequel tous les flops sauf le premier sont cadencés par la sortie du flop précédent. Conception module dff ( input d, input clk, input rstn, output reg q, output qn); always

Le compteur 4 bits commence à sincrémenter de 4b0000 à 4h1111, puis revient à 4b0000. Il continuera à compter tant quil est fourni avec une horloge en cours dexécution et que la réinitialisation est maintenue élevée. Le roulement se produit lorsque le bit le plus significatif de lajout final est su

Une bascule capture des données à son entrée sur le front positif ou négatif dune horloge. La chose importante à noter est que tout ce qui arrive aux données après le front dhorloge jusquau prochain front dhorloge ne sera pas reflété dans la sortie. Un loquet dautre part, ne capture pas au bord dune

Conception module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Banc de test module tb; reg clk

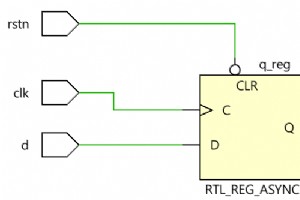

Une bascule D est un élément séquentiel qui suit la broche dentrée d au front donné dune horloge. Conception n° 1 :avec réinitialisation active-basse asynchrone module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or neg

Conception module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule

Il est toujours préférable de commencer en utilisant un exemple très simple, et aucun ne sert mieux lobjectif autre que Hello World !. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with som

Verilog a des tâches et des fonctions système qui peuvent ouvrir des fichiers, générer des valeurs dans des fichiers, lire des valeurs à partir de fichiers et charger dans dautres variables et fermer des fichiers. Ouvrir et fermer des fichiers module tb; // Declare a variable to store the file

Échelle de temps par défaut Bien que les modules Verilog soient censés avoir une échelle de temps définie avant le module, les simulateurs peuvent insérer une échelle de temps par défaut. Léchelle de temps réelle appliquée à nimporte quelle étendue dans une hiérarchie élaborée par Verilog peut être

La directive déchelle de temps Verilog spécifie lunité de temps et la précision des simulations. Verilog $timeformat la fonction système spécifie %t style de rapport du spécificateur de format dans les instructions daffichage telles que $display et $strobe . Syntaxe $timeformat(<unit_number

Verilog

Matériau des tuyaux industriels :Considérations sur les tubes centraux

Le véritable potentiel de l'IoT peut être retardé

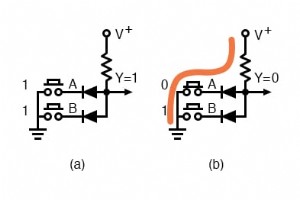

Circuits de commutation de diodes

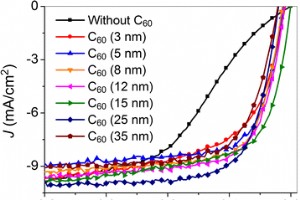

LiF 5 nm comme couche tampon cathodique efficace dans les cellules solaires polymères grâce à la simple introduction d'une couche intermédiaire C60