Tout le code comportemental est écrit dans module et endmodule . Ainsi, quel que soit le design numérique que vous avez lintention de créer, il ira à lintérieur dun module bloquer. Il peut ou non avoir des ports définis - autoriser les signaux à entrer dans le bloc en tant que input ou échapper le b

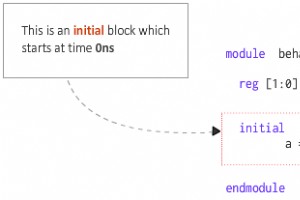

Un ensemble dinstructions Verilog est généralement exécuté séquentiellement dans une simulation. Ces instructions sont placées dans une procédurale bloquer. Il existe principalement deux types de procédure blocs dans Verilog - initial et toujours Syntaxe initial [single statement] initia

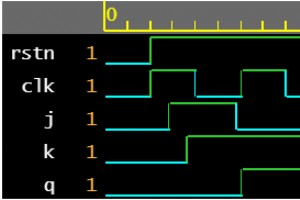

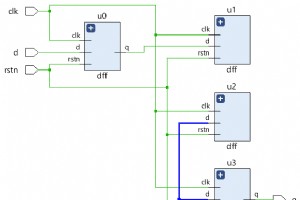

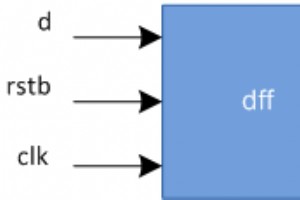

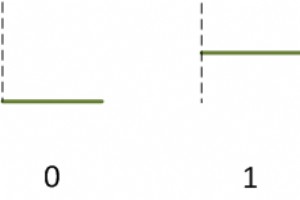

Un article précédent montrait différents exemples dutilisation dun always bloc pour implémenter la logique combinatoire. Un always Le bloc est également principalement utilisé pour implémenter séquentiel logique qui a des éléments de mémoire comme des bascules qui peuvent contenir des valeurs. Tongs

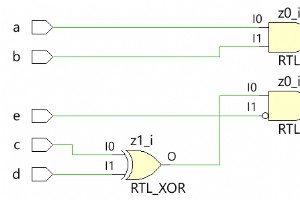

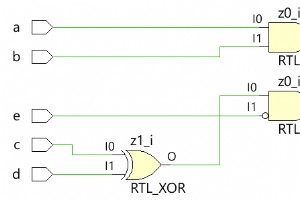

Le bloc verilog always peut être utilisé à la fois pour la logique séquentielle et combinatoire. Quelques exemples de conception ont été montrés en utilisant un assign déclaration dans un article précédent. Le même ensemble de conceptions sera ensuite exploré à laide dun always bloquer. Exemple #1 :

Un always bloc est lun des procédural blocs dans Verilog. Les instructions à lintérieur dun bloc always sont exécutées séquentiellement. Syntaxe always @ (event) [statement] always @ (event) begin [multiple statements] end Le always bloc est exécuté à un événement particulier. Lévénemen

Les fils et les variables Verilog multi-bits peuvent être regroupés pour former un fil ou une variable multi-réseau plus grand en utilisant la concaténation opérateurs { et } séparé par des virgules. La concaténation est également autorisée à avoir des expressions et des constantes dimensionnées com

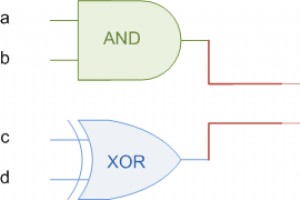

Les données qui ne peuvent pas être traitées sont tout à fait inutiles, il y aura toujours une forme de calcul requise dans les circuits numériques et les systèmes informatiques. Examinons quelques-uns des opérateurs de Verilog qui permettraient aux outils de synthèse de réaliser les éléments matéri

Linstruction verilog assign est généralement utilisée pour piloter en continu un signal de wire type de données et est synthétisé sous forme de logique combinatoire. Voici quelques exemples de conception supplémentaires utilisant le assign déclaration. Exemple #1 :Logique combinatoire simple Le cod

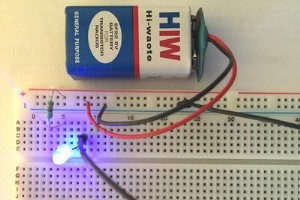

Signaux de type wire ou un fil de fer similaire comme type de données nécessite laffectation continue dune valeur. Par exemple, considérons un fil électrique utilisé pour connecter des pièces sur une planche à pain. Tant que la batterie + 5V est appliquée à une extrémité du fil, le composant connect

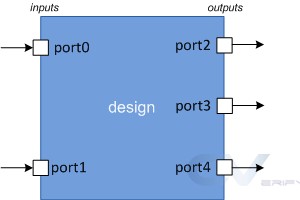

Comme nous lavons vu dans un article précédent, les conceptions plus grandes et complexes sont construites en intégrant plusieurs modules de manière hiérarchique. Les modules peuvent être instanciés dans dautres modules et ports de ces instances peut être connecté à dautres signaux à lintérieur du m

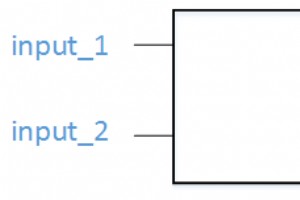

Les ports sont un ensemble de signaux qui agissent comme des entrées et des sorties vers un module particulier et constituent le principal moyen de communication avec lui. Considérez un module comme une puce fabriquée placée sur un PCB et il devient tout à fait évident que la seule façon de communiq

Un module est un bloc de code Verilog qui implémente une certaine fonctionnalité. Les modules peuvent être intégrés dans dautres modules et un module de niveau supérieur peut communiquer avec ses modules de niveau inférieur en utilisant leurs ports dentrée et de sortie. Syntaxe Un module doit être

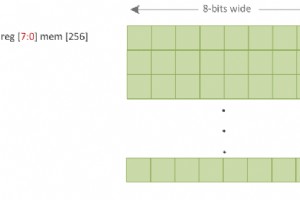

Un tableau la déclaration dun réseau ou dune variable peut être scalaire ou vectorielle. Nimporte quel nombre de dimensions peut être créé en spécifiant une plage dadresses après le nom de lidentifiant et sappelle un tableau multidimensionnel. Les tableaux sont autorisés dans Verilog pour reg , wire

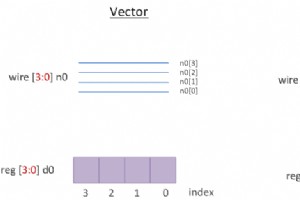

Verilog doit représenter des bits individuels ainsi que des groupes de bits. Par exemple, un élément séquentiel à un seul bit est une bascule. Or un élément séquentiel 16 bits est un registre pouvant contenir 16 bits. A cet effet, Verilog a scalaire et vecteur filets et variables. Scalaire et Vecteu

Lintention principale des types de données dans le langage Verilog est de représenter des éléments de stockage de données comme des bits dans une bascule et des éléments de transmission comme des fils qui se connectent entre des portes logiques et des structures séquentielles. Quelles sont les vale

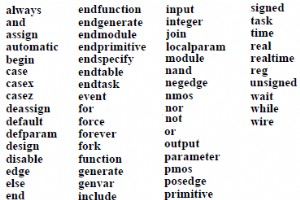

Les conventions lexicales de Verilog sont similaires à C dans le sens où il contient un flux de jetons. Un jeton lexical peut consister en un ou plusieurs caractères et les jetons peuvent être des commentaires, des mots-clés, des nombres, des chaînes ou des espaces blancs. Toutes les lignes doivent

Avant dexaminer plus en détail le langage Verilog, il serait bon de comprendre les différentes couches dabstraction dans la conception des puces. La couche supérieure est larchitecture au niveau du système qui définit les différents sous-blocs et les regroupe en fonction des fonctionnalités. Par ex

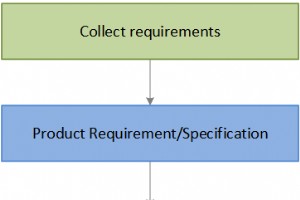

Un flux de conception typique suit une structure illustrée ci-dessous et peut être décomposé en plusieurs étapes. Certaines de ces phases se déroulent en parallèle et dautres séquentiellement. Nous examinerons à quoi ressemble un cycle de conception de projet typique dans lindustrie aujourdhui. Ex

Au début des circuits intégrés, les ingénieurs devaient sasseoir et dessiner physiquement des transistors et leurs connexions sur papier pour les concevoir de manière à pouvoir les fabriquer sur du silicium. Des circuits plus gros et complexes ont exigé plus dingénieurs, de temps et dautres ressourc

Verilog est un type de langage de description matérielle (HDL). Verilog est lun des deux langages utilisés par léducation et les entreprises pour concevoir des FPGA et des ASIC. Si vous nêtes pas familier avec le fonctionnement des FPGA et des ASIC, vous devriez lire cette page pour une introduction

Verilog