Le comportement matériel ne peut pas être mis en œuvre sans instructions conditionnelles et autres moyens de contrôler le flux de la logique. Verilog dispose dun ensemble de blocs de flux de contrôle et de mécanismes pour y parvenir. si-sinon-si Cette instruction conditionnelle est utilisé pour déc

Blocage Bloquer les instructions daffectation sont affectées à laide de = et sont exécutés les uns après les autres dans un bloc procédural. Cependant, cela nempêchera pas lexécution des instructions qui sexécutent dans un bloc parallèle. module tb; reg [7:0] a, b, c, d, e; initial begi

Placer des valeurs sur des réseaux et des variables sappelle des affectations. Il existe trois formes de base : Procédure Continu Procédure continue Valeurs LHS légales Une affectation comporte deux parties :le côté droit (RHS) et le côté gauche (LHS) avec un symbole égal (=) ou un symbole inférie

Il existe des moyens de regrouper un ensemble dinstructions qui sont syntaxiquement équivalentes à une seule instruction et sont appelées instructions de bloc . Il existe deux types dinstructions de bloc :séquentielles et parallèles. Séquentiel Les instructions sont enveloppées à laide de begin et

Un exemple précédent a exploré un détecteur de séquence simple. Voici un autre exemple de détecteur de motif qui détecte un motif légèrement plus long. Conception module det_110101 ( input clk, input rstn, input in, output out );

Un exemple très courant dun FSM est celui dun détecteur de séquence où la conception matérielle est censée détecter lorsquun motif fixe est vu dans un flux de bits binaires qui y sont entrés. Exemple module det_1011 ( input clk, input rstn, input in,

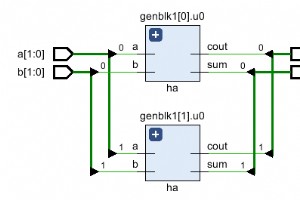

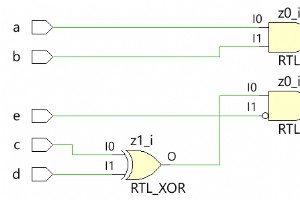

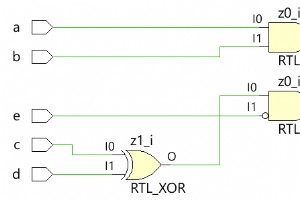

Un generate Le bloc permet de multiplier les instances de module ou deffectuer une instanciation conditionnelle de nimporte quel module. Il offre la possibilité de construire la conception en fonction des paramètres Verilog. Ces instructions sont particulièrement pratiques lorsque la même opération

Tout le code comportemental est écrit dans module et endmodule . Ainsi, quel que soit le design numérique que vous avez lintention de créer, il ira à lintérieur dun module bloquer. Il peut ou non avoir des ports définis - autoriser les signaux à entrer dans le bloc en tant que input ou échapper le b

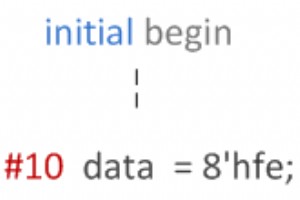

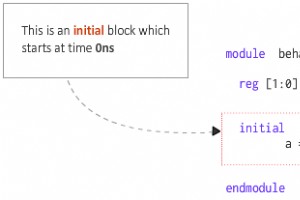

Un ensemble dinstructions Verilog est généralement exécuté séquentiellement dans une simulation. Ces instructions sont placées dans une procédurale bloquer. Il existe principalement deux types de procédure blocs dans Verilog - initial et toujours Syntaxe initial [single statement] initia

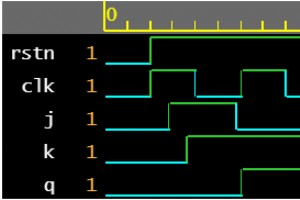

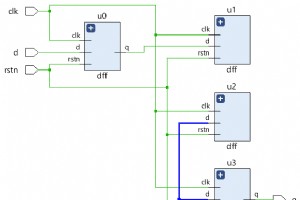

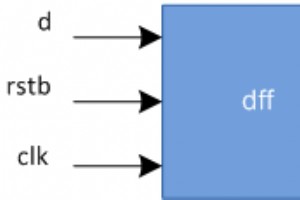

Un article précédent montrait différents exemples dutilisation dun always bloc pour implémenter la logique combinatoire. Un always Le bloc est également principalement utilisé pour implémenter séquentiel logique qui a des éléments de mémoire comme des bascules qui peuvent contenir des valeurs. Tongs

Le bloc verilog always peut être utilisé à la fois pour la logique séquentielle et combinatoire. Quelques exemples de conception ont été montrés en utilisant un assign déclaration dans un article précédent. Le même ensemble de conceptions sera ensuite exploré à laide dun always bloquer. Exemple #1 :

Un always bloc est lun des procédural blocs dans Verilog. Les instructions à lintérieur dun bloc always sont exécutées séquentiellement. Syntaxe always @ (event) [statement] always @ (event) begin [multiple statements] end Le always bloc est exécuté à un événement particulier. Lévénemen

Les fils et les variables Verilog multi-bits peuvent être regroupés pour former un fil ou une variable multi-réseau plus grand en utilisant la concaténation opérateurs { et } séparé par des virgules. La concaténation est également autorisée à avoir des expressions et des constantes dimensionnées com

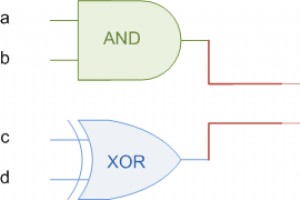

Les données qui ne peuvent pas être traitées sont tout à fait inutiles, il y aura toujours une forme de calcul requise dans les circuits numériques et les systèmes informatiques. Examinons quelques-uns des opérateurs de Verilog qui permettraient aux outils de synthèse de réaliser les éléments matéri

Linstruction verilog assign est généralement utilisée pour piloter en continu un signal de wire type de données et est synthétisé sous forme de logique combinatoire. Voici quelques exemples de conception supplémentaires utilisant le assign déclaration. Exemple #1 :Logique combinatoire simple Le cod

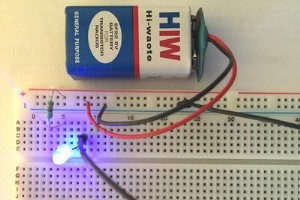

Signaux de type wire ou un fil de fer similaire comme type de données nécessite laffectation continue dune valeur. Par exemple, considérons un fil électrique utilisé pour connecter des pièces sur une planche à pain. Tant que la batterie + 5V est appliquée à une extrémité du fil, le composant connect

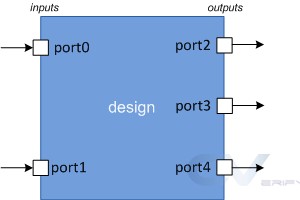

Comme nous lavons vu dans un article précédent, les conceptions plus grandes et complexes sont construites en intégrant plusieurs modules de manière hiérarchique. Les modules peuvent être instanciés dans dautres modules et ports de ces instances peut être connecté à dautres signaux à lintérieur du m

Les ports sont un ensemble de signaux qui agissent comme des entrées et des sorties vers un module particulier et constituent le principal moyen de communication avec lui. Considérez un module comme une puce fabriquée placée sur un PCB et il devient tout à fait évident que la seule façon de communiq

Un module est un bloc de code Verilog qui implémente une certaine fonctionnalité. Les modules peuvent être intégrés dans dautres modules et un module de niveau supérieur peut communiquer avec ses modules de niveau inférieur en utilisant leurs ports dentrée et de sortie. Syntaxe Un module doit être

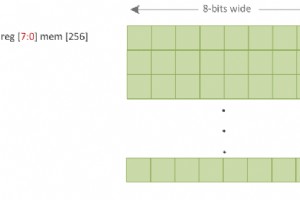

Un tableau la déclaration dun réseau ou dune variable peut être scalaire ou vectorielle. Nimporte quel nombre de dimensions peut être créé en spécifiant une plage dadresses après le nom de lidentifiant et sappelle un tableau multidimensionnel. Les tableaux sont autorisés dans Verilog pour reg , wire

Verilog

5 erreurs que nous trouvons dans la plupart des programmes de machine CNC

Maximisez le retour sur investissement avec l'automatisation et GenAI :préparez votre entreprise à l'avenir

Antich and Sons développe une technique de filage de fil composite pour la production de préformes tissées en 3D

Sablage et peinture vs peinture seule