Conception embarquée avec FPGA :Construire un projet

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

1 :ressources matérielles

2 :Langages d'implémentation

3 :Processus de développement

4 : Créer un projet (cet article)

5 :Implémentation

Adapté de Architecting High-Performance Embedded Systems, par Jim Ledin.

Développer votre premier projet FPGA

Dans cette section, nous allons développer et implémenter un projet simple mais complet en utilisant un dispositif FPGA Xilinx Artix-7 installé sur une carte de développement Digilent Arty A7. Cette carte est disponible en deux variantes, une version moins chère (129 $ US) avec un numéro de modèle se terminant par -35T et une version plus performante, mais plus coûteuse (249 $ US) avec un numéro de modèle se terminant par -100T. La seule différence entre les deux cartes est le modèle du FPGA Artix-7 installé sur la carte. Comme on peut s'y attendre, le -35T a moins de ressources disponibles que le -100T.

Vous pouvez utiliser la variante -35T ou -100T pour ce projet. La seule différence dans le processus de développement est de spécifier le bon modèle de carte chaque fois que le besoin s'en fait sentir. Cependant, dans les chapitres suivants, la variante -100T sera requise en raison des besoins en ressources de l'exemple de conception de projet d'oscilloscope numérique, c'est pourquoi la carte la plus performante est recommandée.

Les cartes Arty A7 sont disponibles à l'achat sur https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ et auprès d'autres sources, telles qu'Amazon.

Pour les besoins de ce projet, les ressources sur la carte d'intérêt sont le dispositif FPGA lui-même, ainsi que les quatre commutateurs, quatre boutons-poussoirs et cinq LED. Ce projet montrera comment installer la suite d'outils Vivado, créer un projet, saisir du code HDL, tester le code et finalement produire un flux binaire et le télécharger sur la carte. Après avoir téléchargé le bitstream sur la carte, vous pourrez tester manuellement le fonctionnement du système. Vous verrez également comment programmer l'image FPGA en mémoire flash sur la carte Arty A7 afin qu'elle se charge et s'exécute à chaque mise sous tension de la carte.

Description du projet

Ce projet implémentera un additionneur binaire à quatre bits dans le FPGA. Il s'agit intentionnellement d'une conception très simple, car l'accent est mis ici sur la configuration des outils et l'apprentissage de leur utilisation, et non sur la mise en œuvre d'un modèle HDL complexe.

Les quatre commutateurs de la carte représentent un nombre binaire de 4 bits et les quatre boutons poussoirs représentent un autre nombre de 4 bits. La logique FPGA effectuera en continu une opération d'addition entre ces deux nombres et affichera le résultat sous forme de nombre binaire à 4 bits sur quatre LED avec une cinquième LED représentant le bit de retenue.

Le code d'additionneur à 4 bits est basé sur le circuit d'additionneur complet à un seul bit décrit dans les langages de conception matérielle section du Chapitre 1 , Architecture de systèmes embarqués hautes performances .

Installation des outils Vivado

Nous utiliserons la suite Xilinx Vivado d'outils de développement FPGA pour ce projet et pour les projets des prochains chapitres. Ces outils sont disponibles gratuitement et sont pris en charge sur les systèmes d'exploitation Windows et Linux. Vous pouvez installer les outils sur l'un ou l'autre système d'exploitation. La description dans cette section couvre la version Windows des outils, mais si vous effectuez l'installation sous Linux, les différences devraient être évidentes. Le travail avec les outils Vivado devrait être presque identique sur les différents systèmes d'exploitation :

- Si vous n'en avez pas déjà un, créez un compte utilisateur Xilinx sur https://www.xilinx.com/registration/create-account.html.

- Visitez https://xilinx.com et connectez-vous à votre compte utilisateur. Une fois connecté, accédez à la page de téléchargement des outils à l'adresse https://www.xilinx.com/support/download.html.

- Téléchargez le Installateur unifié Xilinx :Programme d'installation Web auto-extractible pour Windows . Vous devriez probablement sélectionner la dernière version disponible, mais si vous souhaitez suivre la version utilisée dans ce livre, sélectionnez la version 200.1 .

- Le fichier d'installation aura un nom similaire à Xilinx_1_0602_1208_Win64.exe. Localisez ce fichier dans votre répertoire de téléchargements et exécutez-le. Si une boîte de dialogue vous avertit de l'installation d'une application qui n'est pas vérifiée par Microsoft, cliquez sur Installer quand même .

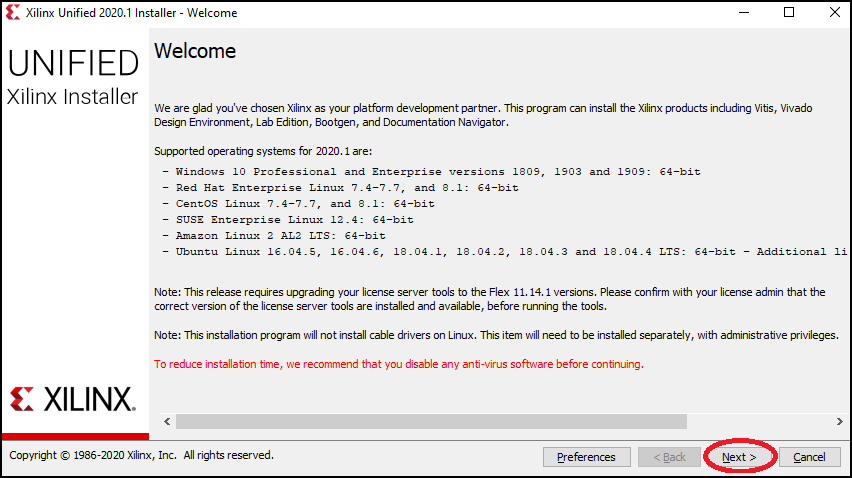

- Quand le Accueil l'écran s'affiche, cliquez sur Suivant :

Figure 4.3 – Boîte de dialogue de bienvenue de l'installateur

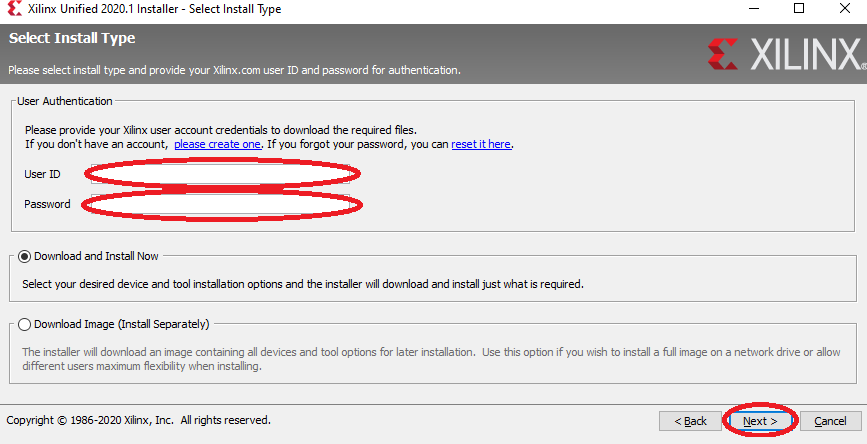

- Sur l'écran suivant, saisissez votre identifiant et votre mot de passe xilinx.com, puis cliquez sur Suivant :

Figure 4.4 – Boîte de dialogue de connexion de l'installateur

- La boîte de dialogue suivante vous demande d'accepter certains accords de licence. Cochez les cases qui disent J'accepte , puis cliquez sur Suivant .

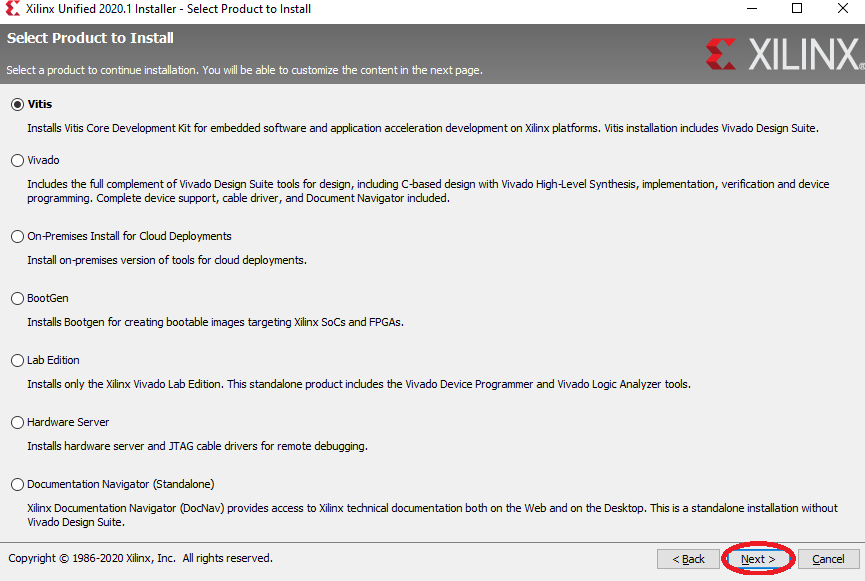

- Dans la boîte de dialogue suivante, quittez Vitis sélectionné comme produit à installer et cliquez sur Suivant . Vitis comprend la suite d'outils Vivado ainsi qu'une collection d'autres outils de développement Xilinx :

Figure 4.5 – Boîte de dialogue de sélection du produit de l'installateur

- La boîte de dialogue suivante vous permet de sélectionner les composants logiciels à installer. Laissez les sélections à leurs valeurs par défaut et cliquez sur Suivant .

- La boîte de dialogue suivante vous permet de sélectionner un répertoire de destination et de spécifier les options de raccourci du programme. Un répertoire de destination de C:\Xilinx est un emplacement approprié. Créez ce répertoire s'il n'existe pas. Cliquez sur Suivant .

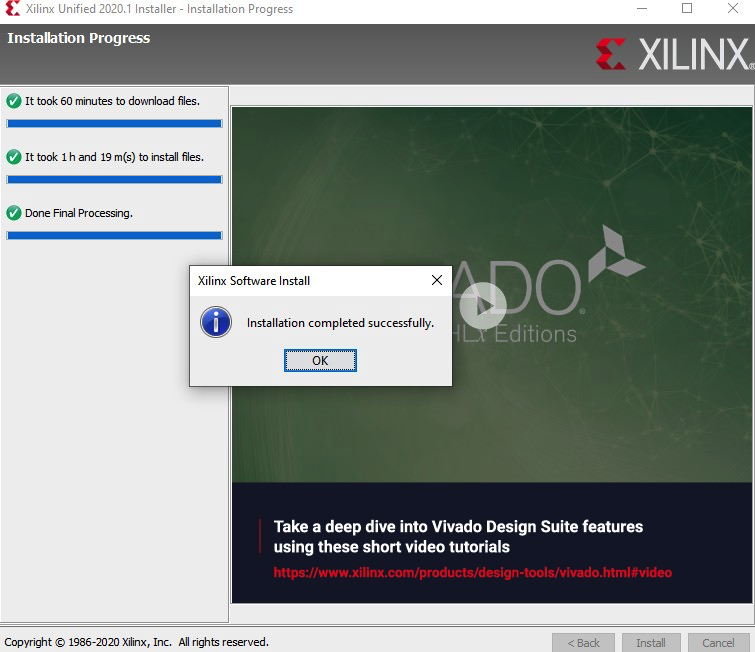

- La boîte de dialogue suivante affiche un résumé des options d'installation. Cliquez sur Installer pour procéder à l'installation. Selon la vitesse de votre ordinateur et de votre connexion Internet, l'installation peut prendre quelques heures :

Figure 4.6 – Boîte de dialogue Installation terminée

Une fois l'installation terminée, nous allons ensuite créer notre premier projet.

Créer un projet

Suivez ces étapes pour créer et construire le projet d'additionneur binaire 4 bits pour la carte Arty A7 :

- Recherchez l'icône du bureau intitulée Vivado 2020.1 (ou recherchez votre numéro de version, s'il est différent) et double-cliquez dessus.

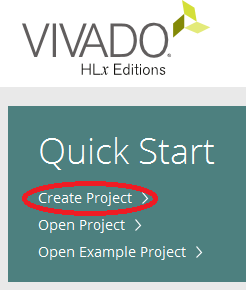

- Lorsque Vivado affiche son écran principal, cliquez sur Créer un projet dans le Démarrage rapide rubrique :

Figure 4.7 – Boîte de dialogue de démarrage rapide de Vivado

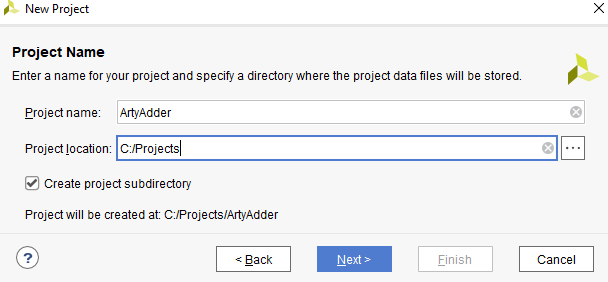

- Cela lancera le Créer un nouveau projet Vivado sorcier. Cliquez sur Suivant pour atteindre le Nom du projet page et entrez ArtyAdder comme nom de projet. Sélectionnez un emplacement de répertoire approprié pour le projet et cochez la case pour créer un sous-répertoire, puis cliquez sur Suivant . Les exemples dans ce livre utiliseront le répertoire C:\Projects comme emplacement pour tous les projets :

Figure 4.8 – Boîte de dialogue Nom du projet

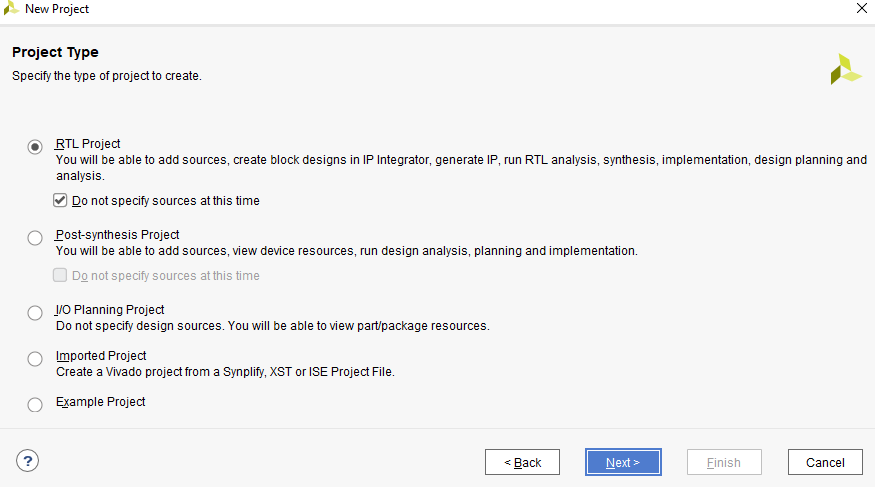

- Dans le Type de projet dialogue, sélectionnez Projet RTL et cochez la case à côté de Ne spécifiez pas les sources pour le moment . Cliquez sur Suivant :

Figure 4.9 – Boîte de dialogue Type de projet

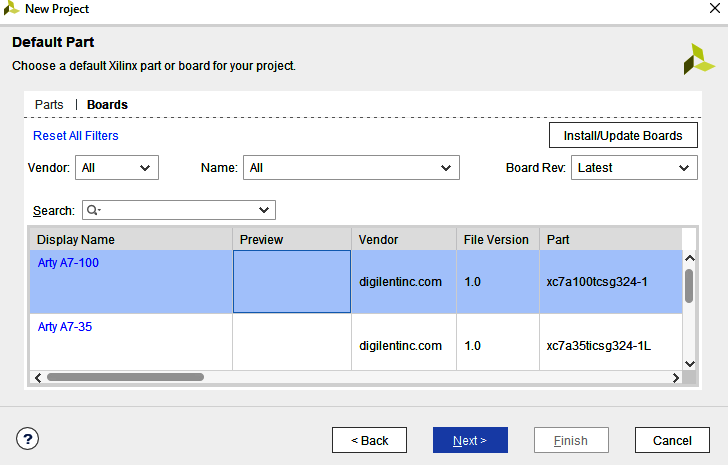

- Dans la partie par défaut dialogue, cliquez sur les Tableaux onglet et tapez Arty dans la Rechercher domaine. Selon le type de planche que vous possédez (ou si vous n'en avez pas encore), sélectionnez soit l'Arty A7-100 ou Arty A7-35 et cliquez sur Suivant :

Figure 4.10 – Boîte de dialogue Pièce par défaut

- Dans le Résumé du nouveau projet boîte de dialogue, cliquez sur Terminer .

Nous avons maintenant créé un projet vide. Dans la section suivante, nous allons créer des fichiers source VHDL contenant la conception du circuit logique pour ce projet.

Création de fichiers source VHDL

Les étapes suivantes décrivent le processus de création de fichiers source VHDL, de saisie du code source et de compilation de la conception FPGA :

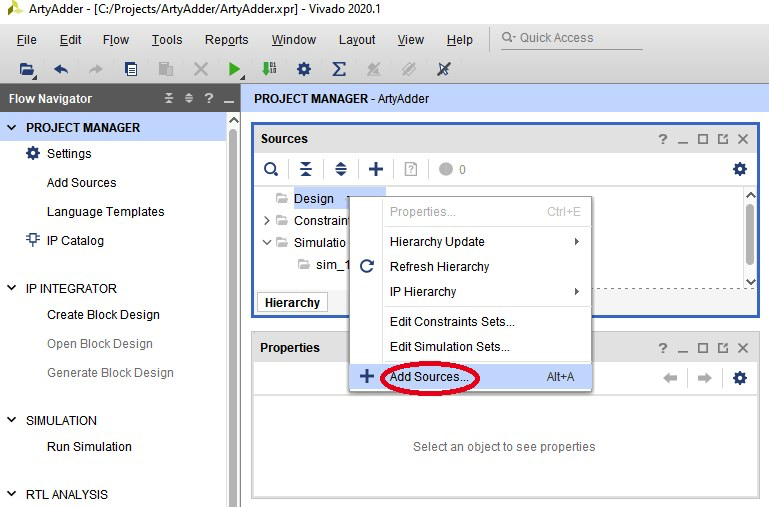

- Dans les Sources sous-fenêtre, cliquez avec le bouton droit sur Sources de conception et sélectionnez Ajouter des sources… :

Figure 4.11 – Sélection du menu Ajouter des sources…

- Dans Ajouter des sources dialogue, assurez-vous d'Ajouter ou créer des sources de conception est sélectionné, puis cliquez sur Suivant .

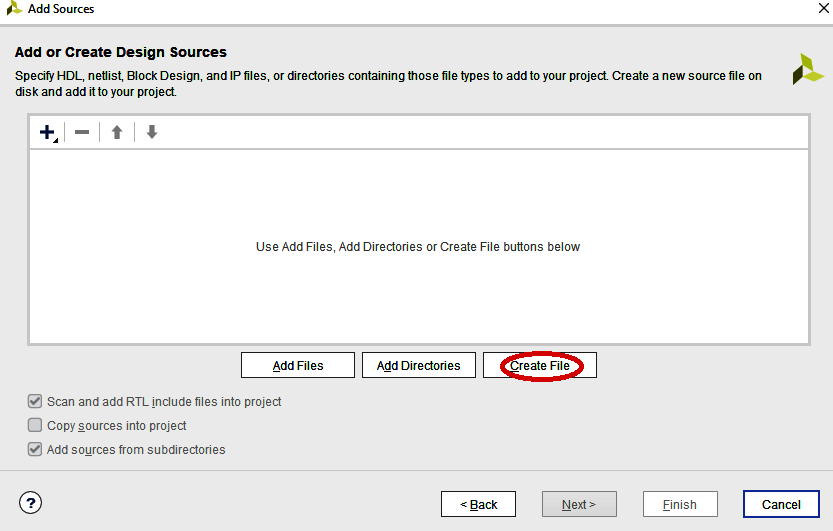

- Dans Ajouter ou créer des sources de conception boîte de dialogue, cliquez sur Créer un fichier :

Figure 4.12 – Boîte de dialogue Ajouter ou créer des sources de conception

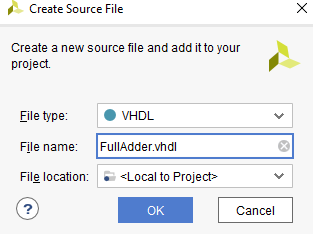

- Entrez le nom de fichier FullAdder.vhdl et cliquez sur OK :

Figure 4.13 – Boîte de dialogue Créer un fichier source

- Répétez les deux étapes précédentes pour créer un autre fichier nommé Adder4.vhdl, puis cliquez sur Terminer dans Ajouter ou créer des sources de conception dialogue.

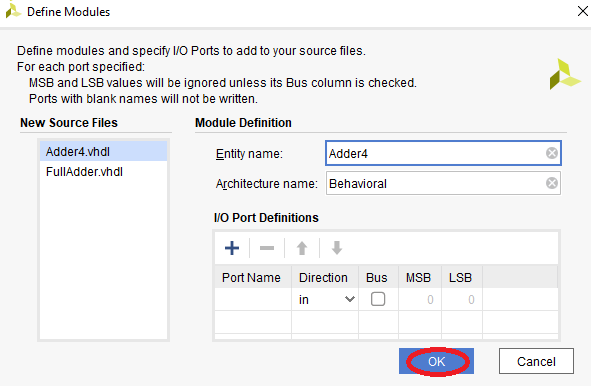

- Les définir les modules dialogue apparaîtra ensuite. Nous n'entrerons rien ici. Cliquez sur OK pour fermer ceci Il vous sera demandé si vous êtes sûr de vouloir utiliser ces valeurs. Cliquez sur Oui :

Figure 4.14 – Boîte de dialogue Définir les modules

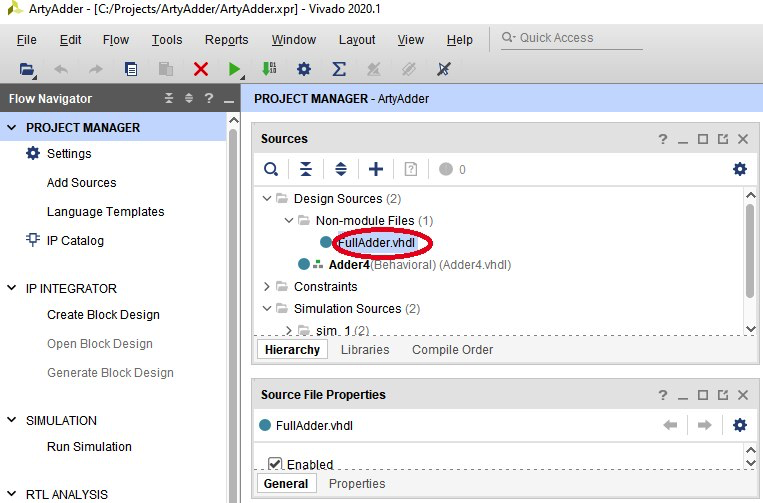

- Développez les Fichiers hors module sous Sources de conception , puis double-cliquez sur FullAdder.vhdl. Une fenêtre d'éditeur s'ouvrira affichant le fichier FullAdder.vhdl vide :

Figure 4.15 – Fichier source nouvellement créé

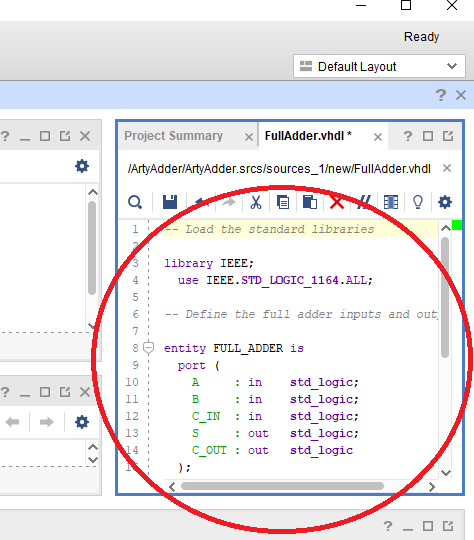

- Saisissez le code VHDL suivant dans la fenêtre de l'éditeur FullAdder.vhdl :

-- Charge la bibliothèque de bibliothèques standard IEEE ; utiliser IEEE.STD_LOGIC_1164.ALL;-- Définir les entrées et sorties complètes de l'additionneur L'entité FULL_ADDER est le port ( A :in std_logic; B :in std_logic; C_IN :in std_logic; S :out std_logic; C_OUT :out std_logic );end entity FULL_ADDER; -- Définir le comportement de l'architecture complète d'additionneur BEHAVIORAL de FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A ET B) OU ((A XOR B) ET C_IN);fin architecture COMPORTEMENT;

Il s'agit du même code d'additionneur complet à un seul bit que nous avons examiné dans les langages de conception matérielle section du Chapitre 1, Architecture des systèmes embarqués hautes performances . Figure 4.16 affiche le code dans la fenêtre de l'éditeur Vivado :

Figure 4.16 – Code source de FullAdder.vhdl

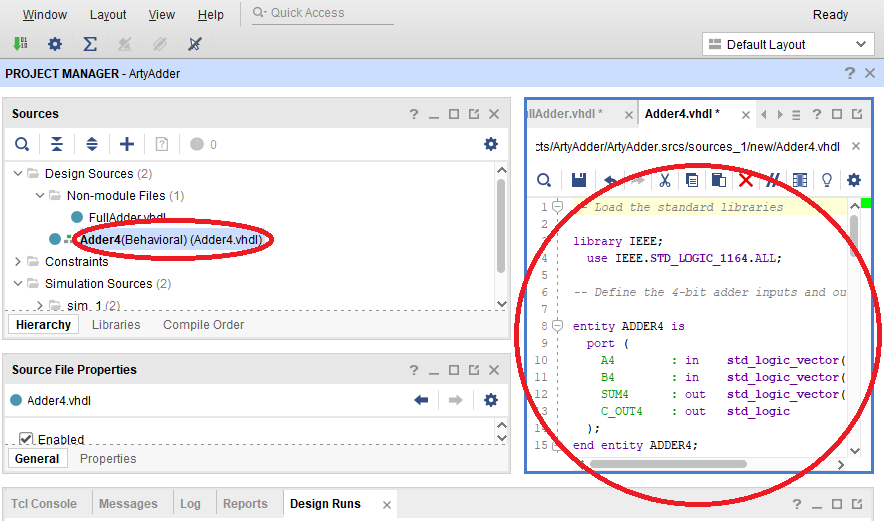

- De la même manière, double-cliquez sur Adder4(Behavioral) (Adder4.vhdl) sous Sources de conception . Supprimez le contenu automatiquement renseigné de Adder4.vhdl fenêtre de l'éditeur et entrez le code suivant dans le fichier Adder4.vhdl éditeur :

-- Charge la bibliothèque de bibliothèques standard IEEE ; utiliser IEEE.STD_LOGIC_1164.ALL ;-- Définir les entrées et sorties de l'additionneur 4 bits L'entité ADDER4 est le port ( A4 :dans std_logic_vector (3 jusqu'à 0); B4 :dans std_logic_vector (3 jusqu'à 0); SUM4 :out std_logic_vector (3 jusqu'à 0 ); C_OUT4 :out std_logic );end entity ADDER4;-- Définir le comportement de l'architecture d'additionneur 4 bits BEHAVIORAL de ADDER4 est -- Référencez la définition précédente du composant d'additionneur complet FULL_ADDER est le port ( A :in std_logic; B :in std_logic; C_IN :in std_logic; S :out std_logic; C_OUT :out std_logic ); composant final; -- Définir les signaux utilisés en interne dans le signal d'additionneur 4 bits c0, c1, c2 :std_logic;begin -- L'entrée de report du premier additionneur est mise à 0 FULL_ADDER0 :FULL_ADDER mappage de port ( A => A4(0), B => B4(0), C_IN => '0', S => SUM4(0), C_OUT => c0 ); FULL_ADDER1 :mappage des ports FULL_ADDER ( A => A4(1), B => B4(1), C_IN => c0, S => SUM4(1), C_OUT => c1 ); FULL_ADDER2 :mappage des ports FULL_ADDER ( A => A4(2), B => B4(2), C_IN => c1, S => SUM4(2), C_OUT => c2 ); FULL_ADDER3 :mappage des ports FULL_ADDER ( A => A4(3), B => B4(3), C_IN => c2, S => SUM4(3), C_OUT => C_OUT4 );fin architecture BEHAVIORAL;

Ce code instancie quatre copies de l'additionneur complet à un seul bit. Le report dans l'additionneur le moins significatif est mis à zéro et le report de chaque additionneur ondule au prochain additionneur le plus significatif. Le résultat de l'addition de deux nombres de 4 bits est un résultat de 4 bits et un report d'un seul bit :

Figure 4.17 – Code source Adder4.vhdl

Le prochain article montrera comment tester la conception et implémenter notre conception pour la carte Arty.

Réimprimé avec la permission de Packt Publishing. Copyright © 2021 Édition Packt

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT).

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT). Contenus associés :

- Conception embarquée avec FPGA :ressources matérielles

- Conception embarquée avec FPGA :langages d'implémentation

- Conception embarquée avec FPGA :processus de développement

- Les outils open source aident à simplifier la programmation FPGA

- Implémentation d'algorithmes à virgule flottante dans les FPGA ou les ASIC

- Tirer parti des FPGA pour l'apprentissage en profondeur

- Les outils logiciels migrent le code GPU vers les FPGA pour les applications d'IA

- Les FPGA remplacent les ASIC dans les ADAS basés sur la vision Subaru Eyesight

Pour plus d'informations sur Embedded, abonnez-vous à la newsletter hebdomadaire d'Embedded.

Embarqué

- Fabrication additive liquide :Construire des objets 3D avec du liquide

- Qu'est-ce que la conception de systèmes embarqués :étapes du processus de conception

- Arrow Electronics lance un concours européen de développeurs FPGA

- Kit de conception mesure la tension artérielle avec capteur optique

- Débuts de FPGA de niveau défense avec accès anticipé

- Créer des robots avec Raspberry Pi et Python

- Construire un segway avec Raspberry Pi

- GoPiGo v2 avec Windows IoT

- Tout compris avec additif