Les fonctions mathématiques Verilog peuvent être utilisées à la place des expressions constantes et prennent en charge à la fois entier et réel mathématiques. Fonctions mathématiques entières La fonction $clog2 renvoie le plafond de log2 de largument donné. Ceci est généralement utilisé pour calcu

Les tâches système daffichage sont principalement utilisées pour afficher des messages dinformation et de débogage afin de suivre le flux de simulation à partir des fichiers journaux et permettent également de déboguer plus rapidement. Il existe différents groupes de tâches daffichage et de formats

Les horloges sont fondamentales pour la construction de circuits numériques car elles permettent à différents blocs dêtre synchronisés les uns avec les autres. Propriétés dune horloge Les principales propriétés dune horloge numérique sont sa fréquence qui détermine la période dhorloge , son cycle d

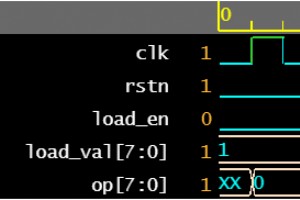

La conception et le testbench de Verilog ont généralement de nombreuses lignes de code comprenant always ou initial blocs, affectations continues et autres instructions procédurales qui deviennent actives à différents moments au cours dune simulation. Chaque changement de valeur dun signal dans le

La simulation Verilog dépend de la façon dont le temps est défini car le simulateur doit savoir ce que signifie un #1 en termes de temps. Le `timescale La directive du compilateur spécifie lunité de temps et la précision des modules qui la suivent. Syntaxe `timescale <time_unit>/<time_

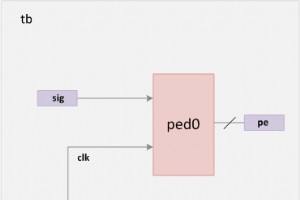

Verilog est un langage de description de matériel et les concepteurs ne sont pas tenus de simuler leurs conceptions RTL pour pouvoir les convertir en portes logiques. Alors, quel est le besoin de simuler ? La simulation est une technique consistant à appliquer différents stimulus dentrée à la con

Primitives Verilog standard comme nand et not nest pas toujours facile ou suffisant pour représenter une logique complexe. Nouveaux éléments primitifs appelés UDP ou primitives définies par lutilisateur peut être défini pour modéliser une logique combinatoire ou séquentielle. Tous les UDP ont exact

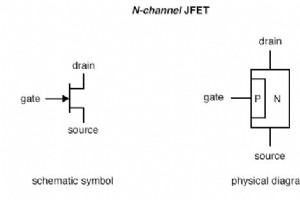

Verilog prend également en charge la modélisation au niveau des transistors, bien quelle soit rarement utilisée par les concepteurs de nos jours, car la complexité des circuits les a obligés à passer à des niveaux dabstraction plus élevés plutôt quà utiliser la modélisation au niveau des commutateur

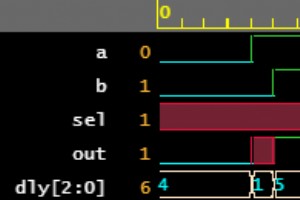

Les éléments numériques sont des entités binaires et ne peuvent contenir que lune ou lautre des deux valeurs - 0 et 1. Cependant, la transition de 0 à 1 et de 1 à 0 a un retard de transition, tout comme chaque élément de porte pour propager la valeur de lentrée à sa sortie. Retards de montée, de d

Certaines des principales primitives intégrées ont été abordées dans larticle précédent et il serait bon de voir quelques exemples pratiques dutilisation de simples and , nor et not portes. Notez que pour écrire le code Verilog à laide de gates, il est nécessaire que vous sachiez connecter les élém

La plupart des conceptions numériques sont réalisées à un niveau dabstraction plus élevé comme RTL, bien quil devienne parfois intuitif de construire des circuits déterministes plus petits à un niveau inférieur en utilisant des éléments combinatoires comme et et ou . La modélisation effectuée à ce n

La plupart des langages de programmation ont une caractéristique appelée portée qui définit la visibilité de certaines sections de code aux variables et aux méthodes. La portée définit un espace de noms pour éviter les collisions entre différents noms dobjets dans le même espace de noms. Verilog dé

Les déclarations de retard Verilog peuvent avoir des retards spécifiés soit sur le côté gauche, soit sur le côté droit de lopérateur daffectation. Retards entre affectations // Delay is specified on the left side #<delay> <LHS> = <RHS> Une inter-affectation Linstruction de

Il existe deux types de contrôles de synchronisation dans Verilog - retard et événement expressions. Le retard control est juste un moyen dajouter un délai entre le moment où le simulateur rencontre linstruction et le moment où il lexécute réellement. Lexpression dévénement permet de retarder linstr

Verilog prend en charge quelques directives de compilateur qui ordonnent essentiellement au compilateur de traiter le code dune certaine manière. Par exemple, une partie du code peut représenter une implémentation dune certaine fonctionnalité et il devrait y avoir un moyen de ne pas inclure le code

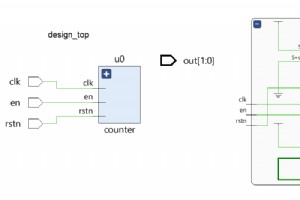

Les paramètres sont des constructions Verilog qui permettent à un module dêtre réutilisé avec une spécification différente. Par exemple, un additionneur 4 bits peut être paramétré pour accepter une valeur pour le nombre de bits et de nouvelles valeurs de paramètre peuvent être transmises lors de lin

Un function est destiné à effectuer un traitement sur lentrée et à renvoyer une seule valeur, alors quun task est plus général et peut calculer plusieurs valeurs de résultat et les renvoyer en utilisant la sortie et inout arguments de type. Les tâches peuvent contenir des éléments chronophages de si

Souvent, nous constatons que certains morceaux de code sont répétitifs et appelés plusieurs fois dans le RTL. Ils ne consomment généralement pas de temps de simulation et peuvent impliquer des calculs complexes qui doivent être effectués avec différentes valeurs de données. Dans ce cas, on peut décl

Le case Linstruction vérifie si lexpression donnée correspond à lune des autres expressions de la liste et se branche en conséquence. Il est généralement utilisé pour implémenter un multiplexeur. La construction if-else peut ne pas convenir sil y a de nombreuses conditions à vérifier et se synthétis

Un for loop est la boucle la plus largement utilisée dans les logiciels, mais elle est principalement utilisée pour répliquer logique matérielle dans Verilog. Lidée derrière un for boucle consiste à itérer un ensemble dinstructions données dans la boucle tant que la condition donnée est vraie. Ceci

Verilog

La technologie va-t-elle vraiment détruire des emplois ? Amber Rudd estime que l'automatisation est à l'origine du déclin du banal

L'entrepôt de données n'est pas mort :il a juste besoin d'une refonte de l'automatisation

Introduction aux transistors à effet de champ à jonction (JFET)

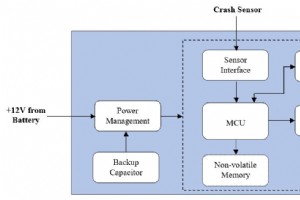

Répondre aux nouvelles exigences en matière d'enregistrement de données fiable dans les systèmes automobiles