Étude sur l'effet des paramètres structurels et du mécanisme interne d'un transistor à effet de champ tunnel bidirectionnel symétrique et interchangeable S/D contrôlé par porte

Résumé

Un transistor à effet de champ tunnel bidirectionnel symétrique et interchangeable S/D contrôlé par grille bilatérale (B-TFET) est proposé dans cet article, qui montre l'avantage des caractéristiques de commutation bidirectionnelle et de la compatibilité avec les circuits intégrés CMOS par rapport au TFET asymétrique conventionnel. Les effets des paramètres structurels, par exemple, les concentrations de dopage du N + région et P + région, longueur du N + région et longueur de la région intrinsèque, sur les performances de l'appareil, par exemple, les caractéristiques de transfert, I sur –Je désactivé rapport et oscillation sous le seuil, et le mécanisme interne sont discutés et expliqués en détail.

Introduction

La consommation d'énergie est l'un des principaux problèmes de l'industrie des circuits intégrés. Si un appareil fonctionne à l'état passant, son courant de conduction doit atteindre une certaine valeur critique; lorsque le courant atteint une valeur critique, la tension de grille correspondante est définie comme la tension de seuil. Lorsque l'appareil est à l'état bloqué, la tension de grille correspondante doit être une valeur différente de celle de l'état passant critique, qui est souvent appelée tension à l'état bloqué. Le concept d'oscillation sous le seuil (SS) s'applique au dispositif qui fonctionne entre l'état désactivé et l'état activé critique, qui est égal à la variation de la tension de grille lorsque le courant augmente d'un ordre de grandeur. Lorsque l'appareil est bien conçu, la valeur critique du courant à l'état passant, la tension de seuil et la tension à l'état bloqué de l'appareil ont été déterminées ; alors, un SS plus petit correspond à des changements de courant plus forts dans la zone sous-seuil, à un courant statique plus petit du dispositif à l'état éteint et à une consommation d'énergie statique inférieure du dispositif. La SS des transistors à effet de champ à oxyde métallique et semi-conducteur (MOSFET), qui sont les cellules unitaires de base largement utilisées dans les circuits intégrés, est limitée par le mécanisme physique du courant généré pendant le fonctionnement du dispositif et ne peut être inférieure à la valeur limite de 60 mV/déc. Pour dépasser cette limitation, un transistor à effet de champ tunnel (PIN ou NIP TFET) basé sur une technologie à base de silicium a été proposé ces dernières années. Un TFET conventionnel est formé en ajoutant une couche de semi-conducteurs intrinsèques à faible dopage entre p - et n -matériaux semi-conducteurs de type. Comparé au MOSFET, le TFET présente les avantages d'une sensibilité élevée et d'une faible consommation d'énergie statique [1]. Le TFET est commuté en modulant l'effet tunnel quantique à travers une barrière au lieu de moduler l'émission thermoionique sur une barrière comme dans le MOSFET traditionnel. Ainsi, le TFET n'est pas limité par la queue thermique de Maxwell-Boltzmann des porteurs, qui limite la SS du MOSFET à 60 mV/dec à température ambiante [2] (exactement 63 mV/dec à 300 K). Le concept a été proposé par Chang et al. tout en travaillant chez IBM [3]. Pour la première fois, Joerg Appenzeller et ses collègues d'IBM ont démontré que le SS du TFET pouvait être inférieur à 60 mV/déc. Les TFET peuvent être utilisés comme commutateurs électroniques économes en énergie [4], ce qui permet de surmonter le goulot d'étranglement des MOSFET et de réduire considérablement la consommation d'énergie des circuits intégrés. Le processus de production est compatible avec les MOSFET. Il est susceptible de remplacer le transistor MOSFET comme unité de base des circuits intégrés de nouvelle génération. Par conséquent, les TFET sont devenus un sujet brûlant ces dernières années [5, 6]. Pour améliorer les performances des TFET en termes de SS, de courant conducteur direct et de fuite inverse, de nombreuses études sur la conception de la structure et l'optimisation des dispositifs TFET ont été menées, qui se concentrent principalement sur l'amélioration de la forme de la structure du canal du dispositif et de l'électrode de grille [7 ,8,9,10,11,12] et les matériaux diélectriques de grille avec différentes fonctions de travail. L'analyse des caractéristiques et l'optimisation de la structure du matériau diélectrique de grille [13,14,15] et des diélectriques de grille avec différentes constantes diélectriques ont été réalisées [15,16,17,18,19,20]. En physique des dispositifs, la modélisation analytique des TFET avec la structure à double grille [21,22,23,24,25,26,27] et la structure à grille environnante [28,29,30,31,32,33] a également été largement réalisée. Un inconvénient des TFET à base de silicium par rapport aux MOSFET est le courant direct plus petit, et l'amplitude du courant direct est déterminée par l'efficacité de la génération de courant tunnel. L'efficacité de génération de courant tunnel peut être augmentée en réduisant la bande interdite entre la bande de valence et la bande de conduction dans la région qui est utilisée pour générer le courant tunnel de bande à bande ou en réduisant l'épaisseur de la région à effet tunnel. Par conséquent, en ingénierie des matériaux, les dispositifs TFET basés sur des matériaux semi-conducteurs à bande interdite étroite et des structures à effet tunnel à hétérojonction ont été largement développés [34,35,36,37,38]. Pendant ce temps, l'introduction de matériaux bidimensionnels dans les TFET sous forme de couches à effet tunnel avec une épaisseur ultrafine a été largement étudiée [39,40,41,42,43,44]. De plus, certains articles ont rapporté la fiabilité des TFET, tels que l'effet du dopage de la source sur l'entrelacement de la bande interdite à effet tunnel [45], l'effet de l'effet tunnel assisté par piège sur les caractéristiques sous-seuil des TFET [46], et l'effet de l'effet aléatoire. dopage sur la perturbation des performances de l'appareil [47]. Cependant, les résultats de recherche actuels visent principalement les caractéristiques de fonctionnement de base et les principes de fonctionnement des TFET simples, et l'objectif fondamental le plus important de la recherche et du développement des TFET est de fournir une unité structurelle de base avec une consommation d'énergie inférieure et de remplacer la structure MOSFET existante. . Pour atteindre cet objectif fondamental, il doit être placé dans un circuit spécifique pour vérifier sa compatibilité avec la technologie MOSFET. À l'heure actuelle, des recherches sur la stratégie de conception de circuits basée sur des dispositifs TFET sont progressivement menées, telles que le circuit de signaux analogiques et mixtes [48, 49, 50], le circuit logique numérique [50, 51], la conception de circuits de gestion de l'alimentation [52]. Il existe également des études sur la conception de circuits hybrides à base de MOSFET et de TFET [53]. Cependant, les types de dopage de la région de source et de la région de drain sont opposés l'un à l'autre, ce qui crée une asymétrie entre la région de source et la région de drain. Cette structure asymétrique rend impossible le remplacement complet du MOSFET par la symétrie source/drain.

Prenez le n -type TFET comme exemple. Le côté avec p -type impureté est utilisé comme région source, tandis que l'autre côté avec n -une impureté de type est utilisée comme région de drain. Lorsque le dispositif fonctionne, une différence de potentiel positive doit être appliquée de la région de drain à la région de source. Si l'électrode de source et l'électrode de drain sont interverties, c'est-à-dire le p -la région d'impureté de type est définie à un potentiel plus élevé par rapport au n -région d'impureté de type, puis la jonction PN formée par le p -type impureté région et n -La région d'impureté de type sera toujours dans l'état de polarisation positive, ce qui provoque l'échec de la fonction de commande de l'électrode de grille, le TFET sera presque toujours à l'état passant et ne peut pas être éteint. En d'autres termes, cela provoque l'échec de la fonction de commutation TFET. En d'autres termes, les modules fonctionnels du circuit (comme les portes de transmission), qui doivent utiliser les caractéristiques de commutation bidirectionnelle des transistors pour fonctionner normalement, sont difficiles à réaliser en utilisant des TFET classiques avec une structure asymétrique de source et de drain, afin de résoudre ces problèmes. , nous avons proposé un TFET bidirectionnel symétrique et interchangeable source drain (B-TFET) [54], qui montre l'avantage des caractéristiques de commutation bidirectionnelle et de la compatibilité avec les circuits intégrés CMOS par rapport aux TFET asymétriques traditionnels. Dans cet article, nous avons proposé un B-TFET bilatéral modifié avec un canal planaire. Les effets de paramètres structurels clés, tels que les concentrations de dopage du N + région et P + région, longueur du N + région et longueur de la région intrinsèque, sur les performances de l'appareil, par exemple, les caractéristiques de transfert, I sur –Je désactivé rapport et l'oscillation sous le seuil, sont expliqués en détail sur la base d'une analyse physique. Par la suite, ces paramètres structurels clés sont optimisés.

Méthodes

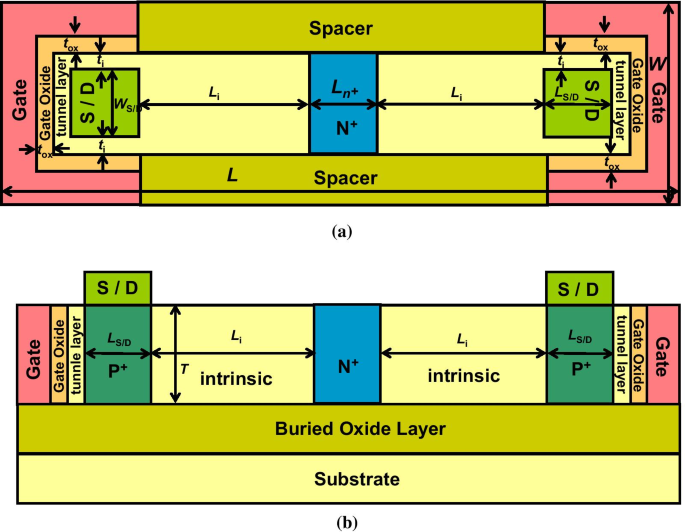

La figure 1a montre une vue de dessus schématique du TFET B de type N bilatéral contrôlé par porte avec un canal planaire. La figure 1b montre une vue croisée du TFET B de type N bilatéral contrôlé par porte. Contrairement au TFET classique, le B-TFET proposé est complètement symétrique, la source/drain P + interchangeable -des régions dopées s'étendent de chaque côté du corps en silicium, et l'électrode de grille s'étend des deux côtés du corps en silicium. L'ensemble de la structure de l'appareil est symétrique. Le N + -la région dopée se trouve dans la partie centrale du corps en silicium. L et W sont respectivement toute la longueur et toute la largeur du dispositif proposé. L je est la longueur de la région intrinsèque ; L N+ est la longueur du N + Région; L S/D et W S/D sont la longueur et la largeur du P + les régions interchangeables source/drain, respectivement ; \(T\) est l'épaisseur du corps en silicium ; \(t_{{{\text{ox}}}}\) est l'épaisseur de l'oxyde de grille ; \(t_{i}\) est l'épaisseur de la région tunnel intrinsèque entre la région S/D et l'oxyde de grille.

un Vue schématique de dessus du TFET de type N bilatéral contrôlé par porte avec canal planaire. b Vue croisée du N-Type B-TFET bilatéral contrôlé par porte

Dans cet article, tous les modèles physiques tels que le modèle statistique de Fermi, le modèle de mobilité CVT, le modèle de recombinaison Auger, le modèle de réduction de bande interdite et un modèle de tunnelage bande à bande standard sont activés. Tous les paramètres de l'appareil dans ce document sont répertoriés dans le tableau 1.

Résultats et discussion

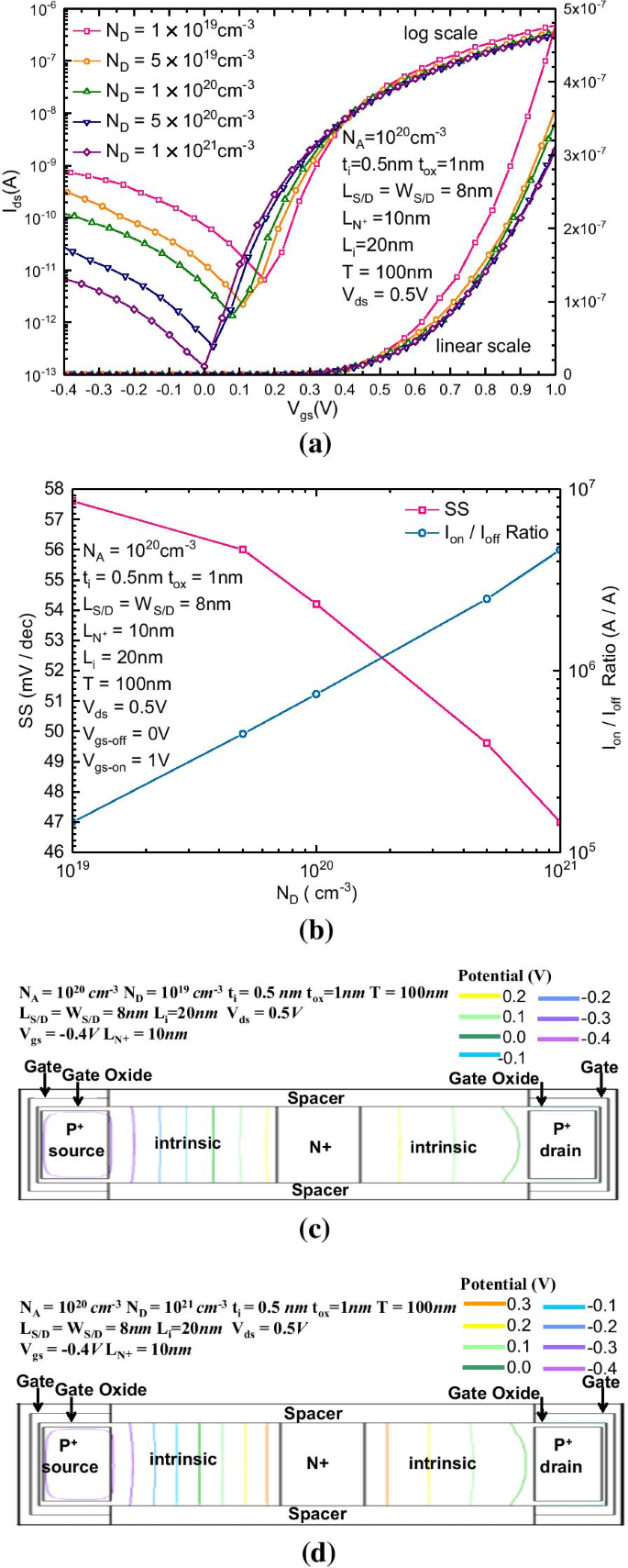

Les figures 2a, b montrent la caractéristique de transfert, le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) et le SS moyen avec différents \(N_{ D}\) (\(10^{18}\)–\(10^{21} \,{\text{cm}}^{ - 3}\)). Sur la figure 2a, \(N_{D}\) affecte l'intensité du courant de fuite drain-source polarisé en inverse. Avec l'augmentation de la concentration de dopage, le courant de fuite est considérablement supprimé et le courant direct ne change pas de manière significative. Dans la figure 2b, le SS et \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) sont également affectés par \(N_{D}\ ). Avec l'augmentation de la concentration de dopage, du fait que le courant de fuite inverse est considérablement supprimé, le courant au point de fonctionnement statique diminue, de sorte que la SS moyenne diminue également. Parce que le courant direct est beaucoup moins affecté que la fuite inverse, le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) augmente avec l'augmentation en concentration de dopage. La figure 2c, d montre les distributions potentielles bidimensionnelles du B-TFET proposé avec \(N_{D}\) égal à 10 19 cm −3 et 10 21 cm −3 , respectivement. Lorsque l'électrode de grille est polarisée en inverse, un champ électrique puissant sera généré entre l'électrode de drain polarisée en direct et l'électrode de grille polarisée en inverse, ce qui entraîne un fort effet tunnel de bande à bande près de la région de drain. Parmi les paires électron-trou générées résultantes, les électrons peuvent directement sortir de l'électrode de drain, tandis que les trous de la bande de valence doivent traverser le N + région, subséquemment à la région intrinsèque du côté source et être déchargée par l'électrode source pour former le courant de fuite continu. Pour minimiser le courant de fuite, les trous produits par l'effet tunnel de bande à bande doivent être efficacement bloqués afin qu'ils ne s'échappent pas de la région N + . Par rapport à la région N + avec une concentration plus faible, la région N + avec une concentration plus élevée forme une plus grande différence de potentiel entre la région P + et la région N + , c'est-à-dire que la valeur potentielle à la frontière entre la région intrinsèque et la région N + augmentera avec l'augmentation de \(N_{D}\) car la région N + avec une concentration plus élevée peut produire une plus grande différence de concentration électronique entre la source et le drain. Ensuite, plus d'électrons peuvent être diffusés de la région N + vers les régions intrinsèques des deux côtés de la région N + , ce qui augmente la quantité de charge positive (principalement composée de donneur) dans la région N + après ionisation et augmente par conséquent le potentiel différence entre la région P + et la région N + . Précisément parce que la région N + avec une concentration de dopage plus élevée a un potentiel plus élevé que les côtés source et drain après ionisation, les trous générés par l'effet tunnel de bande à bande près de la région de drain peuvent être bloqués plus efficacement, ce qui diminue plus efficacement le courant de fuite.

un \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) caractéristiques de transfert et b variation de SS et le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) du B-TFET proposé avec différents \(N_{D }\); la distribution de potentiel bidimensionnelle inversée avec c N D = 10 19 cm −3 et d N D = 10 21 cm −3

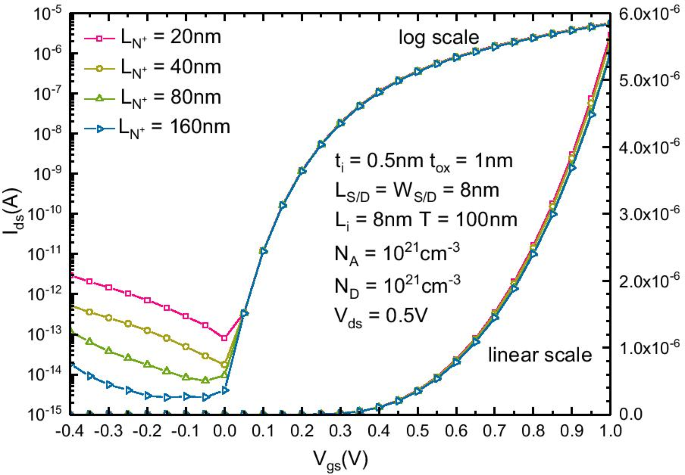

En plus de la concentration de dopage de la région N + , un autre paramètre clé de la région N + , qui peut affecter de manière significative le courant de fuite polarisé en inverse, est la longueur de la région N + . Les figures 3a, b montrent les caractéristiques de transfert \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) du B-TFET proposé avec différents L N+ . Le courant de fuite polarisé en inverse diminue largement avec l'augmentation de L N+ . Comme le montre la figure 2b, l'oscillation sous-seuil et \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) sont également affectées par L N+ . Avec l'augmentation de L N+ , parce que le courant de fuite inverse est considérablement supprimé, le courant au point de fonctionnement statique et la SS moyenne sont également réduits. Le courant direct est beaucoup moins affecté que la fuite inverse, et le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) augmente avec l'augmentation en L N+ . Les figures 3c, d montrent la distribution de concentration de trous en 2 dimensions du B-TFET proposé avec L N+ égal à 2 nm et 80 nm, respectivement. Quand L N+ est égal à 2 nm, la concentration minimale de trous dans la région N + est supérieure à 10 17 cm −3 , tandis que lorsque L N+ est égal à 80 nm, la concentration minimale de trous est inférieure à 10 14 cm −3 . L'augmentation de la longueur de la région N + améliore sa capacité à empêcher les trous de traverser la région N + . En tant que porteur minoritaire hors équilibre dans la région N + , lorsque la région N + est plus longue, plus de trous seront recombinés avec des électrons avant de traverser la région N + , de sorte que l'augmentation de la longueur de la région N + peut également former un courant de fuite continu à polarisation inverse. Le SS moyen peut être réduit à 40,2 mV/déc, et le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) peut dépasser 10 10 .

un \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) caractéristiques ; b variation du SS et du rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) du B-TFET proposé avec différents L N+; Distribution de concentration de trous en 2 dimensions du B-TFET proposé sous polarisation inverse pour L N+ égal à (3) 2 nm et (4) 80 nm

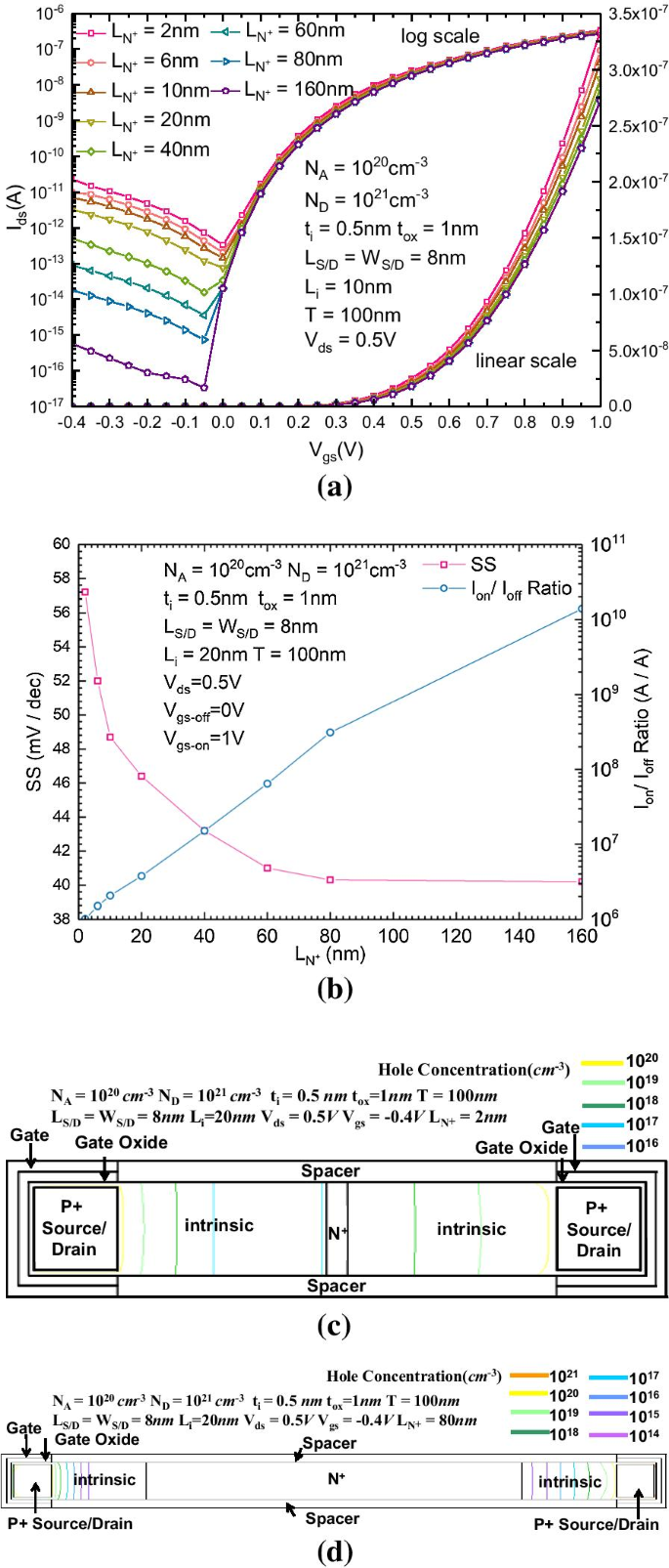

Les figures 4a, b montrent les caractéristiques de transfert \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) et les changements de SS et \(I_{{{ \text{on}}}}{-}I_{{{\text{off}}}}\) rapport du B-TFET proposé avec différents L je , respectivement. Le courant direct diminue avec l'augmentation de L je car la résistance de la région intrinsèque est proportionnelle à la longueur d'elle-même. Ensuite, pour maximiser le courant direct, la longueur de la région intrinsèque doit être minimisée. Cependant, la diminution de la longueur de la région intrinsèque améliore le champ électrique dans la région intrinsèque entre la région source P + et la région N + , de sorte que la courbure de la bande près de cette région est plus grande que la région intrinsèque près de l'électrode de drain, ce qui induit courant de fuite plus inversement polarisé. Les figures 4c, d montrent la distribution de potentiel bidimensionnelle biaisée en sens inverse du B-TFET proposé pour L je égal à 4 nm et 100 nm, respectivement. Pour le L le plus court je (4 nm), le champ électrique dans la région intrinsèque entre la région source P + et la région N + près de l'électrode source est beaucoup plus fort que celui dans la région intrinsèque entre la région drain P + et la région N + près du électrode de vidange. Ensuite, le courant de fuite reste presque constant, ce qui est indépendant du changement de tension de grille. La figure 4b montre que la plage de valeurs optimale de L je est d'environ 7 à 10 nm, où le SS diminue jusqu'à une valeur de vallée de 41 mV/déc et le \(I_{{{\text{on}}}}{-}I_{{{\text{off}}} }\) augmente jusqu'à une valeur maximale de près de 10 8 .

un \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) caractéristiques du B-TFET et b variation de SS et le rapport \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) avec différents \(L_{i}\); Distribution de potentiel bidimensionnelle biaisée en sens inverse du B-TFET proposé pour L i égal à c 20 nm et d 100 nm

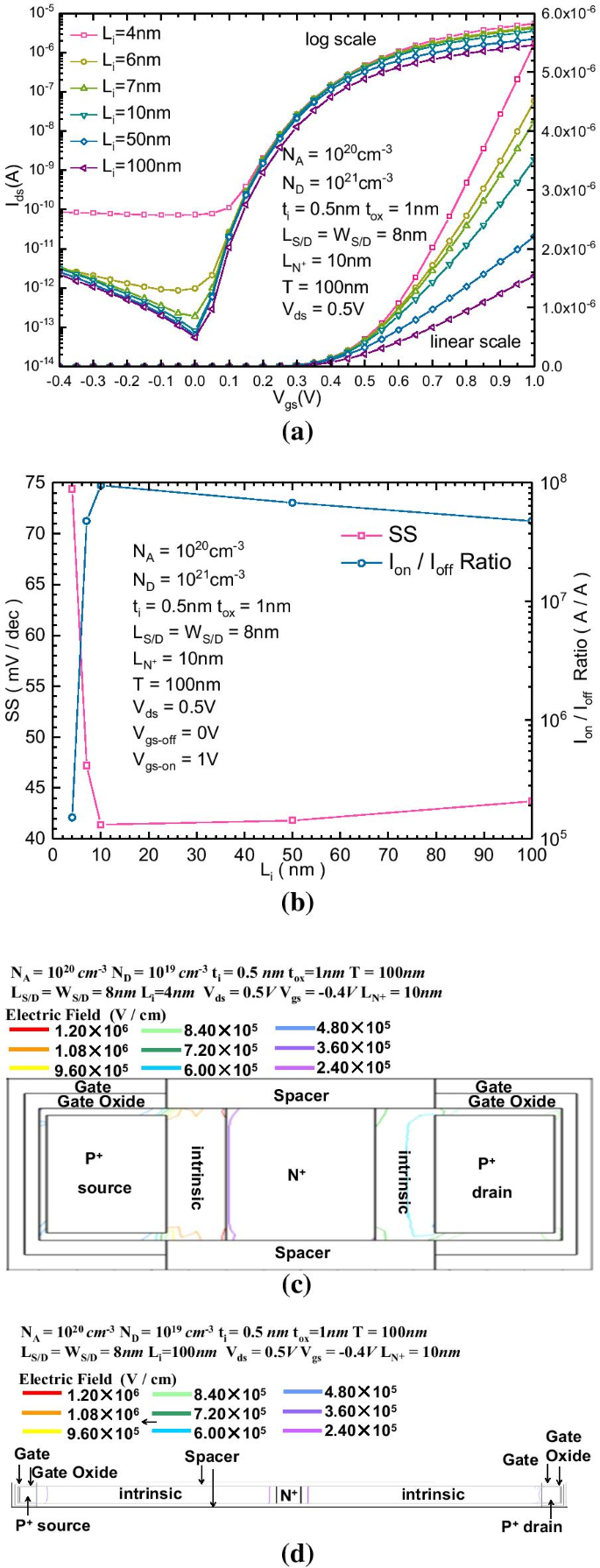

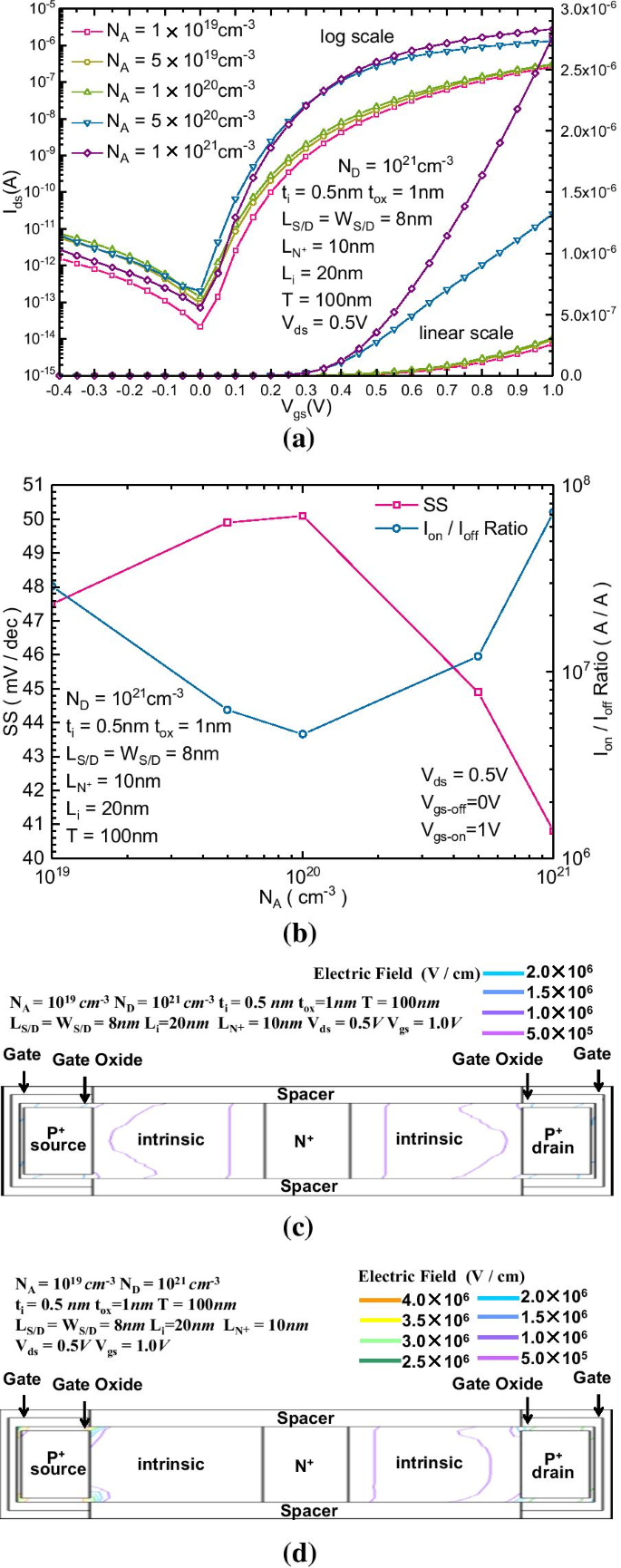

Les figures 5a, b montrent les caractéristiques de transfert \(I_{{{\text{ds}}}}{-}V_{{{\text{ds}}}}\) et le changement de SS et \(I_{{{ \text{on}}}}{-}I_{{{\text{off}}}}\) rapport du B-TFET proposé avec différents \(N_{A}\). La figure 5a montre qu'en augmentant la concentration de la région dopée P + , nous pouvons obtenir moins de SS et un courant direct plus important. Le courant de fuite polarisé en inverse n'est évidemment pas affecté par le changement de \(N_{A}\), mais le courant direct peut être augmenté avec l'augmentation de \(N_{A}\). Dans la figure 5b, les rapports SS et \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) peuvent être améliorés en augmentant \(N_{A }\). Les figures 5c, d montrent la distribution du champ électrique en 2 dimensions du B-TFET proposé avec \(N_{A}\) égal à 10 19 cm −3 et 10 21 cm −3 , respectivement. L'augmentation de \(N_{A}\) augmente le champ électrique dans la région intrinsèque du tunnel ; ensuite, davantage de paires électron-trou peuvent être générées par effet tunnel de bande à bande, ce qui améliore le courant direct du B-TFET proposé.

un \(I_{{{\text{ds}}}}{-}V_{{{\text{gs}}}}\) caractéristiques de transfert, b variation du rapport SS et \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) du B-TFET proposé avec différents \(N_{A} \). Distribution de champ électrique bidimensionnelle polarisée en inverse du B-TFET proposé pour \(N_{A}\) égal à (3) 10 19 cm −3 et (4) 10 21 cm −3

D'après la discussion ci-dessus, \(N_{D}\) et \(N_{A}\) doivent être définis sur la valeur maximale possible. La plage de valeurs optimale de L je est de 7 à 10 nm. Cependant, il existe un compromis entre la consommation d'énergie statique et L N+ . La figure 6 montre les caractéristiques de transfert \(I_{{{\text{ds}}}}{-}V_{{{\text{ds}}}}\) du B-TFET optimisé avec différents L N+ . L N+ peut être sélectionné en fonction de différentes exigences de conception de consommation d'énergie statique. En guise de compromis, pour s'assurer que le ratio \(I_{{{\text{on}}}}{-}I_{{{\text{off}}}}\) est supérieur à 10 8 , LN+ est recommandé d'être au-dessus de 20 nm. Le courant d'activation est augmenté à environ 6 × 10 –6 A, et la SS est réduite à 38 mV/déc.

\(I_{{{\text{ds}}}}{-}V_{{{\text{ds}}}}\) caractéristiques de transfert du B-TFET optimisé avec différents LN+

Conclusions

Dans cet article, les effets des paramètres structurels et du mécanisme interne d'un transistor bidirectionnel à effet de champ à effet tunnel symétrique et bidirectionnel contrôlé par grille bilatérale sont analysés. Les effets des paramètres clés tels que la concentration et la longueur de la région N + , la longueur de la région intrinsèque entre les régions P + et N + , et la concentration de la région P + ont été discutés en détail. Par rapport au TFET conventionnel, le B-TFET présente l'avantage d'une forte résistance au courant de fuite polarisé en inverse. Par la suite, de bonnes performances telles qu'un SS moyen inférieur et un ratio \(I_{{\text{on}}}}{-}I_{{{\text{off}}}}\) supérieur peuvent être obtenus. De plus, en raison de la symétrie structurelle et des caractéristiques de commutation source/drain interchangeables et bidirectionnelles, il est plus compatible avec le circuit CMOS.

Disponibilité des données et des matériaux

Nous avons inclus une déclaration de disponibilité des données et du matériel pour nous-mêmes et au nom de nos coauteurs sous la rubrique « Intérêts concurrents ». Toutes les données et le matériel disponibles sont des travaux originaux. Toutes les données ont été clairement fournies dans le manuscrit sans données supplémentaires ni documents à l'appui.

Abréviations

- L :

-

Toute la longueur de l'appareil proposé

- W :

-

Toute la largeur de l'appareil proposé

- L je :

-

Longueur de la région intrinsèque

- L N + :

-

Longueur du N + région

- L S / D :

-

Longueur du P + régions interchangeables source/drain

- W S / D :

-

Largeur du P + régions interchangeables source/drain

- \(T\) :

-

Épaisseur du corps en silicone

- \(t_{{{\text{ox}}}}\) :

-

Épaisseur de l'oxyde de grille

- \(t_{i}\) :

-

Épaisseur de la région tunnel intrinsèque entre la région S/D et l'oxyde de grille

- MOSFET :

-

Transistor à effet de champ semi-conducteur à oxyde métallique

- TFET :

-

Transistor à effet de champ tunnel

Nanomatériaux

- La diode Shockley

- Étude des premiers principes sur la stabilité et l'image STM du borophène

- Effet de la distribution de nanoparticules d'or dans le TiO2 sur les caractéristiques optiques et électriques des cellules solaires à colorant

- L'effet du plasma de contact hors équilibre sur les propriétés structurelles et magnétiques des spinelles Mn Х Fe3 − X О4

- Effet du traitement de recuit in situ sur la mobilité et la morphologie des transistors à effet de champ organiques à base de TIPS-Pentacène

- Étude expérimentale sur les caractéristiques d'écoulement et de transfert de chaleur de nanofluides TiO2-eau dans un tube cannelé en spirale

- Matrices de nanotubes TiO2 :fabriquées à l'aide d'un modèle Soft-Hard et de la dépendance de la taille des grains des performances d'émission de champ

- Étude sur la mémoire à commutation de résistance multi-niveaux et la phototension dépendante de l'état de la mémoire dans les jonctions Pt/Nd:SrTiO3

- Conception et ajustement de la fonction de travail du graphène via la taille, la modification, les défauts et le dopage :une étude théorique du premier principe