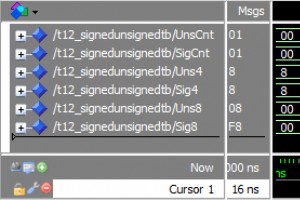

Les types signés et non signés en VHDL sont des vecteurs de bits, tout comme le type std_logic_vector. La différence est que si std_logic_vector est idéal pour implémenter des bus de données, il est inutile pour effectuer des opérations arithmétiques. Si vous essayez dajouter un nombre à un type st

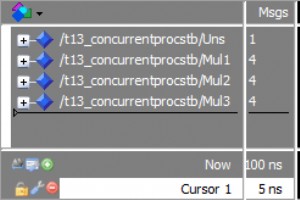

Une instruction concurrente en VHDL est une affectation de signal au sein de larchitecture, mais en dehors dune construction de processus normale. Linstruction simultanée est également appelée affectation simultanée ou processus simultané. Lorsque vous créez une instruction simultanée, vous créez e

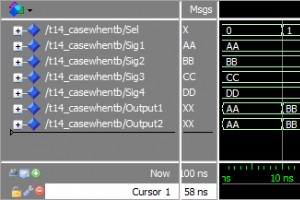

Linstruction Case-When obligera le programme à emprunter un chemin parmi plusieurs chemins différents, en fonction de la valeur dun signal, dune variable ou dune expression. Cest une alternative plus élégante à une instruction If-Then-Elsif-Else avec plusieurs Elsif. Dautres langages de programmati

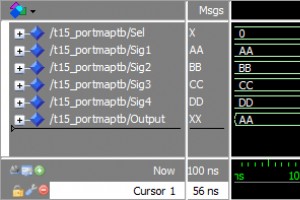

Un module est une unité autonome de code VHDL. Les modules communiquent avec le monde extérieur via lentité . Carte des ports est la partie de linstanciation du module où vous déclarez à quels signaux locaux les entrées et les sorties du module doivent être connectées. Dans les didacticiels précéde

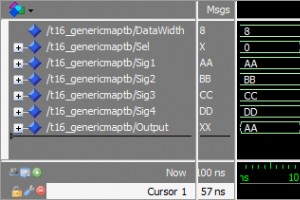

La création de modules est un excellent moyen de réutiliser le code, mais vous avez souvent besoin du même module avec de plus petites variations tout au long de votre conception. Cest à cela que servent les génériques et la carte générique. Il vous permet de rendre certaines parties du module confi

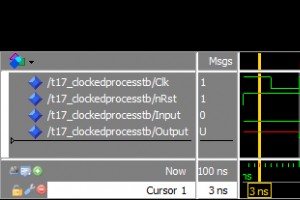

La grande majorité des conceptions VHDL utilise la logique cadencée , également appelée logique synchrone ou logique séquentielle . Un processus cadencé est déclenché uniquement par un signal dhorloge maître, pas lorsque lun des autres signaux dentrée change. Le bloc de construction de base de la l

Testez vos progrès avec ce quiz VHDL après avoir terminé les didacticiels 12 à 17 de la série de didacticiels VHDL de base ! Quelle affirmation est vraie concernant le type signé ? Ils peuvent représentent des valeurs plus élevées que les types non signés Si le le bit le plus à gauche est 1 l

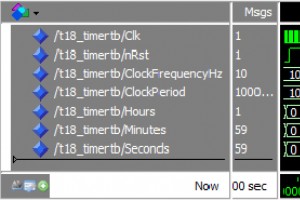

Dans les tutoriels précédents, nous avons utilisé le wait for déclaration pour retarder le temps dans la simulation. Mais quen est-il des modules de production ? Le wait for la déclaration ne peut pas être utilisée pour cela. Cela ne fonctionne quen simulation car nous ne pouvons pas simplement dire

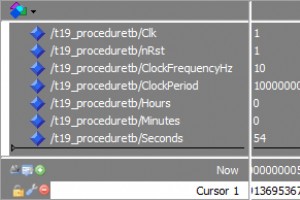

Une procédure est un type de sous-programme en VHDL qui peut nous aider à éviter de répéter du code. Parfois, le besoin se fait sentir deffectuer des opérations identiques à plusieurs endroits tout au long de la conception. Bien que la création dun module puisse être exagérée pour des opérations min

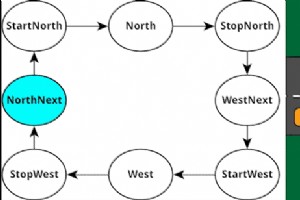

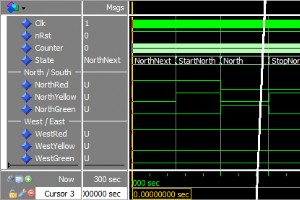

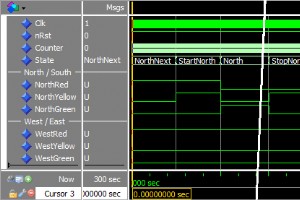

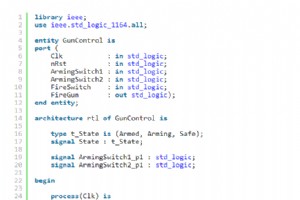

Une machine à états finis (FSM) est un mécanisme dont la sortie dépend non seulement de létat actuel de lentrée, mais également des valeurs dentrée et de sortie passées. Chaque fois que vous avez besoin de créer une sorte dalgorithme dépendant du temps en VHDL, ou si vous êtes confronté au problème

Les fonctions sont des sous-programmes en VHDL qui peuvent être utilisés pour implémenter des algorithmes fréquemment utilisés. Une fonction prend zéro ou plusieurs valeurs dentrée et renvoie toujours une valeur. En plus de la valeur de retour, ce qui distingue une fonction dune procédure, cest quel

Une fonction impure peut lire ou écrire nimporte quel signal dans sa portée, y compris ceux qui ne figurent pas dans la liste des paramètres. On dit que la fonction a des effets secondaires . Ce que nous entendons par effets secondaires, cest quil nest pas garanti que la fonction renvoie la même va

Il est possible de piloter des signaux externes à partir dune procédure. Tant que le signal est dans le périmètre de la procédure, il est accessible en lecture ou en écriture, même sil nest pas listé dans la liste des paramètres. Les procédures déclarées dans la région déclarative de larchitecture

Testez vos progrès avec ce quiz VHDL après avoir terminé la partie 4 de la série de didacticiels VHDL de base ! Comment mesurer le temps réel en VHDL ? En utilisant une instruction attendre 1 ns En comptant périodes dhorloge En exploitant délai de propagation Corriger! Mauvais! - Quelle

La liste chaînée est une structure de données dynamique. Une liste chaînée peut être utilisée lorsque le nombre total déléments nest pas connu à lavance. Il grandit et rétrécit en mémoire, par rapport au nombre déléments quil contient. Les listes chaînées sont plus facilement implémentées à laide d

Un banc dessai dauto-vérification est un programme VHDL qui vérifie lexactitude de lappareil testé (DUT) sans compter sur un opérateur pour inspecter manuellement la sortie. Le banc de test dauto-vérification fonctionne entièrement de lui-même et affiche un message OK ou Échec à la fin. Chaque modu

Un banc de test interactif est une configuration de simulateur dans laquelle lentrée de lappareil sous test (DUT) est fournie par un opérateur pendant que le banc de test est en cours dexécution. Le plus souvent, cela signifie que vous entrez des commandes dans la console du simulateur pour fournir

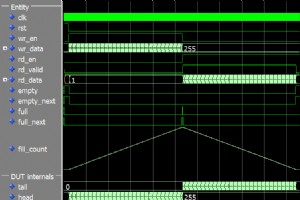

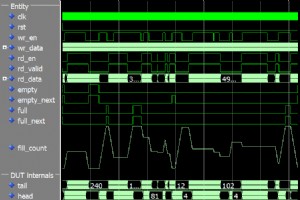

Les tampons circulaires sont des constructions populaires pour créer des files dattente dans les langages de programmation séquentiels, mais ils peuvent également être implémentés dans le matériel. Dans cet article, nous allons créer un tampon circulaire en VHDL pour implémenter un FIFO dans la RAM

La vérification aléatoire contrainte est une stratégie de banc dessai qui repose sur la génération de transactions pseudo-aléatoires pour lappareil sous test (DUT). Lobjectif est datteindre une couverture fonctionnelle dun certain nombre dévénements prédéfinis grâce à une interaction aléatoire avec

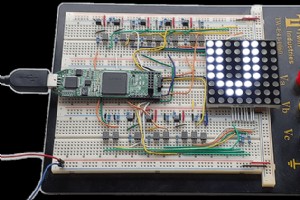

Je suis ravi dannoncer que le cours VHDL et FPGA sur lequel je travaille depuis six mois commence à se terminer. Le cours est actuellement en version bêta et je prévois de le lancer pour la première fois cet automne. À qui sadresse la formation FPGA ? Le cours FPGA est destiné au développeur qui co

VHDL