Comment utiliser l'instanciation de Port Map dans VHDL

Un module est une unité autonome de code VHDL. Les modules communiquent avec le monde extérieur via l'entité . Carte des ports est la partie de l'instanciation du module où vous déclarez à quels signaux locaux les entrées et les sorties du module doivent être connectées.

Dans les didacticiels précédents de cette série, nous avons écrit tout notre code dans le fichier VHDL principal, mais normalement nous ne le ferions pas. Nous créons une logique dans le but de l'utiliser dans une conception FPGA ou ASIC, pas pour le simulateur.

Un module VHDL créé pour s'exécuter dans un simulateur n'a généralement pas de signaux d'entrée ou de sortie. Il est entièrement autonome. C'est pourquoi l'entité de nos conceptions est vide. Il n'y a rien eu entre le entity balise et le end entity; balise.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

Un module sans aucun signal d'entrée ou de sortie ne peut pas être utilisé dans une conception réelle. Son seul but est de nous permettre d'exécuter du code VHDL dans un simulateur. C'est pourquoi on l'appelle un testbench . Pour simuler un module avec des signaux d'entrée et de sortie, nous devons instancier dans un banc d'essai.

Les modules et bancs de test viennent souvent par paires et sont stockés dans des fichiers différents. Un schéma de nommage courant consiste à appeler le testbench le nom du module avec "Tb" ajouté, et à nommer l'architecture "sim". Si le module s'appelle "MyModule", le testbench s'appellera "MyModuleTb". Par conséquent, les noms de fichiers deviennent "MyModuleTb.vhd" et "MyModule.vhd".

Avec l'aide du code de testbench, nous pouvons vérifier que le module fonctionne correctement dans un environnement de simulation. Le module testé est généralement appelé dispositif testé (DUT).

Les modules peuvent également être instanciés dans d'autres modules. Le partitionnement du code en modules lui permet d'être instancié plusieurs fois. Vous pouvez créer plusieurs instances d'un module dans la même conception, et il peut être réutilisé dans de nombreuses conceptions.

La syntaxe d'une entité avec un port en VHDL est :entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

La syntaxe pour instancier un tel module dans un autre fichier VHDL est :<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

Le <label> peut être n'importe quel nom, et il apparaîtra dans la fenêtre de hiérarchie de ModelSim. Le <library_name> pour un module est défini dans le simulateur, pas dans le code VHDL. Par défaut, chaque module est compilé dans le work bibliothèque. Le <entity_name> et <architecture_name> doit correspondre au module dont nous créons une instance. Enfin, chacun des signaux d'entité doit être mappé à un nom de signal local.

Il existe d'autres façons d'instancier un module en VHDL, mais c'est la syntaxe de base pour l'instanciation explicite.

Exercice

Dans ce tutoriel vidéo, nous allons apprendre à créer et instancier un module en VHDL :

Le code final pour le MUX testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

Le code final pour le module MUX :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

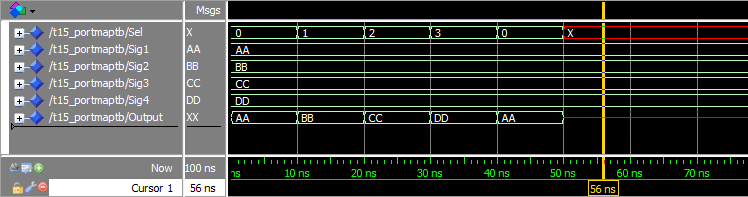

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

Analyse

Comme nous pouvons le voir sur la forme d'onde, le module multiplexeur (MUX) fonctionne comme prévu. La forme d'onde est identique à celle du tutoriel précédent que nous avons créé sans utiliser de modules.

Il y a maintenant une séparation claire entre le module de conception et le banc d'essai. Le module contenant le MUX est ce que nous avons l'intention d'utiliser dans une conception, et le seul but du testbench est de nous permettre de l'exécuter dans un simulateur. Il y a un processus dans le testbench qui utilise wait déclarations pour créer des retards artificiels dans la simulation. Le module de conception n'a aucune notion de temps, il réagit uniquement aux stimuli externes.

Nous avons nommé l'architecture du banc de test sim , pour simuler. L'architecture du module de conception a été nommée rtl , qui signifie niveau de transfert de registre. Ce ne sont que des conventions de nommage. Lorsque vous voyez un fichier avec un tel nom, vous savez immédiatement s'il s'agit d'un testbench ou d'un module de conception. Différentes entreprises peuvent avoir des conventions de dénomination différentes.

À emporter

- Les signaux d'entrée et de sortie sont spécifiés dans l'entité d'un module

- Un module sans signaux d'entrée/sortie est appelé un testbench , et il ne peut être utilisé que dans un simulateur

- Un module avec des signaux d'entrée/sortie ne peut généralement pas être exécuté directement dans un simulateur

Aller au tutoriel suivant »

VHDL

- Comment utilisons-nous le molybdène?

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai piloté par Tcl pour un module de verrouillage de code VHDL

- Comment arrêter la simulation dans un testbench VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment générer des nombres aléatoires en VHDL

- Comment utiliser une procédure dans un processus en VHDL

- Comment utiliser une fonction en VHDL

- Comment utiliser une meuleuse de coupe