Comment arrêter la simulation dans un testbench VHDL

Comment arrêter le simulateur VHDL lorsque la simulation est terminée ? Il existe plusieurs façons de le faire. Dans cet article, nous examinerons les moyens les plus courants de mettre fin à une exécution réussie du testbench.

Le code VHDL présenté ici est universel et devrait fonctionner dans n'importe quel simulateur VHDL compatible. Pour les méthodes impliquant Tcl, je listerai les commandes des simulateurs ModelSim et Vivado.

Vous pouvez télécharger un exemple de projet avec les quatre bancs de test différents de cet article si vous avez installé ModelSim. Entrez votre adresse e-mail dans le formulaire ci-dessous pour recevoir le fichier Zip !

Utiliser finir procédure

La finition VHDL est mon moyen préféré d'arrêter un testbench VHDL qui se termine sans erreur. Vous devez importer "finish" du package STD.ENV, et vous devez compiler le testbench en VHDL-2008 ou plus récent pour l'utiliser.

Le code ci-dessous termine la simulation lorsque nous atteignons la dernière ligne du processus du séquenceur de testbench.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

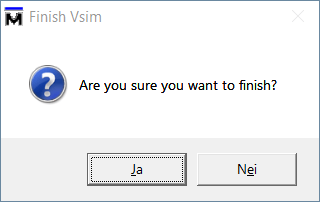

Notez que terminer quitte la simulation par défaut. Si vous exécutez ModelSim dans la version GUI, une fenêtre contextuelle apparaîtra indiquant "Etes-vous sûr de vouloir terminer?". Si vous cliquez sur Oui, ModelSim va se fermer.

Ce n'est probablement pas ce que vous voulez. Heureusement, nous pouvons empêcher ce comportement en ajoutant l'option "-onfinish stop" à la commande vsim, comme indiqué ci-dessous. Ce faisant, la finition procédure se comportera de la même manière que le stop procédure dont nous parlerons dans la prochaine section de cet article.

vsim -onfinish stop work.using_finish_tb

Un avantage d'utiliser finish est que vous pouvez utiliser le comportement par défaut lors de la simulation en mode batch. Si vous utilisez des scripts pour démarrer la simulation, vous souhaitez rendre le contrôle au script appelant une fois la simulation terminée.

L'exemple ci-dessous montre un testbench utilisant le finish procédure démarrée en mode batch ModelSim sous Linux. Une fois le testbench terminé, le simulateur se ferme et à la dernière ligne, nous sommes de retour dans le shell Linux.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

La finition VHDL La procédure est définie dans le package ENV standard. Comme nous pouvons le voir dans le code ci-dessous, il existe deux versions surchargées. Il y a la version sans aucun paramètre, qui est celle que j'utilise toujours, et il y en a une autre qui prend un entier de statut comme entrée constante.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

On pourrait penser que l'entier de statut devient le code de sortie lorsqu'il est appelé depuis un shell Linux, mais ce n'est pas le cas, du moins pas avec ModelSim. Le problème avec l'utilisation de ce code d'état est que ce qu'il fait dépend du simulateur. Le libellé de la norme VHDL-2008 est "la valeur du paramètre STATUS peut être utilisée d'une manière définie par l'implémentation par le simulateur hôte ".

Cependant, vous pouvez contrôler la valeur du code de sortie Linux dans ModelSim en utilisant la commande Tcl exit -code <value> , mais c'est une autre histoire.

Utiliser l'arrêt procédure

Le VHDL arrête procédure provoque une pause de la simulation. Cela peut être utile si vous souhaitez examiner manuellement les valeurs du signal ou même continuer la simulation ultérieurement. Le simulateur le traite comme un point d'arrêt.

L'exemple ci-dessous montre comment importer et utiliser le stop procédure.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Un problème avec l'utilisation de stop dans les configurations basées sur des scripts, c'est qu'il ne quitte pas la simulation. Au lieu de rendre le contrôle à l'appelant, ModelSim ouvre un shell de commande Tcl, provoquant le blocage indéfini du script appelant.

La liste ci-dessous montre la sortie de l'exécution du testbench qui utilise le stop procédure en mode batch. Après l'arrêt de la simulation, nous sommes toujours dans ModelSim. Pour sortir du shell Tcl, il faudrait taper "exit".

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Tout comme la finition procédure, arrêter nécessite VHDL-2008 ou plus récent. Comme indiqué ci-dessous, une version surchargée de la procédure existe. Il prend une valeur d'état entière, mais le comportement varie selon les simulateurs.

procedure STOP (STATUS: INTEGER); procedure STOP;

Utiliser l'affirmation mot-clé

Un moyen sûr et universel d'arrêter un testbench VHDL consiste à créer un échec d'assertion. C'est la première façon que quelqu'un m'a appris à terminer la simulation lorsque j'apprenais le VHDL à l'université.

Aucune importation supplémentaire n'est nécessaire et cela fonctionne dans toutes les versions VHDL. Assurez-vous simplement d'utiliser le niveau de gravité échec , comme illustré dans l'exemple ci-dessous.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

Et pourquoi est-ce que je déteste cette façon d'arrêter une simulation réussie ?

Tout d'abord, il est étrange et déroutant de voir l'impression de l'exemple ci-dessus :

# ** Failure: Test: OK

Il dit que c'est un "échec", mais le test est "OK" en même temps. C'est parce que le assert est censée indiquer une condition d'erreur et non la réussite de la simulation.

L'autre problème ennuyeux auquel je peux penser est qu'il devient difficile de savoir par programmation si la simulation a réussi.

La plupart des professionnels du VHDL démarrent les simulations à partir d'un script à un moment donné, par exemple, dans le cadre d'un schéma de test de régression plus large. Si le testbench s'arrête également à un échec d'assertion alors qu'il n'y a rien de mal, nous ne pouvons pas l'utiliser comme marqueur pour déterminer la santé du module VHDL.

Utiliser Tcl

La dernière méthode d'arrêt de la simulation que je vais couvrir consiste à utiliser Tcl en combinaison avec VHDL. Au lieu d'arrêter le testbench à partir du fichier VHDL, nous définissons un signal VHDL régulier lorsqu'il est temps de s'arrêter. Et au préalable, nous configurons le simulateur pour écouter un changement sur ce signal de déclenchement.

Lire aussi :

Pourquoi vous devez apprendre Tcl

Regardez l'exemple ci-dessous, qui définit un signal nommé stop_condition lorsque tous les cas de test sont terminés.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

Vous pouvez mettre n'importe quel processus de banc d'essai qui a fait son travail en veille avec une seule attente déclaration avant le processus de fin étiquette. Cela l'empêchera de redémarrer. Le code Tcl pour arrêter réellement la simulation diffère d'un simulateur à l'autre.

Dans ModelSim

Ce que nous voulons, c'est arrêter le testbench lorsque la condition d'arrêt Le signal VHDL devient vrai . Nous pouvons le faire en configurant un rappel dans Tcl avant d'exécuter le testbench VHDL.

Selon le manuel de référence des commandes ModelSim, nous pouvons y parvenir en utilisant le Tcl lorsque commande. Dans le code Tcl ci-dessous, nous enregistrons un tel rappel, puis nous démarrons le simulateur en utilisant run -all .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Notez que le code entre les accolades ne s'exécutera pas tant que le rappel n'aura pas eu lieu. Lorsque le code VHDL modifie la stop_condition signal à vrai , le simulateur s'arrêtera et exécutera les deux lignes. Dans l'exemple, nous arrêtons la simulation et affichons « Test :OK » sur la console. Vous pouvez également avoir une sortie Tcl commande là-dedans, qui quitterait le simulateur, tout comme le VHDL finish procédure.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

La liste ci-dessus montre la sortie imprimée sur la console ModelSim lorsque le testbench Tcl / VHDL est terminé. Si vous voulez l'essayer sur votre ordinateur, utilisez le formulaire ci-dessous pour télécharger le projet ModelSim avec tous les exemples de cet article !

À Vivado

Selon le Vivado Design Suite Tcl Command Reference Guide, nous pouvons enregistrer un rappel Tcl en utilisant la add_condition commande. Le code ci-dessous montre l'équivalent Xilinx pour la version ModelSim discutée précédemment.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

Le -notrace Le commutateur empêche les lignes de code de la fonction de rappel d'être renvoyées au terminal lors de leur exécution. Je préfère ne pas avoir d'encombrement supplémentaire dans la console.

La liste ci-dessous montre un extrait de la simulation exécutée dans la console du simulateur Vivado.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Réflexions finales

Comme vous l'avez vu, il existe de nombreuses façons de terminer une simulation VHDL. Cependant, le seul que j'utilise est la finition VHDL-2008 procédure.

Tous les simulateurs prennent désormais en charge VHDL-2008, et vous n'avez pas besoin de compiler le code RTL en 2008, seulement le testbench. La finition est la méthode la plus portable, et elle vous permet d'arrêter le simulateur lors de l'exécution en mode graphique, ou de quitter lors de l'exécution en mode batch. Exactement le comportement que je souhaite la plupart du temps.

Mais il y a des avantages aux méthodes Tcl qui sortent du cadre de cet article. Lorsque vous avez mis le simulateur en pause dans le rappel Tcl, vous pouvez faire bien plus que simplement arrêter le simulateur et quitter. Vous pouvez examiner les signaux VHDL et même les manipuler à l'aide de Tcl, pendant que vous êtes dans le rappel. C'est la vérification en utilisant Tcl.

VHDL

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai piloté par Tcl pour un module de verrouillage de code VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment générer des nombres aléatoires en VHDL

- Banc de test interactif utilisant Tcl

- Comment créer un banc d'essai d'auto-vérification

- Comment créer une liste chaînée en VHDL

- Comment utiliser une procédure dans un processus en VHDL

- Comment arrêter la rouille