Banc de test interactif utilisant Tcl

Un banc de test interactif est une configuration de simulateur dans laquelle l'entrée de l'appareil sous test (DUT) est fournie par un opérateur pendant que le banc de test est en cours d'exécution. Le plus souvent, cela signifie que vous entrez des commandes dans la console du simulateur pour fournir un stimulus au DUT.

Bien que vous deviez toujours créer un banc d'essai auto-vérifié, un banc d'essai interactif peut être un bon complément. Il est plus facile d'effectuer des tests ad hoc avec un banc de test interactif à portée de main que de modifier le code du banc de test d'auto-vérification.

Souvent, vous découvrirez des problèmes dans le laboratoire que vous voudrez essayer dans le banc d'essai. Avec un banc de test interactif, il peut être aussi simple que de taper la séquence d'entrée qui a été observée pour reproduire le comportement indésirable dans le simulateur.

Tcl interagit avec VHDL

La plupart des simulateurs VHDL utilisent Tcl comme langage de console. Les simulateurs ont un tas de commandes spécifiques au fournisseur, mais la bonne nouvelle est qu'elles peuvent être traitées comme n'importe quelle autre commande Tcl. Vous pouvez utiliser Tcl pour créer des scripts complexes, principalement portables, pour gérer et prendre en charge vos bancs de test VHDL.

Modifier les signaux VHDL de Tcl

Pour interagir avec VHDL, nous devons trouver la commande permettant de modifier une valeur de signal. Dans ModelSim, il s'agit de la commande "forcer". Comme spécifié dans le document de référence de la commande, le synopsis de la commande est :

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] Le commutateur que vous souhaitez utiliser est le drapeau "-deposit". Cela modifie instantanément la valeur du signal VHDL, mais permet à un autre pilote VHDL ou Tcl de le modifier ultérieurement.

En ignorant les options que nous n'utilisons pas, le synopsis simplifié ressemble à ceci :

force -deposit <signal_name> <value>

Le déclencheur VHDL

Maintenant que nous savons comment contrôler les signaux VHDL de Tcl, nous devons créer une sorte de processus récepteur dans notre banc de test VHDL. Le code ci-dessous montre un exemple minimal d'un tel banc d'essai.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

Le processus se réveillera lorsque le trigger le signal passe de quelque chose à '1' . Il affichera « Déclenché ! à la console lorsque cela se produit, nous permettant de tester le concept de contrôle des processus VHDL depuis Tcl.

Je n'ai fait que la console ModelSim. Les commandes émises, ainsi que la sortie, peuvent être consultées dans la transcription ci-dessous.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

J'ai exécuté le testbench pendant 10 nanosecondes après le démarrage de la simulation.

Ensuite, j'ai forcé le trigger signaler à '1' . Sur la ligne suivante, j'attends 0 nanosecondes. Le but est de créer un cycle delta. Je veux que le processus soit déclenché, mais je ne veux pas que le temps de simulation passe.

Enfin, je force le trigger renvoyer un signal à '0' avant de continuer le testbench.

Nous pouvons voir que le processus VHDL s'est réveillé après la ligne "run 0 ns" et a imprimé "Triggered!" à la console.

Lecture des valeurs de signal VHDL en tcl

Pour lire les valeurs de signal dans ModelSim, vous pouvez utiliser la commande "examiner". On peut par exemple lire la valeur du trigger signal en utilisant cette commande dans la console ModelSim :

VSIM 6> examine /trigger # 0

Vous voudriez assigner la valeur à une variable Tcl lors de l'utilisation de "examine" dans un script. Essayons ceci dans la console ModelSim :

VSIM 7> set triggerVal [examine /trigger] # 0

Ensuite, nous pouvons par exemple imprimer la variable en utilisant la commande Tcl "puts" :

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

Arrêter le simulateur après chaque test

Le moyen le plus simple d'exécuter le test suffisamment longtemps pour que le DUT réagisse consiste simplement à exécuter le simulateur pendant une durée fixe. Par exemple, si le DUT doit réagir après deux cycles d'horloge et que la période d'horloge est de 10 nanosecondes, nous utiliserons la commande "run 20 ns" dans notre script Tcl.

Si le DUT n'a pas de temps de réaction fixe, une assertion VHDL peut être utilisée pour arrêter la simulation et passer le contrôle à une fonction de rappel Tcl. Dans ModelSim, cela reviendrait à définir un point d'arrêt à partir de votre script Tcl en utilisant la commande "when" :

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] Vous devrez également définir une fonction de rappel "onBreak" dans Tcl qui sera exécutée lorsque le point d'arrêt est atteint. La fonction "onBreak" est spécifiée dans la référence de commande ModelSim.

Les inconvénients des tests pilotés par Tcl

Il y a des inconvénients à utiliser des bancs de test qui reposent fortement sur des scripts Tcl. Les plus évidents sont les problèmes de vitesse et de portabilité.

Les bancs de test pilotés par Tcl fonctionnent en démarrant et en arrêtant le simulateur plusieurs fois pour interagir avec le code VHDL. Démarrer et arrêter la simulation pour exécuter une fonction Tcl entre les deux prend plus de temps que d'exécuter un banc de test VHDL en continu. Alors que Tcl est un langage interprété, VHDL est compilé dans le simulateur et s'exécute beaucoup plus rapidement que Tcl.

Bien que Tcl soit portable sur d'autres simulateurs, les commandes spécifiques au simulateur que vous devrez utiliser ne le sont pas. Même si vous trouvez les commandes équivalentes dans l'autre simulateur, elles peuvent fonctionner différemment. Les fournisseurs de simulateurs établissent leur propre ensemble de règles pour les commandes qu'ils prennent en charge. Par conséquent, un banc de test piloté par Tcl doit être considéré comme moins portable qu'un banc de test VHDL pur.

Nouveau cours VHDL et FPGA

* Je suis en train de créer un nouveau cours VHDL et FPGA qui plongera de manière approfondie dans les bancs d'essai. Vous apprendrez à créer une conception FPGA à partir de zéro. Après avoir terminé le cours, vous saurez comment créer des bancs de test auto-vérifiés et comment réutiliser le code pour créer un banc de test interactif.

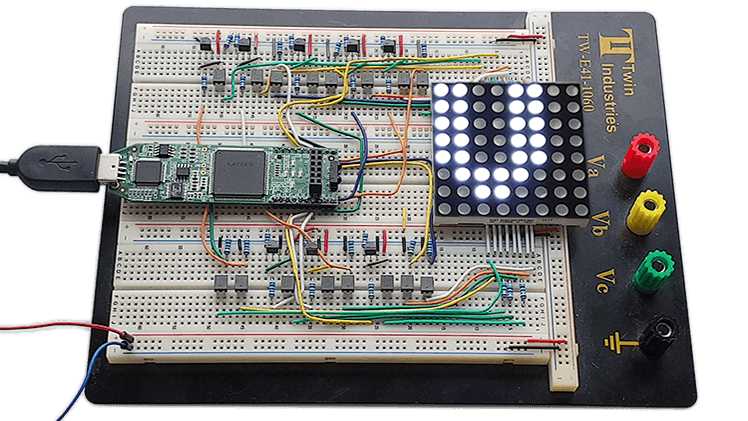

* Mis à jour le 12 octobre 2020 : J'ai terminé le cours. Cliquez sur l'image ci-dessous pour en savoir plus.

Le produit que nous allons créer est un module contrôleur LED à matrice de points. Nous utiliserons la carte de développement Lattice iCEstick à 49 $. En fin de compte, nous mettrons en œuvre la conception sur une planche à pain. Vous pourrez taper sur le clavier de votre ordinateur et les caractères apparaîtront sur l'écran LED à matrice de points contrôlé par le FPGA.

En savoir plus sur le cours Dot Matrix VHDL et FPGA ici !

Ouvre :

À déterminer .

VHDL

- Tutoriel - Introduction au VHDL

- Exemples de conversions VHDL

- Instruction de procédure - Exemple VHDL

- Enregistrements - Exemple VHDL

- C# en utilisant

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai d'auto-vérification

- Projecteur laser interactif utilisant des capteurs Zigbee

- Utiliser une fraiseuse comme tour