Comment utiliser une instruction Case-When en VHDL

L'instruction Case-When obligera le programme à emprunter un chemin parmi plusieurs chemins différents, en fonction de la valeur d'un signal, d'une variable ou d'une expression. C'est une alternative plus élégante à une instruction If-Then-Elsif-Else avec plusieurs Elsif.

D'autres langages de programmation ont des constructions similaires, en utilisant des mots-clés tels qu'un commutateur , cas , ou sélectionnez . Entre autres choses, les instructions Case-When sont couramment utilisées pour implémenter des multiplexeurs en VHDL. Continuez à lire ou regardez la vidéo pour découvrir comment !

Cet article de blog fait partie de la série de didacticiels VHDL de base.

La syntaxe de base de l'instruction Case-When est :case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case;

Le <expression> est généralement une variable ou un signal. L'instruction Case peut contenir plusieurs when choix, mais un seul choix sera sélectionné.

Le <choice> peut être une valeur unique comme "11" :when "11" =>

Ou cela peut être une plage comme 5 to 10 :when 5 to 10 =>

Il peut contenir plusieurs valeurs comme 1|3|5 :when 1|3|5 =>

Et surtout, le others choix. Il est sélectionné chaque fois qu'aucun autre choix n'a été trouvé :when others =>

Le others le choix est équivalent au Else branche dans l'instruction If-Then-Elsif-Else.

Exercice

Dans ce didacticiel vidéo, nous allons apprendre à créer un multiplexeur à l'aide de l'instruction Case-When en VHDL :

Le code final que nous avons créé dans ce tutoriel :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

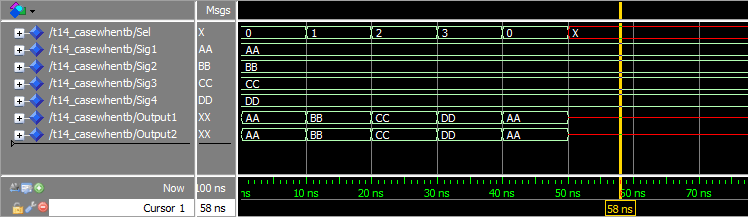

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

La sortie vers la console du simulateur lorsque nous avons appuyé sur le bouton d'exécution dans ModelSim :

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

Analyse

Tout d'abord, nous avons créé un processus utilisant If-Then-Elsif-Else qui transmettrait l'un des signaux Sig1 , Sig2 , Sig3 , ou Sig4 , basé sur la valeur du signal sélecteur Sel .

Ensuite, nous avons créé un processus qui faisait exactement la même chose, en utilisant l'instruction Case-When. Nous pouvons voir à partir de la forme d'onde que les signaux de sortie des deux processus, Output1 et Output2 , se comporte exactement de la même façon.

Dans notre exemple, le Sel signal n'a que quatre valeurs légales. Mais s'il y avait eu un plus grand nombre de possibilités, nous pouvons facilement voir que l'instruction Case-When peut aider à rendre le code plus lisible. C'est la manière préférée de créer un tel composant par la plupart des concepteurs VHDL.

Compréhension du multiplexeur était le point bonus de cet exercice. Les multiplexeurs, ou MUX en abrégé, sont des composants centraux de la conception numérique. Il s'agit simplement d'un commutateur qui sélectionne l'une des nombreuses entrées et la transmet à la sortie.

Voici une illustration de la façon dont notre MUX transmet le signal d'entrée sélectionné :

Nous avons utilisé le others clause pour attraper toutes les valeurs de Sel qui n'étaient ni des uns ni des zéros. Comme nous l'avons appris dans le tutoriel std_logic, ces signaux peuvent avoir un certain nombre de valeurs qui ne sont pas '0' ou '1' . C'est une bonne pratique de conception de traiter ces valeurs en affichant 'X' . Cela indique une valeur inconnue sur ce signal, et elle sera également visible dans la logique en aval.

Nous pouvons voir sur la forme d'onde que lorsque le Sel le signal est devenu rouge, Output1 et Output2 également changé en "XX" . C'est when others => en action.

De plus, la sortie de la console dans ModelSim affiche un avertissement à cause du Sel le signal étant réglé sur "UU" . Les messages "** Avertissement :NUMERIC_STD."=" : métavaleur détectée, renvoyant FALSE" apparaissent à 50 ns de temps de simulation, ce qui correspond exactement au moment où les signaux deviennent rouges.

À emporter

- Case-When peut être utilisé à la place de plusieurs instructions If-Then-Elsif

- Le

when others =>peut être utilisé pour implémenter un choix par défaut - Les multiplexeurs sont de préférence créés à l'aide d'instructions Case-When

Aller au tutoriel suivant »

VHDL

- Instruction de procédure - Exemple VHDL

- Comment utilisons-nous le molybdène?

- Comment créer une liste de chaînes en VHDL

- Comment arrêter la simulation dans un testbench VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment générer des nombres aléatoires en VHDL

- Comment utiliser une procédure dans un processus en VHDL

- Comment utiliser une fonction en VHDL

- Comment utiliser une meuleuse de coupe