Comment créer une instruction simultanée en VHDL

Une instruction concurrente en VHDL est une affectation de signal au sein de l'architecture, mais en dehors d'une construction de processus normale. L'instruction simultanée est également appelée affectation simultanée ou processus simultané.

Lorsque vous créez une instruction simultanée, vous créez en fait un processus avec certaines caractéristiques clairement définies. Les instructions simultanées sont toujours équivalentes à un processus utilisant une liste de sensibilité, où tous les signaux à droite de l'opérateur d'affectation de signal sont sur la liste de sensibilité.

Ces processus de notation abrégée sont utiles lorsque vous souhaitez créer une logique simple qui aboutit à l'affectation d'un seul signal. Au lieu de taper une construction de processus complète avec des listes de sensibilité et tout cela, vous pouvez simplement affecter le signal cible directement dans l'architecture.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

Lorsqu'il est utilisé correctement, l'intention du code sera toujours assez claire. Inutile de créer un processus pour chaque bit que vous souhaitez inverser.

Exercice

Dans cette vidéo, nous apprenons à créer une déclaration simultanée :

Le code final que nous avons créé dans ce tutoriel :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

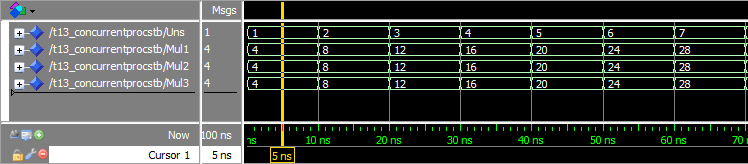

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

Analyse

Nous pouvons voir sur la forme d'onde que Mul1 , Mul2 , et Mul3 comporte exactement la même chose. En effet, l'instruction concurrente et les deux processus que nous avons créés sont équivalents.

Une instruction concurrente fonctionne exactement comme un processus. Tous les signaux à droite du <= sont automatiquement ajoutés à la liste de sensibilité. Cela signifie que le signal à gauche du <= sera mis à jour chaque fois que l'un des signaux évalués change.

Il existe de nombreuses façons de multiplier des nombres en VHDL. Dans cet exercice, nous avons multiplié le Uns signal par 4, en utilisant le décalage de bits. Tous nos signaux sont de unsigned type, ce qui signifie qu'ils sont interprétés par des nombres. Ajouter un 0 à droite d'un nombre binaire revient à le multiplier par 2.

Voici une illustration de ce qui se passe au niveau du curseur dans la forme d'onde :

À emporter

- Une instruction simultanée est une affectation de signal directement dans la région de l'architecture

- Les instructions simultanées sont équivalentes à un processus avec tous les signaux évalués sur la liste de sensibilité

Aller au tutoriel suivant »

VHDL

- Instruction de procédure - Exemple VHDL

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai piloté par Tcl pour un module de verrouillage de code VHDL

- Comment arrêter la simulation dans un testbench VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment créer un tampon circulaire FIFO en VHDL

- Comment créer un banc d'essai d'auto-vérification

- Comment créer une liste chaînée en VHDL

- Comment utiliser une procédure dans un processus en VHDL