Comment utiliser signé et non signé en VHDL

Les types signés et non signés en VHDL sont des vecteurs de bits, tout comme le type std_logic_vector. La différence est que si std_logic_vector est idéal pour implémenter des bus de données, il est inutile pour effectuer des opérations arithmétiques.

Si vous essayez d'ajouter un nombre à un type std_logic_vector, ModelSim produira l'erreur de compilation :Aucune entrée possible pour l'opérateur infixe "+". C'est parce que le compilateur ne sait pas comment interpréter cette collection de bits qu'est le vecteur.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

Nous devons déclarer notre vecteur comme signé ou non signé pour que le compilateur le traite comme un nombre.

La syntaxe pour déclarer les signaux signés et non signés est :signal <name> : signed(<N-bits> downto 0) := <initial_value>;

signal <name> : unsigned(<N-bits> downto 0) := <initial_value>;

Tout comme avec std_logic_vector, les plages peuvent être to ou downto n'importe quelle gamme. Mais déclarer des signaux avec d'autres plages que downto 0 est si rare, que passer plus de temps sur le sujet ne servirait qu'à nous embrouiller. La valeur initiale est facultative, par défaut c'est 'U' pour tous les bits.

Nous utilisons déjà le integer type pour les opérations arithmétiques dans les didacticiels précédents. Alors pourquoi avons-nous besoin des types signés et non signés ? Pour la plupart, les concepteurs numériques aiment avoir plus de contrôle sur le nombre de bits qu'un signal utilise réellement.

En outre, les valeurs signées et non signées s'enroulent, tandis que le simulateur génère une erreur d'exécution si un integer est incrémenté au-delà des limites. Enfin, signé et non signé peuvent avoir d'autres valeurs comme 'U' et 'X' , tandis que les entiers ne peuvent avoir que des valeurs numériques. Ces méta-valeurs peuvent nous aider à découvrir des erreurs dans notre conception.

Exercice

Dans cette vidéo, nous apprenons comment les signaux signés et non signés se comportent de la même manière, et comment ils se comportent différemment :

Le code final que nous avons créé dans ce tutoriel :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T12_SignedUnsignedTb is

end entity;

architecture sim of T12_SignedUnsignedTb is

signal UnsCnt : unsigned(7 downto 0) := (others => '0');

signal SigCnt : signed(7 downto 0) := (others => '0');

signal Uns4 : unsigned(3 downto 0) := "1000";

signal Sig4 : signed(3 downto 0) := "1000";

signal Uns8 : unsigned(7 downto 0) := (others => '0');

signal Sig8 : signed(7 downto 0) := (others => '0');

begin

process is

begin

wait for 10 ns;

-- Wrapping counter

UnsCnt <= UnsCnt + 1;

SigCnt <= SigCnt + 1;

-- Adding signals

Uns8 <= Uns8 + Uns4;

Sig8 <= Sig8 + Sig4;

end process;

end architecture;

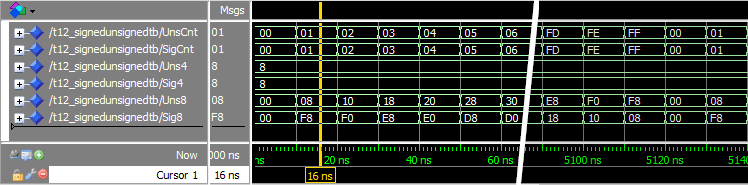

La fenêtre de forme d'onde dans ModelSim, agrandie sur les parties intéressantes :

Analyse

La base de tous les signaux de la forme d'onde est définie sur hexadécimal afin que nous puissions les comparer de manière égale.

Dans l'exemple du compteur d'enveloppement, nous voyons que les signaux signés et non signés se comportent exactement de la même manière. Les deux UnsCnt et SigCnt commencent à 0, et sont incrémentés un par un jusqu'à FF. Hex FF (décimal 255) est la plus grande valeur que nos signaux 8 bits peuvent contenir. Par conséquent, l'incrément suivant les ramène tous les deux à 0.

Nous avons créé les deux signaux 4 bits Uns4 et Sig4 , et leur a donné à tous les deux une valeur initiale de "1000". Nous pouvons voir sur la forme d'onde qu'ils sont tous les deux juste hexadécimaux 8 (binaire 1000).

Les deux derniers signaux 8 bits que nous avons créés étaient Uns8 et Sig8 . Nous pouvons voir sur la forme d'onde que leurs valeurs initiales sont 0, comme on pouvait s'y attendre. Mais à partir de là, ils se comportent différemment ! Apparemment, les types signés et non signés faisaient une différence lors de l'ajout de deux signaux de longueurs différentes.

C'est à cause de quelque chose connu sous le nom d'extension de signe . Ajouter des nombres positifs ou négatifs stockés dans des vecteurs de longueur égale, est la même opération en logique numérique. C'est à cause du fonctionnement du complément à deux. Si les vecteurs sont de longueurs différentes, le vecteur le plus court devra être prolongé.

Le nombre binaire 4 bits non signé "1000" est décimal 8, tandis que le nombre 4 bits signé "1000" est décimal -8. Le "1" à l'endroit le plus à gauche du nombre signé indique qu'il s'agit d'un nombre négatif. Par conséquent, les deux signaux 4 bits sont étendus différemment par le compilateur.

Il s'agit d'une visualisation de la façon dont l'extension de signe crée les différentes valeurs pour le Uns8 et Sig8 signaux :

À emporter

- Les signaux de type signé et non signé sont des vecteurs qui peuvent être utilisés dans les opérations arithmétiques

- Les signaux de type signé et non signé déborderont silencieusement

- L'extension de signe peut créer des résultats différents pour les types signés et non signés

Aller au tutoriel suivant »

VHDL

- Signé ou non signé en VHDL

- Comment utiliser une procédure dans un processus en VHDL

- Comment utiliser une fonction impure en VHDL

- Comment utiliser une fonction en VHDL

- Comment utiliser une procédure en VHDL

- Comment utiliser l'instanciation de Port Map dans VHDL

- Comment installer un simulateur et un éditeur VHDL gratuitement

- Microcontrôleur PIC18 :qu'est-ce que c'est et comment l'utiliser

- Qu'est-ce qu'un désignateur de référence et comment l'utiliser dans l'assemblage ?