Jétais un peu agacé par les particularités de linterface AXI la première fois que jai dû créer une logique pour interfacer un module AXI. Au lieu des signaux de contrôle habituels occupé/valide, plein/valide ou vide/valide, linterface AXI utilise deux signaux de contrôle nommés « prêt » et « valide

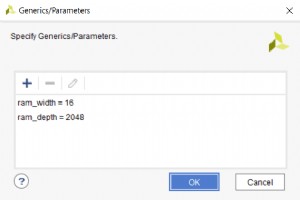

Un moyen pratique de remplir la RAM de bloc avec des valeurs initiales consiste à lire des littéraux binaires ou hexadécimaux à partir dun fichier ASCII. Cest aussi un bon moyen de créer une ROM (mémoire en lecture seule) en VHDL. Après tout, la RAM et la ROM sont la même chose dans les FPGA, la ROM

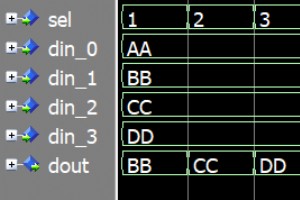

La lecture des valeurs de signal à partir du fichier est un autre moyen de générer des stimuli pour lappareil testé (DUT). La séquence et la synchronisation du testbench sont codées en dur dans un fichier de stimulus qui est lu par le testbench VHDL, ligne par ligne. Cela vous permet de modifier fac

La conversion du fichier image au format bitmap constitue le moyen le plus simple de lire une image à laide de VHDL. La prise en charge du format de fichier dimage graphique raster BMP est intégrée au système dexploitation Microsoft Windows. Cela fait de BMP un format dimage approprié pour stocker d

Cette vidéo est une présentation dintroduction sur les FPGA et la technologie logique programmable. Jai prononcé cette conférence de 45 minutes lors dun événement organisé par 7 Peaks Software à Bangkok, en Thaïlande, le 19 novembre 2019. Les faits saillants de la présentation incluent : 05:07 Qu

VHDL a un générateur pseudo-aléatoire intégré, mais il ne peut générer que des nombres à virgule flottante entre 0 et 1. Heureusement, vous pouvez en dériver tout autre type de format de données aléatoire dont vous auriez besoin. Continuez à lire cet article pour savoir comment produire real ou inte

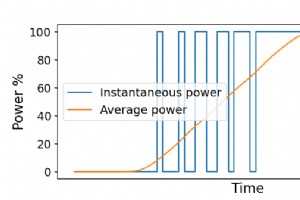

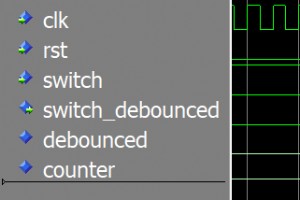

La modulation de largeur dimpulsion (PWM) est un moyen efficace de contrôler lélectronique analogique à partir de broches FPGA purement numériques. Au lieu dessayer de réguler la tension analogique, PWM active et désactive rapidement le courant dalimentation à pleine puissance de lappareil analogiqu

Jai remarqué que bon nombre des gadgets que jai achetés au cours des deux dernières années sont passés du clignotement des LED à la respiration des LED. La plupart des gadgets électroniques contiennent une LED détat dont le comportement donne des indications sur ce qui se passe à lintérieur de lappa

Comment arrêter le simulateur VHDL lorsque la simulation est terminée ? Il existe plusieurs façons de le faire. Dans cet article, nous examinerons les moyens les plus courants de mettre fin à une exécution réussie du testbench. Le code VHDL présenté ici est universel et devrait fonctionner dans nim

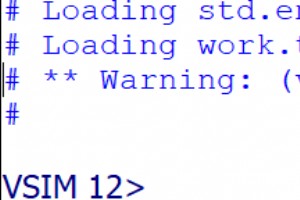

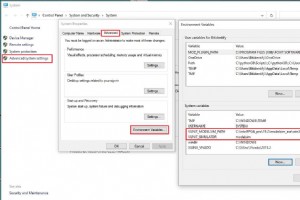

La plupart des simulateurs VHDL utilisent le langage de commande doutil (Tcl) comme langage de script. Lorsque vous tapez une commande dans la console du simulateur, vous utilisez Tcl. De plus, vous pouvez créer des scripts avec Tcl qui sexécutent dans le simulateur et interagissent avec votre code

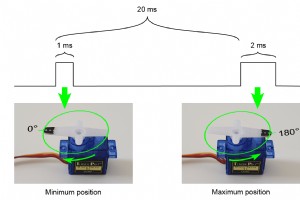

Les servomoteurs radiocommandés (RC) sont de minuscules actionneurs généralement utilisés dans les modèles réduits davions, de voitures et de bateaux. Ils permettent à lopérateur de contrôler le véhicule via une liaison radio à distance. Étant donné que les modèles RC existent depuis longtemps, lint

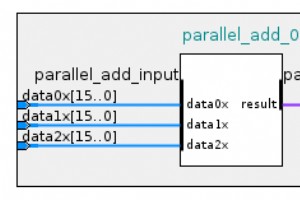

Linstruction generate en VHDL peut automatiquement dupliquer un bloc de code vers des fermetures avec des signaux, des processus et des instances identiques. Il sagit dune boucle for pour la région darchitecture qui peut créer des processus chaînés ou des instances de module. Contrairement à une

Les chaînes de texte en VHDL sont généralement limitées à des tableaux de caractères de longueur fixe. Cela a du sens car VHDL décrit le matériel et les chaînes de longueur générique nécessitent une mémoire dynamique. Pour définir un tableau de chaînes, vous devez allouer de lespace au moment de la

Ce didacticiel couvre lutilisation de lanalyseur logique intégré (ILA) et Entrée/Sortie virtuelle (VIO) cœurs pour déboguer et surveiller votre conception VHDL dans lIDE Xilinx Vivado. Dans de nombreux cas, les concepteurs doivent effectuer une vérification sur puce. Autrement dit, accéder au compo

Lors de la conception de VHDL pour des applications FPGA critiques pour la sécurité, il ne suffit pas décrire des bancs de test au mieux. Vous devez présenter la preuve que le module fonctionne comme prévu et sans effets secondaires indésirables. Les techniques de vérification formelle peuvent vous

VUnit est lun des frameworks de vérification VHDL open source les plus populaires disponibles aujourdhui. Il combine un exécuteur de suite de tests Python avec une bibliothèque VHDL dédiée pour automatiser vos bancs de test. Pour vous donner ce tutoriel VUnit gratuit, VHDLwhiz fait appel à Ahmadm

Avez-vous déjà souhaité exécuter une simulation VHDL incluant un cœur IP Quartus via le cadre de vérification VUnit ? Cest ce que lingénieur FPGA Konstantinos Paraskevopoulos avait en tête, mais il na pas trouvé de tutoriel adapté. Heureusement, il a utilisé son talent pour comprendre comment et a

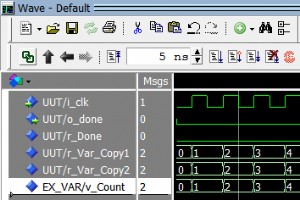

Les variables en VHDL agissent de la même manière que les variables en C. Leur valeur est valide à lemplacement exact dans le code où la variable est modifiée. Ainsi, si un signal utilise la valeur de la variable avant laffectation, elle aura lancienne valeur de variable. Si un signal utilise la val

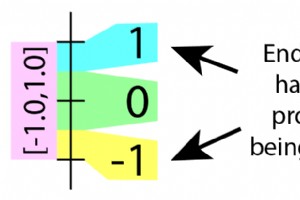

Tous les concepteurs numériques doivent comprendre comment les mathématiques fonctionnent à lintérieur dun FPGA ou dun ASIC. La première étape consiste à comprendre comment fonctionnent les types de signaux signés et non signés. Les types signés et non signés existent dans numeric_std package, qui f

La construction Record en VHDL peut être utilisée pour simplifier votre code. Les enregistrements sont similaires aux structures en C . Les enregistrements sont le plus souvent utilisés pour définir un nouveau type VHDL. Ce nouveau type contient tout groupe de signaux souhaité par lutilisateur. Le p

VHDL