PMOSFET Ge à haute mobilité avec passivation Si amorphe :impact de l'orientation de la surface

Résumé

Nous rapportons la passivation Si amorphe des pMOSFET Ge fabriqués sur des surfaces orientées (001), (011) et (111) pour des applications avancées de CMOS et de transistors à couches minces. La passivation au Si amorphe du Ge est réalisée par pulvérisation cathodique magnétron à température ambiante. Avec l'épaisseur fixe de Si t Si , Les pMOSFET Ge orientés (001) atteignent le courant à l'état passant le plus élevé I ON et mobilité efficace des trous μ eff par rapport aux appareils sur d'autres orientations. À une densité de charge d'inversion Q inv de 3,5 × 10 12 cm −2 , transistors Ge(001) avec 0.9 nm t Si démontrer un pic μ eff de 278 cm 2 /V × s, qui est 2,97 fois supérieure à la mobilité universelle Si. Avec la diminution de t Si , Je ON des transistors Ge augmente en raison de la réduction de l'épaisseur effective capacitive, mais les caractéristiques d'oscillation sous le seuil et de fond de fuite sont dégradées en raison de l'augmentation de l'écart médian D il .

Contexte

Le germanium (Ge) a suscité d'énormes intérêts de recherche pour les applications avancées de CMOS et de transistors à couche mince en raison de sa mobilité plus élevée des trous et de son traitement thermique inférieur par rapport au Si [1,2,3,4,5,6]. Pour atteindre la mobilité élevée des canaux, le processus de passivation de surface conduisant à une qualité d'interface élevée est nécessaire avant la formation de l'empilement de grilles. Plusieurs techniques de passivation de surface ont été développées pour offrir les avantages de la mobilité des porteurs dans les transistors à effet de champ Ge métal-oxyde-semiconducteur (MOSFET) [1, 2, 7,8,9,10]. Parmi ces techniques, une calotte en silicium (Si) passivée sur Ge a été le point chaud ces dernières années, en raison de ses avantages de suppression efficace des états d'interface et de bonne stabilité thermique et fiabilité [11]. La formation de calotte de passivation Si a été largement étudiée en utilisant le dépôt chimique en phase vapeur (CVD) avec des précurseurs de SiH4 [1], Si2 H6 [4], Si3 H8 [12], et l'évaporation par faisceau électronique [13]. Bien que la méthode CVD puisse fournir la couche de passivation la plus uniforme par rapport au dépôt physique en phase vapeur (PVD), son taux de passivation présente une forte corrélation entre l'orientation de la surface du canal et la température du processus. La technique PVD pourrait fournir un taux de passivation amélioré même à température ambiante, ce qui présente les avantages d'un faible budget thermique et d'un faible coût, ce qui la rend plus adaptée aux transistors à couche mince et aux applications d'intégration 3D en fin de ligne. Dans cette lettre, nous avons fabriqué des pMOSFET Ge à haute mobilité sur des surfaces orientées (001), (011) et (111) en utilisant une passivation Si amorphe par pulvérisation cathodique magnétron. Mobilité efficace des trous considérablement améliorée μ eff est réalisé dans les transistors Ge par rapport à la mobilité universelle Si. Impacts de l'orientation de la surface et de l'épaisseur du Si t amorphe Si sur l'effet boostant de la passivation Si amorphe sur μ eff sont étudiés.

Méthodes

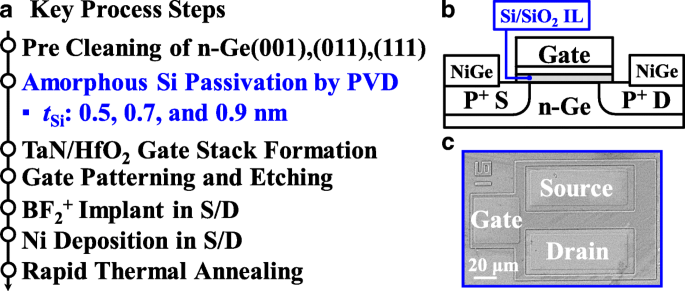

La figure 1a montre les étapes clés du processus de fabrication des pMOSFET Ge sur des surfaces orientées (001), (011) et (111). Après nettoyage de la pré-grille dans une solution HF diluée (1:50), une couche de passivation de Si amorphe ultrafine a été déposée sur des substrats n-Ge par pulvérisation magnétron à une puissance cible de 50 W. Trois durées de passivation de 60 s, 80 s et 100 s ont été utilisés correspondant au dépôt de 0,5, 0,7 et 0,9 nm t si , respectivement. Après cela, un HfO2 de 5 nm d'épaisseur le diélectrique de grille a été déposé à 250 °C par dépôt de couche atomique en utilisant TDMAHf et H2 O comme précurseurs de Hf et O, respectivement. Une électrode de grille en TaN de 50 nm a été déposée par pulvérisation cathodique réactive. Ensuite, l'électrode de grille a été modelée et gravée, qui a été suivie par BF2 + implantation dans les régions source/drain (S/D) à 30 KeV avec une dose de 1 × 10 15 cm − 2 . Des métaux S/D non auto-alignés de nickel 15 nm ont été formés par un processus de décollement. Enfin, un recuit thermique rapide à 400°C a été réalisé pour l'activation du dopant et la métallisation S/D. La figure 1b montre le schéma en coupe du Ge pMOSFET avec Si/SiO2 couche interfaciale (IL). La figure 1c montre une image au microscope vue de dessus d'un pMOSFET Ge fabriqué.

un Séquence de processus montrant les étapes clés utilisées pour fabriquer les pMOSFET Ge avec différents t Si . b Schéma en coupe d'un pMOSFET Ge avec SiO2 IL. c Image au microscope vue de dessus d'un pMOSFET Ge fabriqué

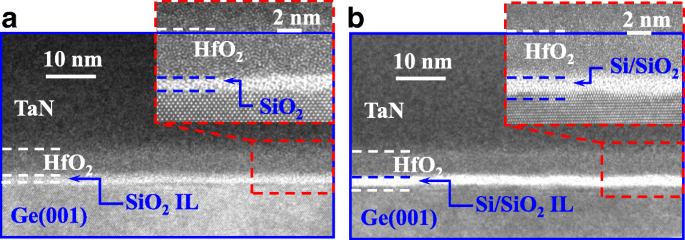

La figure 2a, b montre les images au microscope électronique à transmission (MET) de l'empilement de grilles à élevé/métal avec SiO2 /Si couche interfaciale (IL) sur le canal Ge(001) avec t Si de 0,5 et 0,9 nm, respectivement. Les encarts montrent les images TEM haute résolution (HRTEM) des échantillons. Pour l'appareil avec un t Si de 0,5 nm, la couche de Si amorphe était complètement oxydée, tandis que pour le dispositif avec 0,9 nm t Si , il restait environ deux monocouches de Si après les étapes de recuit suivantes.

Images MET en coupe d'empilements de portes Ge pMOSFET avec a 0.5 nm t Si et b 0.9 nm t Si . Les images HRTEM dans les médaillons montrent que Si/SiO2 IL est formé entre HfO2 et la chaîne Ge

Résultats et discussion

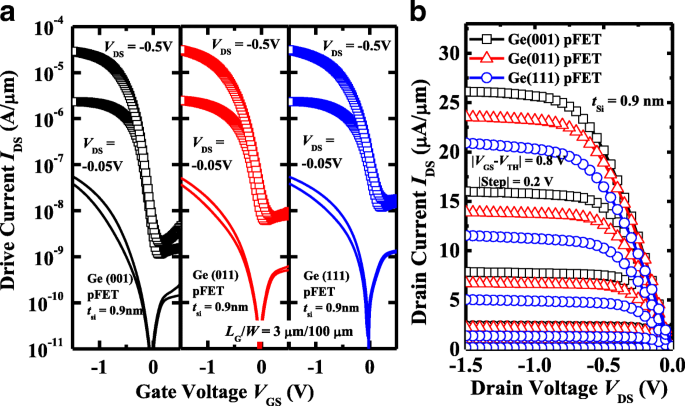

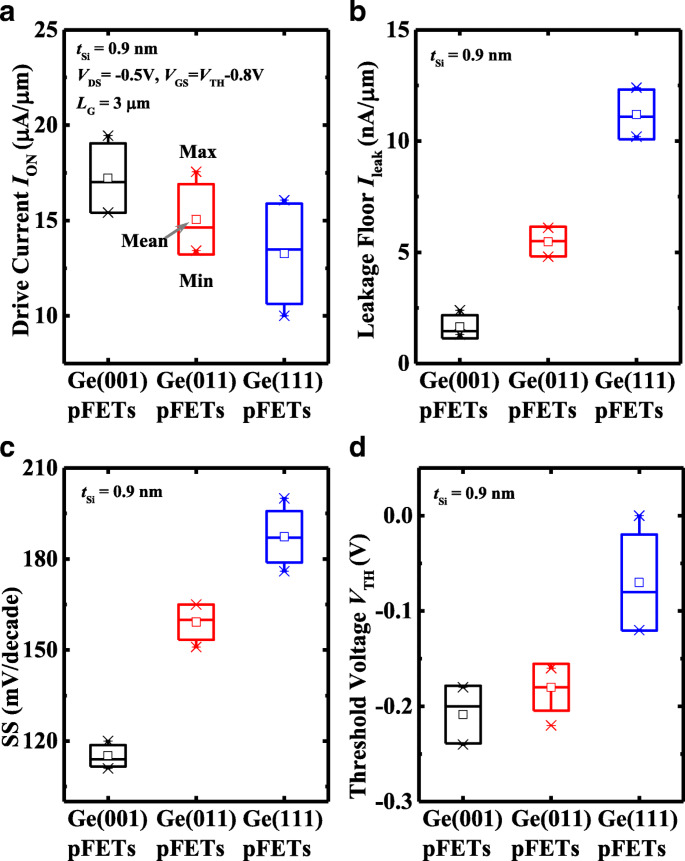

La figure 3a trace le I mesuré DS -V GS et Je G -V GS courbes des pMOSFET Ge typiques sur des surfaces orientées (001), (011) et (111) avec un t de 0,9 nm Si , qui montrent les excellentes caractéristiques de transfert. Tous les transistors ont une longueur de grille L G de 3 μm et une largeur de portail W de 100µm. La direction du canal est [110] pour toutes les orientations. Le Je DS -V DS courbes des dispositifs mesurées à différentes surcharges de grille V GS -V TH sont représentés sur la figure 3b. Ici, tension de seuil V TH est défini comme le V GS à Je DS de 10 -7 A/μm. Il est observé que Ge(001) pMOSFET atteint le courant d'entraînement plus élevé I ON par rapport aux transistors sur les surfaces (011) et (111) au V fixe GS -V TH . Plus tard, nous montrerons que cela est attribué au fait que les pMOSFET Ge(001) ont une mobilité effective des trous plus élevée μ eff en comparaison avec les dispositifs sur les deux autres orientations de surface. Nous effectuons une comparaison complète des performances électriques des appareils avec le t fixe Si de 0.9 nm, y compris I ON , fond de fuite I fuite , oscillation sous le seuil (SS) et V TH caractéristiques. Je fuite est défini comme le minimum I DS à V DS de − 0,05 V. La figure 4a présente le tracé statistique du I ON pour les pMOSFET Ge sur diverses orientations, et I ON a été défini comme I DS à un V DS de − 0,5 V et un V GS -V TH de − 0.8 V. Tous les transistors de ce tracé ont le L G de 3 μm et W de 100µm. Les dispositifs orientés (001) présentent le I moyen amélioré ON par rapport à ceux des orientations (011) et (111), ce qui est attribué à la plus haute μ eff . La figure 4b compare le I fuite pour les appareils, montrant que les transistors Ge(001) ont le I le plus bas fuite d'entre eux, et les pMOSFET Ge(011) ont le I inférieur fuite que les appareils orientés (111). Il convient de noter que le I fuite est déterminé par le courant inverse du p + /n jonction dans la région de drain, qui est affectée par la concentration de fond de dopage de type n dans le substrat Ge et l'activation du p + implanté dopants. Les concentrations de dopage de type n dans les plaquettes avec diverses orientations ne sont pas exactement les mêmes. L'orientation de la surface affecte le taux d'activation du dopant et la qualité de recristallisation des régions S/D. De plus, bien que le I G est inférieur à I DS avant la mise sous tension des transistors, cela influencerait le I fuite . De même, les pMOSFET Ge orientés (001) démontrent les caractéristiques SS améliorées par rapport aux deux autres orientations, ce qui est dû au fait que les transistors sur la surface (001) ont la densité de midgap inférieure de l'état d'interface D il par rapport aux autres appareils. La figure 4d montre que les appareils sur différentes orientations ont les différents V TH . Sur la base des résultats de la figure 4, il est conclu que, avec le t fixe Si de 0,9 nm, les pMOSFET Ge orientés (001) obtiennent les meilleures caractéristiques électriques.

un Mesuré I DS -V GS et Je G -V GS courbes de pMOSFET Ge orientés (001), (011) et (111) avec un t de 0,9 nm Si montrant les excellentes caractéristiques de transfert. b Je DS -V DS courbes mesurées à différents V GS -V TH pour les appareils

Comparaison de a Je ON , b Je fuite , c SS, et d V TH pour les pMOSFET Ge orientés (001), (011) et (111) avec un t Si de 0.9 nm

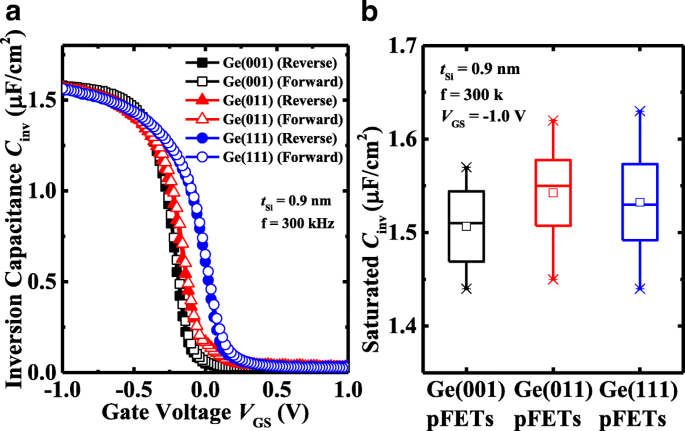

Les épaisseurs de Si/SiO2 IL dans les transistors avec 0.9 nm t Si sur différentes orientations de surface sont étudiées en utilisant la capacité d'inversion C inv contre V GS mesure, comme illustré à la Fig. 5. Les mesures de balayage avant et arrière présentent une hystérésis négligeable dans les appareils. Les transistors présentent la même amplitude de C inv , ~ 1,56 μF/cm 2 , correspondant à l'épaisseur effective capacitive (CET) de 2,2 nm. La figure 5b montre les résultats statistiques de C saturé inv pour les appareils, qui démontrent la très faible différence de C inv dans les transistors sur différentes orientations de surface. Ceci indique que le taux de passivation du Si amorphe par pulvérisation cathodique magnétron est indépendant de l'orientation de la surface. La règle des décalages gauche-droite du C inv -V GS courbes est bien cohérente avec celle de V TH pour les dispositifs de la figure 4d, ce qui pourrait être induit par la concentration de dopage légèrement différente dans des substrats d'orientation différents.

un Comparaison de l'inversion C inv -V GS courbes parmi les Ge pMOSFET avec 0.9 nm t Si sur des orientations différentes. Les balayages avant et arrière sont affichés. b Graphiques statistiques pour le C saturé inv des appareils montrant les différences négligeables de C inv en régime d'inversion

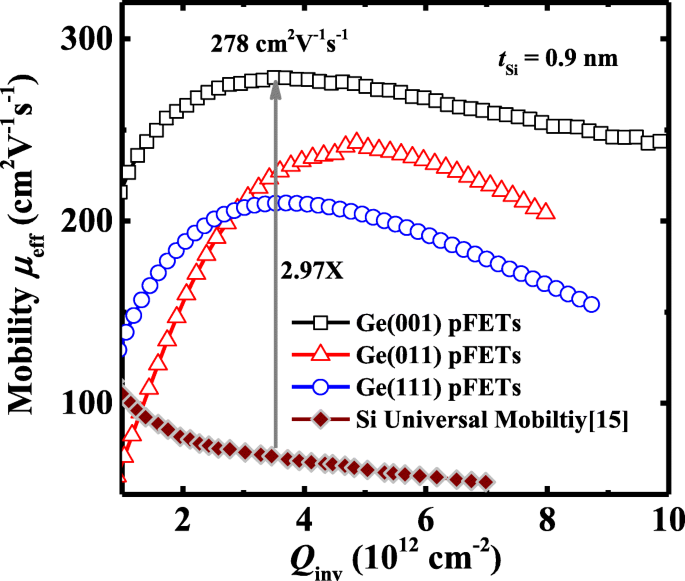

La figure 6 compare les caractéristiques de mobilité des transistors à 0,9 nm t Si sur différentes orientations de surface. Le μ eff a été extrait à l'aide d'une méthode basée sur la pente de résistance totale [14]. Les pMOSFET Ge(001) présentent une mobilité de canal beaucoup plus élevée par rapport aux dispositifs sur les orientations (011) et (111). Les transistors sur le substrat (001) atteignent un pic μ eff de 278 cm 2 /V·s à une densité de charge d'inversion Q inv de ~ 3,5 × 10 12 cm −2 , qui est 2,97 fois supérieure à la mobilité universelle Si. Rugosité de surface à l'interface Si/Ge et densité d'états d'interface (D il ) peut affecter μ eff des dispositifs à haute densité de porteurs d'inversion. Il est peu probable que les tranches de Ge achetées dans le commerce avec diverses orientations de surface présentent la différence évidente de rugosité de surface. Par conséquent, il est supposé que l'amélioration de la mobilité dans les dispositifs orientés (001) est principalement due à la diffusion réduite des porteurs contribuée par les états d'interface. Dans ce travail, nous évaluons le midgap D il des appareils, et avec le t fixe Si de 0,9 nm, les pMOSFET Ge orientés (001) ont en effet le midgap inférieur D il par rapport aux autres orientations.

Parcelle de μ eff contre Q inv pour Ge pMOSFETs avec 0,9 nm t Si sur des substrats orientés (001), (011) et (111). Les pMOSFET Ge(001) atteignent l'amélioration de 2,97 fois en μ eff à un Q inv de 3,5 × 10 12 cm −2 par rapport à la mobilité universelle Si. Le μ eff a été extrait à l'aide d'une méthode basée sur la pente de résistance totale [17]

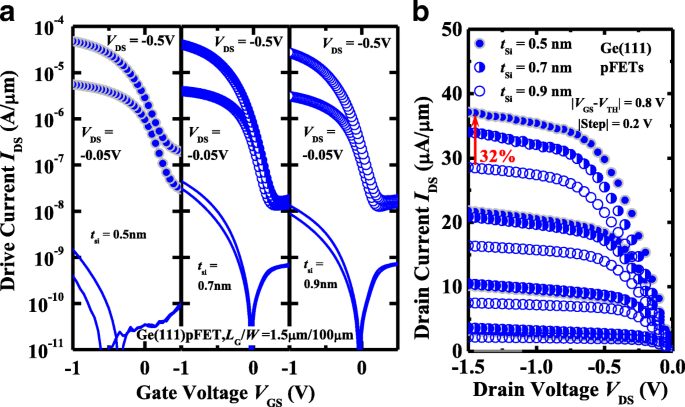

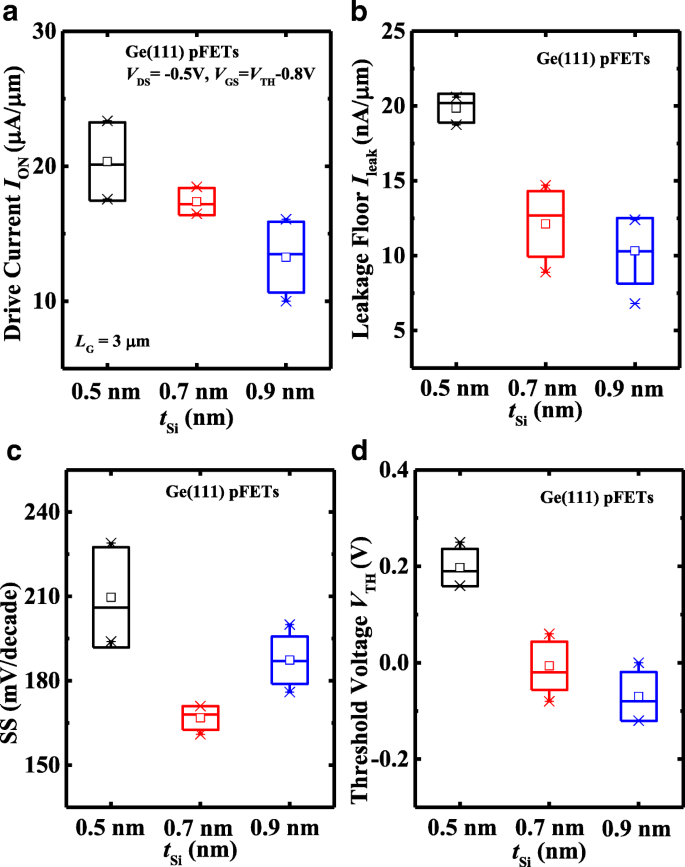

L'impact de t Si sur les performances électriques des pMOSFET Ge est également étudiée. Les figures 7a, b présentent le I mesuré DS -V GS et Je DS -V DS courbes, respectivement, des pMOSFET Ge orientés (111) avec t Si de 0,5, 0,7 et 0,9 nm à un V DS de − 0,05 et − 0,5 V. Les transistors ont un L G de 1,5 µm. Il est observé que les pMOSFET Ge avec 0.9 nm t Si présentent des caractéristiques de transfert améliorées par rapport aux appareils avec un t plus fin Si , mais Je ON de l'appareil diminue avec l'augmentation de t Si . Au V DS de − 1.5 V et V GS -V TH de − 0.8 V, Ge(111) pMOSFET avec 0.5 nm t Si démontre une amélioration de 32 % de I ON par rapport à l'appareil avec 0.9 nm t Si . La figure 8 présente les résultats statistiques de I ON , Je fuite , SS et V TH des Ge pMOSFET sur (111)-orientation avec différents t Si . De la Fig. 8a, nous voyons que les transistors avec 0,5 nm t Si atteindre le I amélioré ON en comparaison avec les appareils avec t plus épais Si , ce qui est dû au transistor avec 0.5 nm t Si qui a un CET plus petit, conduisant à un C plus élevé inv . On remarque que Je fuite diminue avec l'augmentation de t Si (Fig. 8b), et des transistors avec 0,5 nm t Si a des caractéristiques SS inférieures à celles des dispositifs avec couche de passivation Si amorphe de 0,7 et 0,9 nm (Fig. 8c). Cela peut être dû à ces transistors avec 0,5 nm t Si avoir un écart médian plus élevé D il . La relation entre SS et midgap D il de Ge pMOSFET peut être exprimé par SS = ln(10) ⋅ (kT /q) ⋅ [1 + (C il + C d )/C bœuf ], où C bœuf , C d , et C il sont respectivement la capacité de l'oxyde, la capacité de la couche d'appauvrissement et la capacité des pièges d'interface. C il peut être calculé par q × D il , étaient D il est la densité de piège d'interface. Bien que transistor avec 0.5 nm t Si a le plus grand C bœuf par rapport aux deux autres appareils, son espace intermédiaire D plus élevé il peut conduire au SS inférieur aux appareils avec le t plus épais Si . La passivation de surface affectera également le I fuite du drain à la source. Avec le balayage de V GS de la position au négatif, le canal passe du mode accumulation au mode inversion. Cependant, si le D il est élevé, certains points de la surface du canal sont bloqués par les pièges d'interface, et les chemins de fuite peuvent se former, augmentant I fuite du drain à la source. Comme le montre la figure 8d, les pMOSFET Ge(111) montrent le décalage de V TH à V négatif GS direction avec l'augmentation de t Si , ce qui est attribué à l'augmentation du TEC. De plus, la densité des pièges dans la moitié inférieure de la bande interdite semble augmenter pour le t plus mince. Si , ce qui pourrait conduire au décalage de V TH [2].

un Je DS -V GS et Je G -V GS et b Je DS -V DS courbes de Ge(111) pMOSFET avec divers t Si . Transistor avec 0,5 nm t Si présente une amélioration de 32 % de I ON par rapport à l'appareil avec 0.9 nm t Si à V DS de − 1.5 V et V GS -V TH de − 0.8 V

Comparaison de a Je ON , b Je fuite , c SS, et d V TH pour les pMOSFET Ge orientés (111) avec 0,5, 0,7 et 0,9 nm t Si montrant que les transistors avec 0,5 nm t Si avoir le meilleur Je ON , mais pire SS et I fuite caractéristiques par rapport aux appareils avec un t plus épais Si

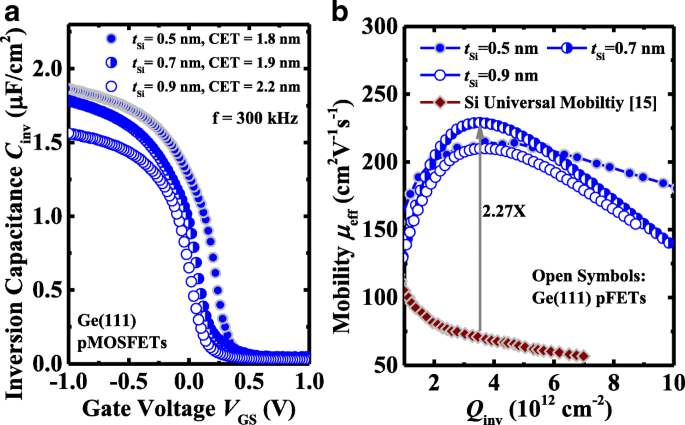

La figure 9a montre le C inv en fonction de V GS courbes pour les pMOSFET Ge sur une surface orientée (111) avec t Si de 0,5, 0,7 et 0,9 nm mesuré à une fréquence de 300 kHz. Les valeurs CET dans les régions d'inversion sont extraites à 1,8, 1,9 et 2,2 nm pour les appareils avec 0,5, 0,7 et 0,9 nm t si , respectivement. μ eff en fonction de Q inv les caractéristiques des appareils sont extraites et représentées sur la figure 9b. Le pMOSFET Ge orienté (111) avec un t de 0,7 nm si atteint la mobilité maximale la plus élevée de 229 cm 2 /V s, ce qui est 2,27 fois supérieur à la mobilité universelle Si. Il est à noter que les appareils avec 0,5 nm t Si présenter un μ considérablement amélioré eff sur les transistors avec un t plus épais Si à un Q élevé inv (par exemple, 10 13 cm −2 ). Cela conduit également à la plus haute I ON à un V élevé GS -V TH dans les appareils avec 0,5 nm t Si par rapport aux appareils avec 0,7 et 0,9 nm t Si . Le μ eff à un Q élevé inv diminue à mesure que t Si augmente de 0,5 nm à 0,7 ~ 0,9 nm, ce qui est attribué au fait que la plus grande rugosité de surface entraîne une diffusion plus forte de la rugosité de surface des porteurs. Lors de la passivation de la surface du Ge par pulvérisation cathodique magnétron à température ambiante, la diffusion des atomes de surface est fortement supprimée. Donc avec l'augmentation de t Si , la rugosité de surface est plus grande, ce qui peut être observé à partir des images HRTEM de la Fig. 2.

un C inv -V G caractéristiques mesurées à 300 kHz pour les appareils orientés (111) avec 0,5, 0,7 et 0,9 nm t Si . b μ eff en fonction de Q inv pour les pMOSFET Ge [17]

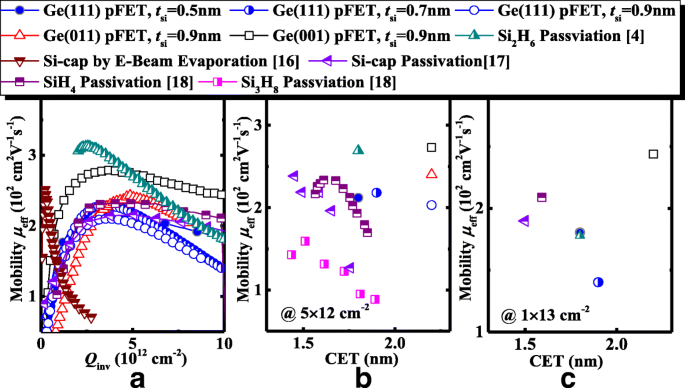

Dans la Fig. 10, nous comparons le μ eff des pMOSFET Ge dans ce travail avec ceux des transistors Ge relaxés rapportés avec Si par évaporation par faisceau E, SiH4 , Si2 H6, et Si3 H8 passivation. Comparé au Si amorphe par évaporation par faisceau E dans la réf. [15], les pMOSFET Ge dans ce travail présentent le μ considérablement amélioré eff . On voit que, au CET similaire, les pMOSFET Ge utilisant la passivation Si amorphe par pulvérisation cathodique magnétron ont le plus faible μ eff en comparaison avec les appareils avec Si2 H6 passivation. Le processus de passivation utilisant du Si amorphe doit être optimisé davantage pour améliorer la mobilité du porteur.

un μ eff pour les pMOSFET Ge dans ce travail par rapport aux résultats publiés pour les pMOSFET Ge relaxés. b , c Analyse comparative de μ eff extrait à Q inv = 5 × 10 12 et 1 × 10 13 cm −2 , respectivement, des Ge pMOSFET avec les différentes valeurs de CET [18, 19]

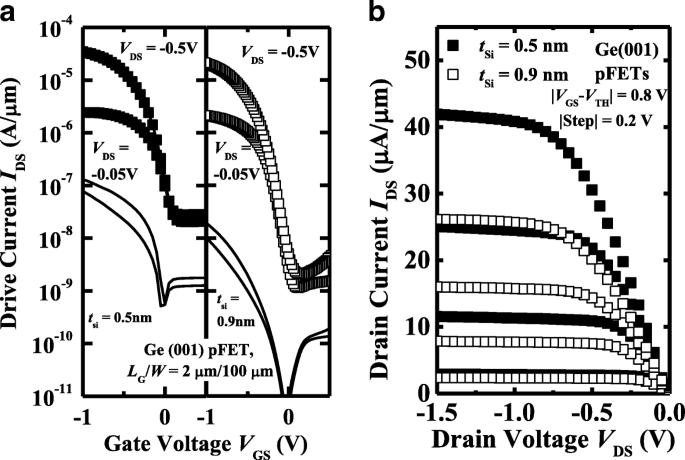

Ge pMOSFET avec les différents t Si sur une surface orientée (001) sont également caractérisés. Les figures 11a, b illustrent le I mesuré DS -V GS et Je DS -V DS courbes, respectivement, d'une paire de pMOSFET Ge(001) avec 0,5 et 0,9 nm t Si . Semblable aux dispositifs orientés (111), Ge(001) pMOSFET avec 0,5 nm t Si obtient l'amélioration de I ON mais la dégradation de I fuite par rapport au transistor avec 0.9 nm t Si .

un Mesuré I DS -V GS et Je G -V GS courbes de pMOSFET Ge orientés (001) avec 0,5 et 0,9 nm t Si . b Je DS -V GS courbes des appareils

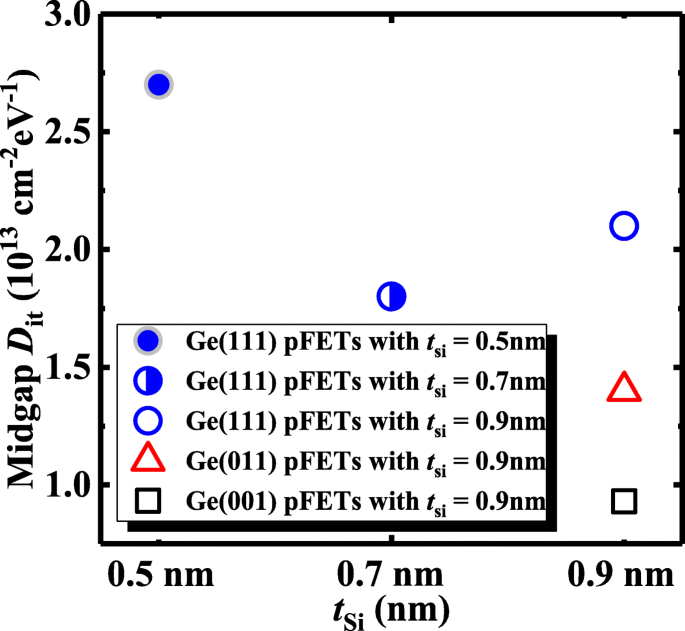

Le midgap D il les caractéristiques des pMOSFET Ge sont étudiées par la méthode de [16], et les valeurs de D il sont calculés par D il = [SSlog(e)/(kT /q ) − 1]C G /q , [16] où q est la charge électronique, k est la constante de Boltzmann, T est la température absolue, et C G est la capacité de grille mesurée par unité de surface. La figure 12 montre D il en fonction de l'épaisseur de Si amorphe avec différentes orientations de surface de Ge. Pour une surface orientée (111), un appareil avec un t de 0,7 nm si a le D le plus bas il valeur. Avec le t 0.9 nm Si , le périphérique orienté (001) a le D inférieur il par rapport aux transistors sur d'autres orientations.

D il par rapport à l'épaisseur de Si amorphe avec diverses orientations de surface Ge

Enfin, nous comparons les principales caractéristiques électriques des pMOSFET Ge sur les différentes orientations du tableau 1. Avec un t fixe Si , Ge(001) pMOSFET a les performances électriques améliorées par rapport aux deux autres orientations. Le courant d'entraînement peut être amélioré en réduisant le t Si de 0,9 nm à 0,5 nm, ce qui est dû au fait que le t plus fin Si fournit un CET considérablement réduit sans causer de dégradation dans μ eff .

Conclusions

Le Ge pMOSFET passivé par le Si amorphe est démontré sur des substrats orientés (001), (011) et (111). Avec un t Si de 0.9 nm, le I amélioré ON et les caractéristiques SS sont obtenues dans les pMOSFET Ge orientés (001) par rapport aux dispositifs sur les orientations (011) et (111), en raison de la plus grande μ eff et midgap inférieur D il . Ge(001) pMOSFET avec 0.9 nm t Si atteindre une mobilité maximale de 278 cm 2 /V s à un Q inv de 3,5 × 10 12 cm −2 , qui est 2,97 fois supérieure à la mobilité universelle Si. Il est démontré que Je ON des appareils s'améliore avec la diminution de t Si en raison de la réduction du TEC. Mais les pMOSFET Ge avec des t plus épais Si présenter l'oscillation inférieure au seuil supérieur et le plancher de fuite, en raison de cet écart médian D il peut être réduit en augmentant t Si .

Abréviations

- ALD :

-

Dépôt de couche atomique

- BF2 + :

-

Ion fluorure de bore

- HEC :

-

Epaisseur effective capacitive

- Voir :

-

Germanium

- GeOx :

-

Oxyde de Germanium

- HF :

-

Acide fluorhydrique

- HfO2 :

-

Dioxyde d'hafnium

- HRTEM :

-

Microscope électronique à transmission haute résolution

- IL :

-

Couche interfaciale

- MOSFET :

-

Transistors à effet de champ métal-oxyde-semiconducteur

- Non :

-

Nickel

- Si :

-

Silicium

- SS :

-

Balançoire sous le seuil

- TaN :

-

Nitrure de tantale

- TDMAHf :

-

Tetrakis (diméthylamido) hafnium

Nanomatériaux

- KUHMUTE repense la mobilité avec l'impression 3D SLS

- Impression 3D haute vitesse avec AFPM

- Impression 3D haute vitesse avec AION500MK3

- Haute performance des cellules solaires PEDOT:PSS/n-Si basées sur une surface texturée avec des électrodes AgNWs

- Convertisseur de polarisation avec biréfringence contrôlable basé sur une métasurface hybride entièrement diélectrique-graphène

- Cellule solaire hybride en silicium organique-nanostructuré à hautes performances avec structure de surface modifiée

- Une référence de tension sans résistance à faible puissance à l'échelle nanométrique avec un PSRR élevé

- Nanofeuillets poreux de ZnO avec modification partielle de la surface pour une meilleure séparation des charges et une activité photocatalytique élevée sous irradiation solaire

- Ge pMOSFET avec passivation GeOx formés par post-oxydation à l'ozone et au plasma