Comment le bruit au niveau du système dans les interfaces numériques peut entraîner des erreurs parasites dans la mémoire Flash série

Dans la poursuite incessante de performances supérieures au niveau du système, les fabricants de dispositifs intégrés (IDM) sont devenus très compétents dans le développement d'interfaces numériques capables de fonctionner à grande vitesse dans des environnements électriquement difficiles. Les interfaces standard, telles que SPI et I2C, offrent un moyen relativement simple d'interconnecter des appareils de différents fournisseurs de manière fiable et efficace. Il en est de même pour les autres types d'interfaces.

Le domaine numérique peut être considéré comme un havre de paix pour les développeurs qui cherchent à créer rapidement des systèmes complexes à l'aide de technologies « standards ». En effet, l'industrie de l'embarqué dépend largement d'interfaces basées sur des normes qui « fonctionnent », car elles fournissent le cadre de l'innovation. Lorsqu'ils ne « fonctionnent pas simplement », cela peut prêter à confusion, en particulier si la cause d'un défaut est mal interprétée. Toute confusion serait compréhensible, étant donné que les interfaces sont développées pour être robustes et fiables lorsqu'elles sont appliquées conformément à la spécification. Le fait que l'interface physique sous-jacente soit fixée dans du silicium rassurerait également.

Le bruit du système, sous toutes ses formes

Toute distorsion d'un signal peut être interprétée comme du bruit et il est probablement raisonnable de supposer que le bruit est le plus souvent apparent dans un environnement de communication; le signal reçu n'est pas le signal envoyé. Cette corrélation directe est relativement simple à trouver, mais dans certains cas, la cause et l'effet ne sont pas aussi faciles à identifier. Le défi est aggravé lorsque la panne devient intermittente.

Les microcontrôleurs d'aujourd'hui sont conçus pour offrir un fonctionnement fiable avec une configuration minimale. Dans le cas d'une interface série, cela peut inclure l'utilisation par défaut de courants d'entraînement élevés sur les broches d'E/S afin de lutter contre l'influence de longues pistes de circuits imprimés ou de charges capacitives élevées. Dans certains cas, cela peut entraîner une surcharge d'une interface qui, à son tour, peut entraîner des effets dérivés qui sont interprétés comme des erreurs ou des défauts.

Par exemple, les dispositifs de mémoire Flash série offrent un certain nombre de fonctionnalités avancées qui garantissent un fonctionnement fiable et permettent d'interroger le dispositif. Cela peut inclure des filtres de bruit, une programmation adaptative avancée et des algorithmes d'effacement qui gèrent les marges des cellules. Certains fabricants incluent également ECC dans les éléments de stockage en sauvegardant des métadonnées supplémentaires à chaque opération d'écriture pour permettre la détection et la correction d'erreurs à un ou plusieurs bits, mais ce correctif ECC n'aidera pas lorsque le bruit corrompt la transaction de message de base sur le bus d'interface de communication.

Le bruit sur l'interface SPI peut être mal interprété comme des impulsions d'horloge supplémentaires. Comme SPI est une interface pilotée par horloge, cela aurait des répercussions telles que des commandes ignorées, des données mal interprétées, de mauvaises commandes utilisées, etc. Cependant, le bruit transporte également de l'énergie et, dans certains cas, cette énergie peut elle-même introduire des erreurs dans le fonctionnement d'un appareil. .

Pompes de charge et dépassement

Dans la plupart des cas, des dépassements ou des dépassements dans un signal peuvent être tolérés par les interfaces numériques. Il ne faut cependant pas oublier que l'énergie sous la courbe est toujours présente et dans certains circuits cela peut être perturbateur.

Un exemple est le circuit de pompe de charge dans la mémoire Flash série. Si les signaux du bus SPI contiennent un bruit important, il est possible que l'énergie contenue dans ce signal se propage jusqu'à la pompe de charge et perturbe son fonctionnement.

La pompe de charge dans la mémoire Flash est une fonction critique, car elle fournit la puissance nécessaire pour modifier la polarisation d'une cellule de mémoire et, efficacement, stocker un 1 ou un 0 logique. Le processus d'écriture/effacement est un moment crucial dans le fonctionnement de Flash. mémoire, toute interruption de la pompe de charge pendant ce temps peut provoquer des erreurs d'écriture ou d'effacement et, bien que ces erreurs puissent être détectées, il est possible qu'elles ne soient pas apparentes.

Une erreur de ce type peut facilement être interprétée comme un défaut du périphérique de mémoire Flash. Le fait que la mémoire Flash a un nombre fini de cycles de lecture et d'écriture garantis par le fabricant est bien compris par les concepteurs embarqués, mais ce qui n'est peut-être pas si bien compris, c'est l'importance de fournir une interface propre sans trop de dépassement ou de sous-dépassement.

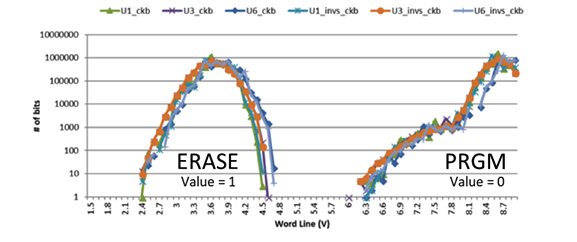

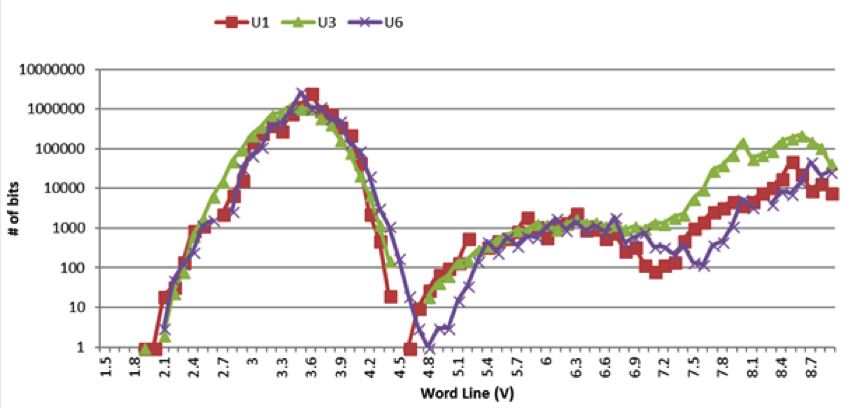

À titre d'exemple, considérons l'image de la figure 1. Elle montre les marges de cellules saines pour six périphériques Flash. Deux modèles distincts émergent entre les cellules programmées avec des données représentant 1 logique (2V à 5V) et 0 (>6v). Par comparaison, l'image de la figure 2 montre la marge des cellules de mémoire pour trois périphériques Flash qui ont subi une corruption de données causée par un dépassement et un sous-dépassement sur les lignes de contrôle.

Figure 1 :Cette image montre de bonnes données de séparation de marge de cellule pour la mémoire Flash qui a été programmée et effacée. (Source :Adesto)

Figure 2 :Cette image montre des données de séparation de marge de cellule médiocres pour la mémoire Flash où il y a eu un bruit important sur les lignes SPI. (Source :Adesto)

Plusieurs facteurs peuvent contribuer au niveau de bruit, tels que la fréquence de fonctionnement, l'amplitude du signal, les niveaux de commande du MCU et l'énergie contenue dans les pointes de bruit. La conception des circuits imprimés et la diaphonie entre les signaux peuvent également être des facteurs contributifs.

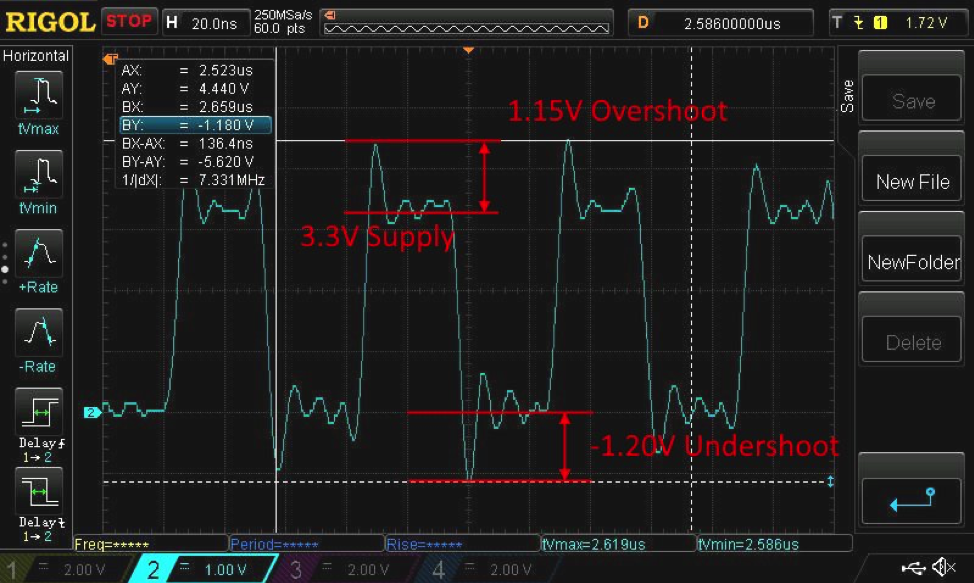

Les données de la figure 2 montrent les effets d'un dépassement et d'un sous-dépassement excessifs sur l'interface série. La figure 3 ci-dessous montre une représentation de ce à quoi ressemblerait ce dépassement dans une application réelle.

cliquez pour agrandir l'image

Figure 3 :Cette image de trace montre clairement que le dépassement et le sous-dépassement présents sur les lignes SPI ont entraîné une tension crête à crête de 5,65 V, ce qui dépasse la valeur maximale absolue documentée dans la spécification de la mémoire Flash . (Source :Adesto)

Le résultat de ce bruit était un fonctionnement erroné de l'appareil, qui se manifestait par des erreurs dans les valeurs stockées dans la mémoire flash série. Initialement, le véritable impact des erreurs n'a pas été détecté, car l'interrogation du registre STATUS sur une base moins fréquente a signalé moins d'erreurs, ce qui a conduit le concepteur à faire des hypothèses incorrectes sur la cause première de l'échec.

Identifier la véritable cause profonde

Bien que ce défaut soit apparu comme une panne de mémoire, la cause première n'était pas liée aux périphériques Flash. Cela a été découvert par les ingénieurs d'Adesto en sondant les signaux SPI et en identifiant le bruit du système présent. Bien que le bruit puisse être en partie attribué à une inadéquation d'impédance présente sur la piste PCB entre le MCU et la mémoire Flash, ce n'était pas toute l'histoire.

La source du bruit était en fait l'interface MCU, qui par défaut à un niveau de lecteur élevé à la mise sous tension. L'entraînement excessif était suffisant pour provoquer des dépassements et des dépassements sur les lignes SPI, qui dans certains cas peuvent être mal interprétés comme des transitions de signal, entraînant des erreurs de lecture ou d'écriture. Cependant, dans ce cas, il a été constaté que le dépassement contenait suffisamment d'énergie pour perturber la pompe de charge Flash, qui était à son tour à l'origine des erreurs.

Dans la conception du client, le microcontrôleur utilisé fournissait un courant d'entraînement configurable pour ses E/S, qui par défaut est ÉLEVÉ au démarrage. Le code application n'ayant pas modifié ce niveau lors de l'initialisation il est resté élevé en fonctionnement normal.

L'impact de ceci peut ne pas être apparent pour d'autres appareils sur le bus SPI, car les interfaces numériques sont généralement conçues pour être robustes. La nature sensible de la mémoire Flash, la nécessité de fonctionner à des fréquences beaucoup plus élevées, et en particulier, le fonctionnement de la pompe de charge, ont rendu la mémoire sensible aux dépassements/sous-dépassements. Cela a conduit à une opération erronée qui a été initialement interprétée à tort comme un défaut du périphérique de mémoire Flash.

Corriger l'erreur

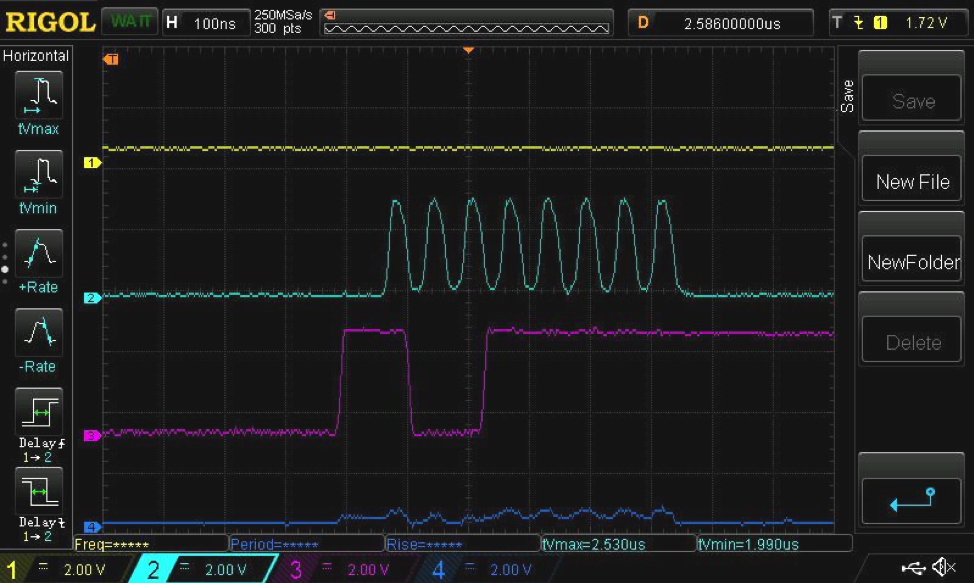

La réduction du courant d'entraînement via le micrologiciel a réduit le dépassement et le sous-dépassement à zéro (Figure 4), ce qui a entraîné un fonctionnement sans erreur de la mémoire Flash.

cliquez pour agrandir l'image

Figure 4 :sans dépassement apparent, la pompe de charge de la mémoire Flash série a pu fonctionner correctement et fournir une fonctionnalité fiable. (Source :Adesto)

La nature de la panne a montré que le périphérique Flash faisait tout son possible pour compenser l'effet de l'erreur, qui était le bruit excessif du système sur l'interface SPI.

Le point peut-être le plus important ici est que la cause était en fait une caractéristique de conception du MCU utilisé, qui était par défaut un mode de fonctionnement qui, dans la plupart des situations, serait tout à fait acceptable. La combinaison d'une sortie d'entraînement élevée et d'une inductance PCB imparfaite a créé une condition qui a entraîné une défaillance intermittente. La réduction de la sortie du lecteur sur le MCU, grâce à un simple changement de firmware, a résolu le problème.

Cela met en évidence la vraie leçon ici :ce qui peut apparaître comme une véritable défaillance d'un composant peut en fait être un oubli dans la conception. Le remplacement des dispositifs de mémoire aurait été une réponse naturelle à ce que l'on croyait initialement être la panne, mais grâce à une solide relation de travail entre le client et le fournisseur, ainsi qu'avec les équipes d'ingénierie matérielle et logicielle, la cause réelle a été trouvée et la bonne solution appliquée . Le résultat a été une conception nettement meilleure, des performances système plus élevées et une plus grande fiabilité.

Conclusion

Le bruit du système peut facilement être écarté lorsqu'il n'y a pas d'impact apparent. Les erreurs intermittentes sont particulièrement difficiles à localiser dans des conditions optimales, mais lorsque les erreurs sont mal interprétées, cela rend le défi encore plus difficile.

Le dépassement est probablement la forme la moins apparente de bruit du système, mais comme expliqué ici, son impact peut être important. La mémoire flash est une technologie fiable mais qui dépend d'une interface soigneusement conçue. Un bruit excessif sur l'interface série a le potentiel de se propager jusqu'aux circuits de pompe de charge, nuisant au fonctionnement des circuits de programmation et d'effacement. Il en résulte des caractéristiques imprévues qui peuvent facilement être interprétées comme un défaut sur l'appareil lui-même se présentant comme des défauts de cellule mémoire, ainsi que des opérations de programmation et d'effacement incohérentes ou peu fiables.

Dans ce cas, remplacer la mémoire Flash et supposer que le problème était résolu aurait pu entraîner la mise sur le marché de produits susceptibles de tomber en panne à un moment donné. Au lieu de cela, le concepteur a été en mesure d'améliorer la programmation et la cohérence d'effacement d'un facteur significatif, avec une endurance efficace passant d'environ 20 000 cycles inacceptables avant que les erreurs ne soient détectées à plus de 2,5 millions de cycles sans erreurs et sans exigence de routines supplémentaires de détection et de correction des erreurs.

Le niveau de configurabilité offert par les microcontrôleurs modernes peut être considéré à la fois comme une aide et un obstacle; le fait que le courant d'entraînement soit configurable était peut-être la cause du dépassement dans cet exemple. Cependant, être capable de réduire la force d'entraînement a également été efficace pour résoudre le problème.

Embarqué

- Keysight lance un nouveau système de test de bruit de phase

- Winbond :la puce mémoire à double matrice NOR+NAND prend désormais en charge NXP Layerscape LS1012A

- Acceed :PC véhicule avec CAN, GbE, PoE, 4G, 3G et WLAN

- Comment les jumeaux numériques peuvent aider à améliorer les performances logistiques

- Comment Cloud Analytics peut accélérer la transformation de la chaîne d'approvisionnement numérique

- Pourquoi les fournisseurs de matériaux devraient adopter le marketing numérique - et comment nous pouvons vous aider !

- Comment les équipementiers de dispositifs médicaux peuvent mettre en œuvre les modèles commerciaux de l'industrie 4.0

- Comment les contaminants dans l'air comprimé peuvent affecter les processus

- Comment réduire le nombre d'erreurs et améliorer le système qualité de production ?