Transistor semi-conducteur latéral à double diffusion à résistance active spécifique ultra-faible avec double grille améliorée et couche partiellement enterrée P

Résumé

Une résistance à l'enclenchement spécifique ultra-faible (R sur,sp ) Un transistor latéral à double diffusion métal-oxyde-semiconducteur (LDMOS) avec une double grille améliorée et une couche partiellement enterrée en P est proposé et étudié dans cet article. Le modèle analytique sur résistance pour le LDMOS proposé est conçu pour fournir un aperçu approfondi de la relation entre la résistance de la région de dérive et la résistance de la région du canal. Une couche enterrée N est introduite sous le puits P pour fournir un chemin de conduction à faible résistance et réduire considérablement la résistance de la région du canal. La structure améliorée à double grille est formée par une couche enterrée N tout en évitant la rupture de perforation verticale à l'état désactivé. Une couche partiellement enterrée en P avec une longueur optimisée est adoptée sous la région de dérive N pour étendre la région d'appauvrissement vertical et détendre le pic de champ électrique à l'état désactivé, ce qui améliore la tension de claquage (BV) avec une faible résistance de la région de dérive. Pour le LDMOS avec double grille améliorée et couche partiellement enterrée P, le résultat montre que R sur,sp est de 8,5 mΩ·mm 2 tandis que BV est 43 V.

Contexte

Avec l'augmentation de la demande pour une fonction logique plus complexe et plus rapide dans les circuits intégrés de puissance analogique, il est important d'améliorer les performances du transistor latéral à double diffusion métal-oxyde-semiconducteur (LDMOS), en minimisant spécialement la résistance à l'état passant ( R sur,sp ) et maximiser la tension de claquage (BV) à l'état bloqué [1,2,3,4,5,6,7,8,9]. Les technologies les plus développées se concentrent sur l'optimisation de la zone de dérive pour améliorer le compromis de R sur,sp vs BV pour les appareils LDMOS [10,11,12,13,14,15,16,17,18,19,20]. Dans nos travaux précédents, le LDMOS avec isolation en tranchée ultra-peu profonde (USTI) a été proposé [21]. La profondeur et l'angle d'angle de l'USTI ont été optimisés pour obtenir les meilleures performances de sa catégorie. Cependant, pour le LDMOS basse tension, la zone de dérive perd la domination en R sur,sp et la contribution de la région du canal ne peut être ignorée.

Méthode

Dans ce travail, un nouveau LDMOS à résistance active spécifique ultra-faible avec une double grille améliorée et une couche partiellement enterrée en P est étudié. Les modèles physiques IMPACT.I, BGN, CONMOB, FLDMOB, SRH et SRFMOB sont utilisés en simulation numérique. Un modèle analytique de résistance est proposé pour fournir un aperçu approfondi de la relation entre la résistance de la région de dérive et la résistance de la région du canal. Sur la base du modèle, la couche enterrée N et la couche partiellement enterrée P sont optimisées pour obtenir un faible R sur,sp et BV élevé.

Résultats et discussion

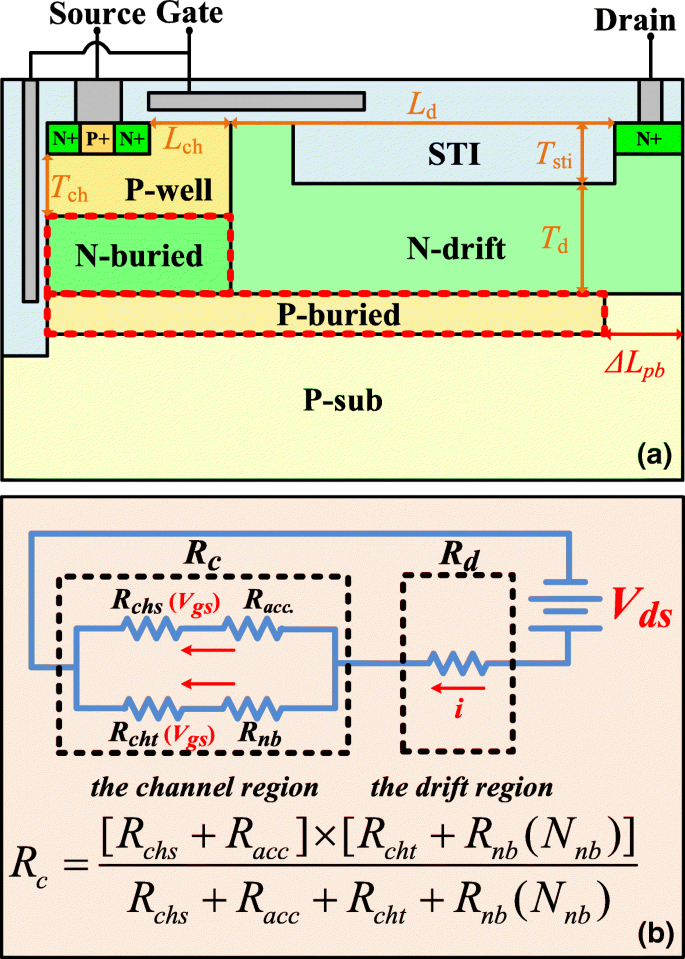

La figure 1a montre la coupe transversale schématique d'un LDMOS à résistance active spécifique ultra-faible avec une double grille améliorée et une couche partiellement enterrée en P. Le LDMOS comprend la double grille avec couche N-enterrée et la couche partielle P-enterrée qui contribue à réduire le R sur,sp et améliorer BV, respectivement. Dans la région du canal, la double grille améliorée est formée d'une grille en tranchée et d'une couche enterrée N hautement dopée. Comparée à la structure conventionnelle à double grille, la couche enterrée N réduit considérablement la résistance de la région du canal en fournissant un chemin de conduction à faible résistance passante sous le puits P à l'état passant. Dans la région de dérive, la couche partiellement enterrée de P avec une concentration de dopage élevée est introduite sous la région de dérive N pour améliorer la BV tout en maintenant un faible R sur,sp . La couche partiellement enterrée au P aide à réduire le champ électrique vertical à l'état bloqué sans rompre l'équilibre des charges dans la région de dérive. La taille de la clé du nouvel appareil est répertoriée dans le tableau 1.

un Vue en coupe schématique d'un LDMOS à très faible résistance spécifique à l'état passant avec une double grille améliorée et une couche partiellement enterrée en P. b Sur-résistance équivalente schématique pour le LDMOS proposé

La figure 1b montre le modèle de résistance active équivalent schématique pour le LDMOS proposé. La résistance totale à l'état passant est considérée comme la résistance de la zone de dérive (R d ) et la résistance de la région du canal (R c ) en série. Dans la région du canal, le chemin de conduction du canal de surface est parallèle au chemin de conduction du canal en tranchée. Ainsi, R c est égal à (R chs + R ac )//(R cht + R nb ), où R chs , R ac , R cht , et R nb sont respectivement les résistances du canal de grille de surface, de la région d'accumulation, du canal de grille de tranchée et de la couche N-enterrée. Sur la base du modèle de résistance proposé, la réduction de R c obtiendrait en diminuant R nb sans affecter les autres performances, car les autres résistances sont principalement déterminées par la technologie du procédé, la tension de fonctionnement et la tension de seuil. Le R d a été réduite en introduisant une couche enterrée de P sous la région de dérive N pour améliorer l'effet de réduction du champ de surface (RESURF) dans nos travaux précédents. Dans ce travail, la couche P-enterrée partielle est adoptée pour améliorer le BV tout en maintenant le faible R d .

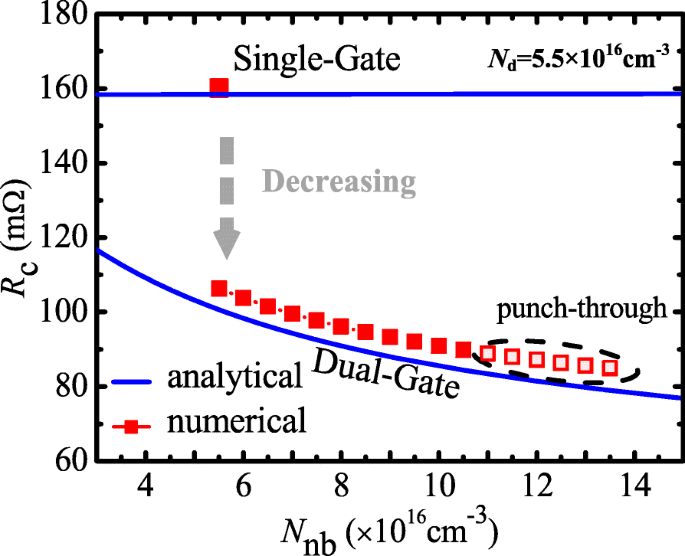

Viser la réduction de R c , la couche N-enterrée à forte concentration de dopage est introduite sous P-well. La figure 2 montre les R numériques et analytiques c en fonction de la concentration de dopage de la couche N-enterrée (N nb ) avec portail simple et double portail. Il est indiqué que la structure à double grille permet de réduire le R c par rapport à la porte simple. Lorsque N nb = N d = 5.5 × 10 16 cm −3 , R c est de 110 mΩ. Selon le modèle sur résistance, R nb est le principal contributeur de R c . Et puis, le R nb est souhaitée pour diminuer dans le but de plus petit R c . Comme le montre la figure 2a, R c est réduit avec N nb en augmentant. Lorsque N nb = 1,35 × 10 17 cm −3 , R c est réduit à 85 mΩ. Cependant, la figure 2 montre également que N nb serait limité par une panne de punch-through. En raison de l'ajout d'une porte de tranchée, R c est diminué d'abord de 34% avec N nb = N d = 5.5 × 10 16 cm −3 . Comme N nb augmente, R c diminue continuellement. Avec N optimisé nb = 1,05 × 10 17 cm −3 , R c est enfin diminué de 45%. Lorsque N nb> 1,05 × 10 17 cm −3 , une panne de punch-through se produira dans P-well. Le résultat analytique de R sur,sp montré dans la Fig. 2 indique que le modèle proposé fournit un bon ajustement avec les résultats de la simulation numérique. Par conséquent, le modèle est crédible pour guider la conception d'optimisation.

R numérique et analytique c en fonction de N nb avec portail simple et double (Z = 1 cm). N d est la concentration de dopage de la région de dérive N

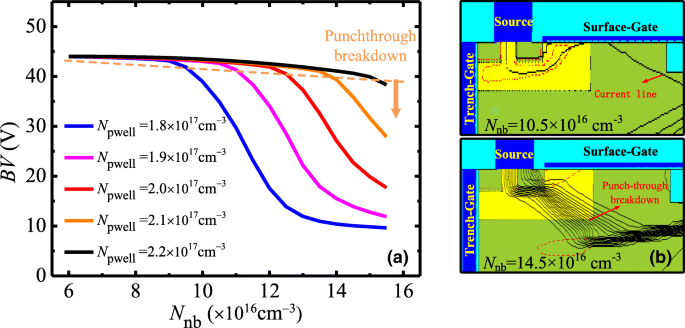

La figure 3a montre le BV numérique en fonction de N nb avec différentes concentrations de dopage du puits P (N pwell ). N nb a un effet non seulement sur le R c , mais aussi la BV. Pour un N donné pwell , BV reste inchangé à petit N nb , puis diminue avec N nb en augmentant. Lorsque N nb augmente à 1,2 × 10 17 cm −3 , BV commence à baisser avec N pwell = 2 × 10 17 cm −3 . La baisse de BV est attribuée à une panne de perforation dans la région du puits P, comme le montre la figure 3b. Lorsque la tension de drain augmente, la région d'épuisement dans le puits P s'étend jusqu'à la source. Lorsque la région d'épuisement attaque la jonction des puits N+/P, le claquage perforant se produit. Pour un grand N pwell , l'épuisement s'étend principalement à la zone de dérive, et le claquage perforant est évité sans dégrader le BV. Bien que le puits P avec une concentration de dopage élevée offre des avantages pour éviter le claquage, il améliorerait la tension de seuil. Ainsi, N pwell de 2 × 10 17 cm −3 est choisi en tenant compte de la tension de seuil et du compromis entre le BV et le R sur,sp .

un BV numérique en fonction de N nb avec différents N pwell . b Profil de densité actuel pour N nb = 10,5 × 10 16 cm −3 et 14,5 × 10 16 cm −3 tandis que N pwell = 2 × 10 17 cm −3 à la panne

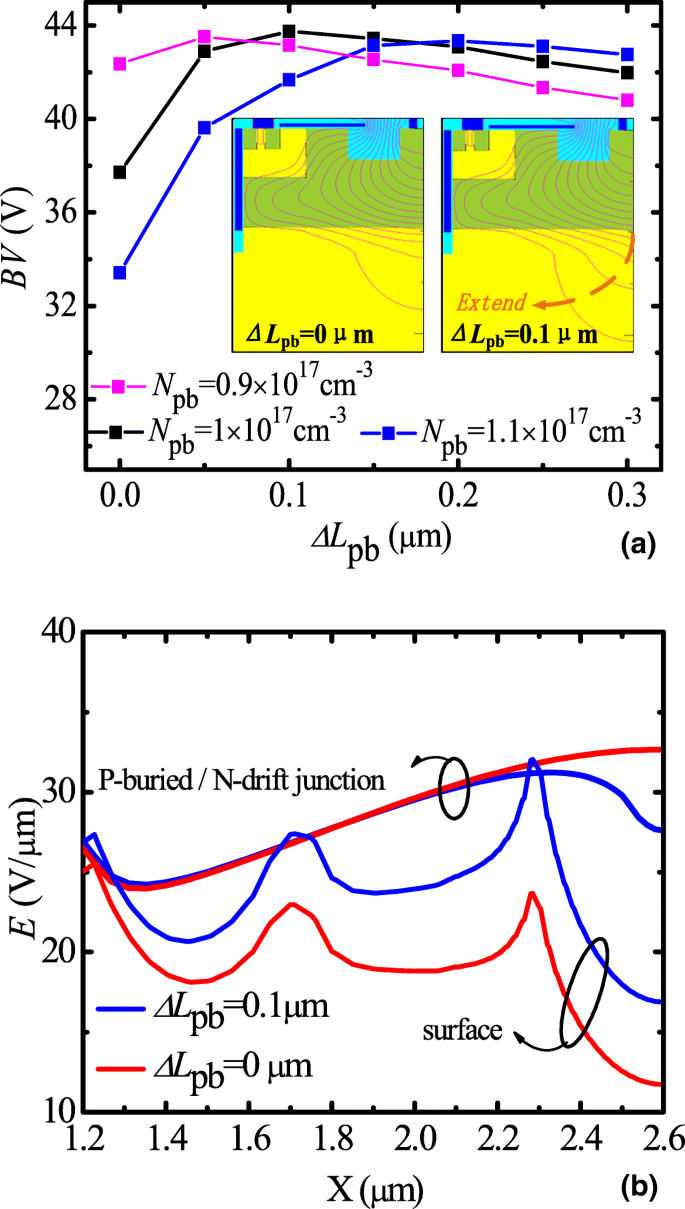

Afin d'obtenir un faible R d et une couche P-enterrée partielle à BV élevée est introduite sous la région de dérive N. La figure 4a montre BV en fonction de ΔL pb avec différents N pb . Pour un N donné pb , comme ΔL pb augmente, BV augmente puis diminue légèrement. Quand ΔL pb = 0.1 μm, N pb = 1 × 10 17 cm −3 , BV atteint la valeur maximale 43 V. L'insert montre le profil de contour équipotentiel avec N pb = 1 × 10 17 cm −3 . Il est indiqué que le contour équipotentiel dans la structure de couche partiellement enterrée de P s'étend davantage au substrat par rapport à la couche complète de P-enterré. La figure 4b montre la distribution du champ électrique à la surface et l'interface de jonction enterrée P/drift N. Pour les LDMOS conventionnels optimisés, le claquage se produit généralement à l'interface N-drift/P-enterré. Pour le LDMOS proposé, la jonction de N-drift/P-sub remplace la jonction de N-drift/P-enterré pour détendre le champ électrique vertical et étendre la région d'appauvrissement, ce qui se traduit par un BV plus élevé tout en maintenant un faible R d .

un BV en fonction de ΔL pb avec différents N pb . L'insert est le profil de contour équipotentiel avec N pb = 1 × 10 17 cm −3 . b Répartition du champ électrique en surface et interface de jonction P-enterré/N-dérive

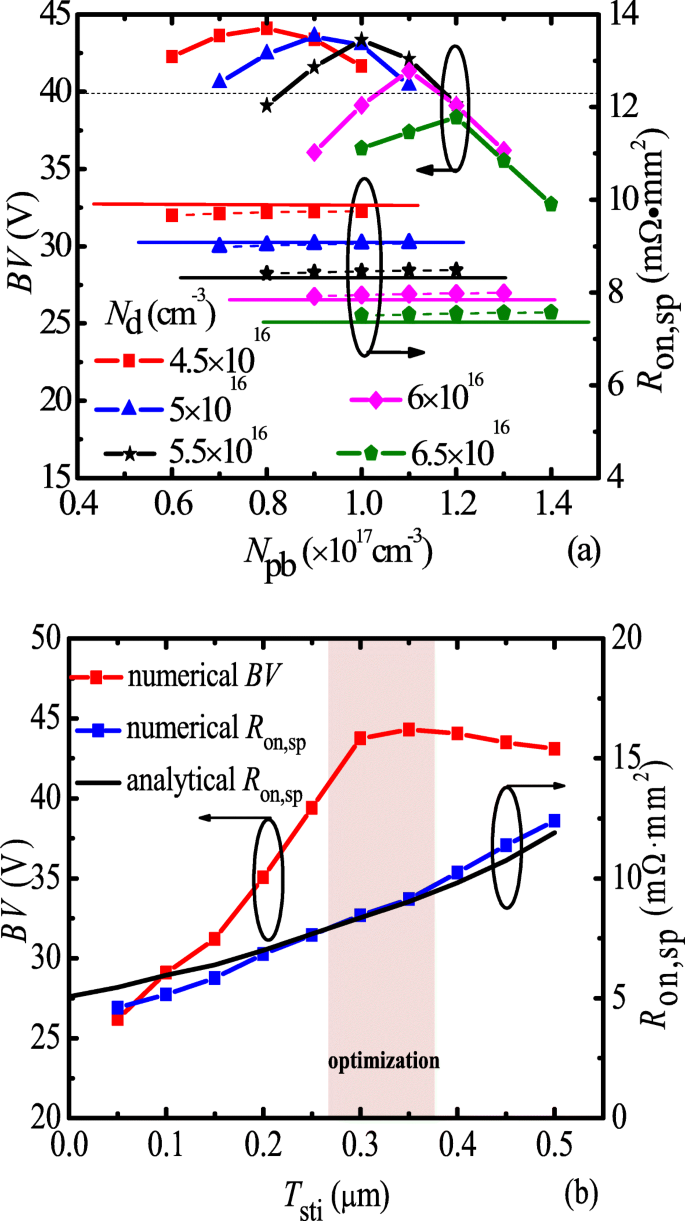

Un équilibre de charge entre la dérive de N et la couche partiellement enterrée de P est nécessaire pour obtenir un BV élevé. La figure 5a montre que BV et R numériques et analytiques sur,sp en fonction de la concentration de dopage du P-enterré (N pb ) pour différents N d . Pour un N donné d , BV a une valeur maximale avec des N variés pb , et le maximum de BV augmente avec la diminution de N d . Cependant, R sur,sp peut être augmenté comme le N d décroissant. En raison de BV requis supérieur à 40 V, le N d = 5.5 × 10 16 cm −3 et N pb = 1 × 10 17 cm −3 sont choisis. La figure 5b montre le BV et le R numériques et analytiques sur,sp en fonction de l'épaisseur de la couche STI (T sti ). T sti a un fort impact sur BV et R sur,sp , et il doit être conçu et optimisé avec soin ainsi que nos travaux antérieurs [21]. Pour T sti < 0.3 μm, le point de claquage sous le bord de la plaque de champ poly a un pic de champ électrique élevé. En tant que T sti augmente, le pic de champ électrique est détendu, puis BV augmente. Pour T sti = 0.3 μm, un BV de 43 V est obtenu. Pour T sti 0,3 μm, le pic de champ électrique sous le bord de la plaque de champ poly est assez faible, en conséquence, le point de claquage est transféré à la jonction P/N sous le côté drain. En tant que T sti augmente, la BV augmente puis sature.

un Numérique (ligne pointillée) et analytique (ligne continue) BV et R sur,sp en fonction de N pb pour différents N d . b Numérique (ligne pointillée) et analytique (ligne continue) BV et R sur,sp en fonction de T sti

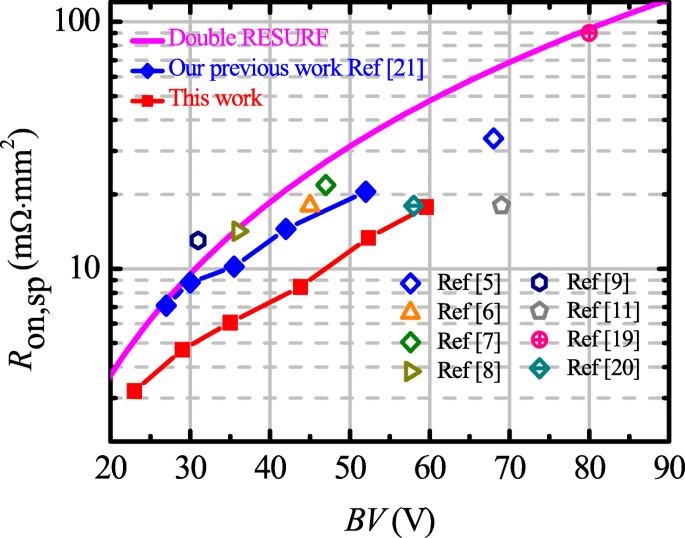

La figure 6 montre la référence des technologies bipolaires-CMOS-DMOS (BCD) existantes et le LDMOS proposé. Apparemment, la technologie de processus pour le LDMOS proposé est compatible avec notre technologie BCD développée qui a atteint les meilleures performances de LDMOS. Dans le processus de fabrication du LDMOS proposé, la couche enterrée N pourrait partager le même masque avec le puits P. Pour le LDMOS proposé, R sur,sp est de 8,5 mΩ·mm 2 tandis que BV = 43 V, qui est réduit d'environ 37% par rapport à nos travaux précédents.

Le benchmark des technologies BCD existantes et le LDMOS proposé

Conclusion

Un nouveau LDMOS à résistance spécifique ultra-faible avec double grille améliorée et couche partiellement enterrée au P est proposé et étudié par simulation numérique dans cet article. Une couche enterrée N avec une concentration de dopage élevée est utilisée pour obtenir une double porte améliorée avec une réduction de R c . Une couche partiellement enterrée de P est introduite sous la région de dérive N pour améliorer la BV avec le maintien de l'équilibre des charges. Le processus de fabrication du LDMOS dans ce travail est compatible avec la technologie BCD existante rapportée dans nos travaux précédents. Le résultat montre que le R sur,sp du LDMOS proposé est réduit de 37% à BV de 43 V par rapport aux travaux précédents. Avec la technologie de traitement des semi-conducteurs allant au niveau nanométrique, le R sur,sp peut réduire davantage avec la diminution de la longueur du canal.

Abréviations

- BCD :

-

Bipolaire-CMOS-DMOS

- BV :

-

Tension de claquage

- LDMOS :

-

Transistor latéral métal-oxyde-semi-conducteur à double diffusion

- RESURF :

-

Réduire le champ de surface

- R sur,sp :

-

Sur-résistance spécifique

- USTI :

-

Isolation de tranchée ultra-peu profonde

Nanomatériaux

- Nanofibres et filaments pour une administration améliorée des médicaments

- Caractéristiques d'alignement interfacial, électrique et de bande des piles HfO2/Ge avec une couche intermédiaire de SiO2 formée in situ par dépôt de couche atomique amélioré par plasma

- Un nouveau photocatalyseur à hétérojonction Bi4Ti3O12/Ag3PO4 avec des performances photocatalytiques améliorées

- Effet de la stabilité thermique améliorée de la couche de support en alumine sur la croissance de nanotubes de carbone à paroi unique alignés verticalement et leur application dans les membranes …

- Influence des nanoparticules d'Ag de différentes tailles et concentrations intégrées dans une couche compacte de TiO2 sur l'efficacité de conversion des cellules solaires à pérovskite

- Potentiel antiprolifératif et de déclenchement de l'apoptose des nanoparticules lipidiques ciblées à base de paclitaxel avec internalisation cellulaire améliorée par les récepteurs de la transf…

- Absorbeur omnidirectionnel par effet de plasmon du vide dans la région visible avec un champ électrique localisé considérablement amélioré

- Transistor à effet de champ SnSe2 avec rapport marche/arrêt élevé et photoconductivité à polarité commutable

- Nanomembranes TiO2 fabriquées par dépôt de couche atomique pour électrode de supercondensateur à capacité améliorée