Performances analogiques/RF du transistor à effet de champ à tunnel double source T-Shape Gate

Résumé

Dans cet article, un transistor à effet de champ tunnel à double source (TGTFET) à grille en forme de T à base de silicium est proposé et étudié par simulation TCAD. En tant qu'étude contrastive, la structure, les caractéristiques et les performances analogiques/RF de TGTFET, LTFET et UTFET sont discutées. Le chevauchement de grille introduit par la grille en forme de T peut améliorer l'efficacité de la jonction tunnel. Les régions à double source dans TGTFET peuvent augmenter le courant à l'état passant (I ON ) en offrant une zone de jonction de tunnel doublée. Afin d'améliorer encore les performances de l'appareil, la poche n+ est introduite dans TGTFET pour augmenter encore le taux de tunneling de bande à bande. Les résultats de la simulation révèlent que le I du TGTFET ON et rapport de commutation (I ON /Je OFF ) atteignent 81 μA/μm et 6,7 × 10 10 à 1 V de tension grille à source (V g ). L'oscillation moyenne sous le seuil du TGTFET (SSavg , de 0 à 0,5 V V g ) atteint 51,5 mV/déc, et l'oscillation sous-seuil minimale du TGTFET (SSmin , à 0,1 V V g ) atteint 24,4 mV/déc. De plus, il a été constaté que les TGTFET ont une forte robustesse sur l'effet d'abaissement de la barrière induite par le drain (DIBL). Les effets de la concentration de dopage, de la dimension géométrique et de la tension appliquée sur les performances de l'appareil sont étudiés afin de créer la directive de conception TGTFET. De plus, la transconductance (g m ), la conductance de sortie (g ds ), capacité grille-source (C gs ), capacité grille à drain (C gd ), fréquence de coupure (f T ), et le gain de bande passante (GBW) du TGTFET atteint 232 μS/μm, 214 μS/μm, 0,7 fF/μm, 3,7 fF/μm, 11,9 GHz et 2,3 GHz à 0,5 V de tension drain-source (V d ), respectivement. Bénéficiant de l'avantage structurel, TGTFET obtient de meilleures caractéristiques DC/AC par rapport à UTFET et LTFET. En conclusion, les bonnes performances considérables font du TGTFET un choix très attrayant pour la prochaine génération d'applications basse consommation et analogiques/RF.

Contexte

La réduction d'échelle des transistors à effet de champ métal-oxyde-semiconducteur (MOSFET) apporte une amélioration significative de la consommation d'énergie des circuits intégrés (CI), des caractéristiques de commutation, de la fonction du circuit et de la densité des circuits intégrés [1, 2]. Mais la contradiction inconciliable entre la mise à l'échelle de la tension d'alimentation et la réduction des courants de fuite à l'état bloqué (I OFF ) se traduira finalement par une consommation d'énergie élevée inacceptable [3]. Dans le même temps, la dégradation de la fiabilité causée par les effets de canal court (SCE) devient de plus en plus grave [4, 5]. Afin de résoudre ces problèmes, il est valable de réduire l'oscillation sous le seuil (SS) et la tension d'alimentation des dispositifs. Sur la base du mécanisme de tunneling bande à bande, les transistors à effet de champ tunnel (TFET) atteignent l'oscillation sous-seuil (SS) inférieure à 60 mV/dec et pourraient réduire efficacement la tension d'alimentation [6,7,8,9,10] . De plus, en raison de l'existence de la jonction tunnel près de la source, le TFET a généralement une petite capacité grille-source (C gs ) [1, 11] ce qui est bénéfique pour les performances de fréquence de l'appareil.

Des études récentes montrent que le TFET semble être un candidat prometteur pour les futures applications basse consommation [12,13,14,15,16] et les applications analogiques/RF [17,18,19]. Cependant, en raison de la petite zone de tunneling efficace, le courant de tunneling limité devient un inconvénient inhérent au TFET P-I-N conventionnel, ce qui conduit à un faible courant de fonctionnement à l'état passant (I ON ). Afin d'améliorer les performances du TFET, de nombreuses nouvelles structures ont été proposées ces dernières années [20,21,22,23,24,25]. Bénéficiant de la grille en retrait, le transistor à effet de champ tunnel en forme de L (LTFET) [23, 24] et le transistor à effet de champ tunnel en forme de U (UTFET) [25] ont été proposés pour obtenir un I ON avec une structure d'appareil compacte. Cependant, il y a encore beaucoup de place pour l'amélioration en LTFET et UTFET et doit consacrer plus d'efforts pour étudier les performances analogiques/RF de ces appareils.

Dans cet article, un transistor à effet de champ tunnel à double source (TGTFET) à grille en forme de T à double source est proposé et étudié par simulation TCAD. Le TGTFET conçu peut doubler la zone de jonction à effet tunnel par rapport aux LTFET et UTFET. Le chevauchement de porte introduit par la porte en forme de T conçue peut améliorer le taux de tunneling de bande à bande (taux BBT). Les résultats de la simulation montrent que le TGTFET proposé obtient un I plus élevé ON (8,1 × 10 − 5 A/μm à V d = 1 V) que le LTFET et l'UTFET dans la même condition. Les deux SSmin (à V g = 0,1 V) et le SSmoy (0~0,5 V V g ) du TGTFET sont inférieurs à 60 mV/déc (respectivement 24,4 mV/déc et 51,5 mV/déc). Le TGTFET obtient une meilleure caractéristique d'entrée/sortie (g m = 232 μS/μm, g ds = 214 μS/μm) que l'UTFET et le LTFET. De plus, les caractéristiques de capacité de TGTFET, UTFET et LTFET sont discutées en détail. Enfin, TGTFET gagne de meilleures performances analogiques/RF (f T = 11,9 GHz et GBW =2,3 GHz) par rapport à UTFET et LTFET. En conséquence, un TGTFET avec de bonnes performances peut être obtenu. Les structures de cet article sont les suivantes :la section « Méthodes » comprend la description de la structure et des paramètres de TGTFET, LTFET [23, 24] et UTFET [25 ] ainsi que les méthodes de simulation TCAD. La section « Résultats et discussion » comprend la description des résultats de la simulation. Dans cette section, le mécanisme, les caractéristiques et les performances analogiques/RF du TGTFET sont étudiés et comparés au LTFET et à l'UTFET. L'influence des paramètres de l'appareil sur le TGTFET est également analysée en détail. La section « Conclusions » donne une conclusion de cet article.

Méthodes

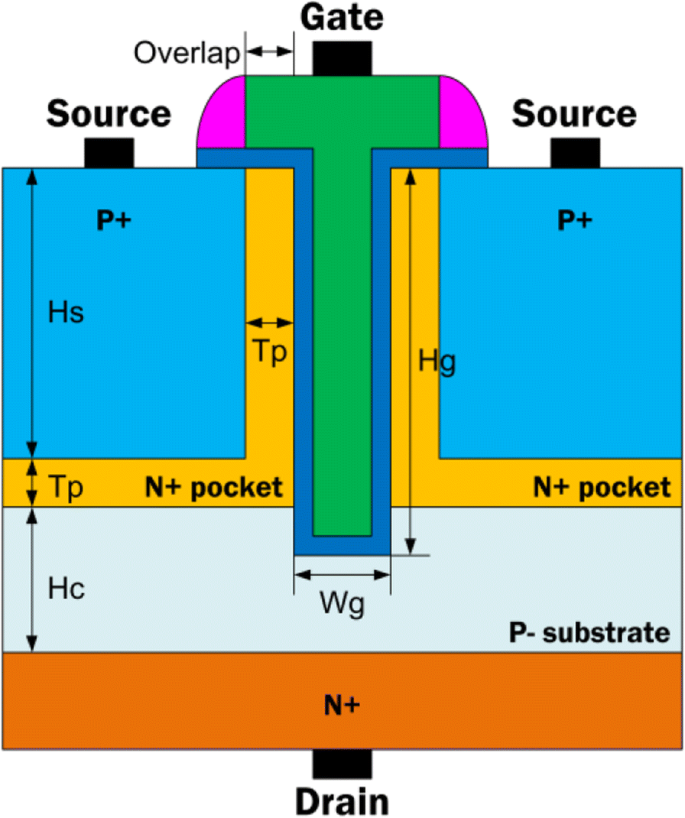

La structure du transistor à effet de champ tunnel à double source à grille en forme de T (TGTFET) est illustrée sur la figure 1. La forme de la grille est similaire à la lettre de l'alphabet « T » (région verte). Les régions à double source sont situées sur les deux côtés de la grille (régions en saphir). Deux poches n+ (régions jaunes) sont insérées pour augmenter le taux d'effet tunnel [20,21,22]. Le drain n+ est placé dans le fond du canal. Par conséquent, la porte en forme de T chevauche les poches n+ dans les directions verticale et latérale. De cette manière, le champ électrique au sommet de la jonction tunnel peut être augmenté. L'augmentation du champ électrique fait que la bande d'énergie se plie plus fortement. Enfin, le taux d'effet tunnel des électrons est amélioré en raison de l'amélioration du champ électrique d'angle [26].

Schéma du transistor à effet de champ tunnel à double source (TGTFET) à grille en forme de T proposé

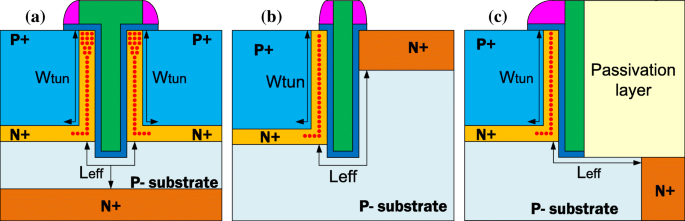

La figure 2 montre la structure de périphérique de LTFET [23, 24], UTFET [25] et TGTFET. Le chevauchement de portes peut aider à améliorer l'efficacité de tunnel du TGTFET. Les régions à double source dans TGTFET peuvent doubler la zone de jonction tunnel par rapport à LTFET et UTFET.

Comparaison de a le TGTFET proposé, b UTFET, et c LTFET

Les paramètres des TGTFET, UTFET et LTFET à base de silicium utilisés dans les simulations sont les suivants :Hs =30 nm (hauteur de la région source), Hg =40 nm (hauteur de la grille en retrait), Wg =6 nm (largeur de la région de grille), Hc =15 nm (hauteur de la région du canal), Tp =5 nm (épaisseur de la poche n+), ϕ = 4. 33 eV (fonction de travail de porte), Tox =2 nm (épaisseur du HfO2 diélectrique de grille), N S = 1 × 10 20 cm −3 (p+ concentration de dopage source), N D = 1 × 10 19 cm −3 (n+ concentration de dopage du drain), N sous = 1 × 10 17 cm −3 (p− concentration de dopage du substrat), et N P = 5 × 10 18 cm −3 (n+ concentration de dopage de poche). Le coefficient de largeur dans la simulation est par défaut de 1 μm.

Les simulations de TGTFET, UTFET et LTFET sont réalisées dans les outils Silvaco Atlas TCAD. Un modèle BTBT non local est introduit dans cette simulation pour prendre en compte la variation spatiale de la bande d'énergie, ce qui peut aider à faciliter la précision du processus de tunneling BTBT. Le modèle de mobilité Lombardi est considéré pour rendre la mobilité du canal plus précise (en considérant la diffusion de surface incluant le champ transverse et la concentration de dopage). Les statistiques de Fermi et le modèle de rétrécissement de la bande interdite sont pris en compte pour ajuster l'effet des régions fortement dopées. Le modèle de recombinaison Shockley-Read-Hall est également pris en compte dans cet article.

Résultats et discussion

Mécanisme de l'appareil et caractéristiques DC avec différents paramètres

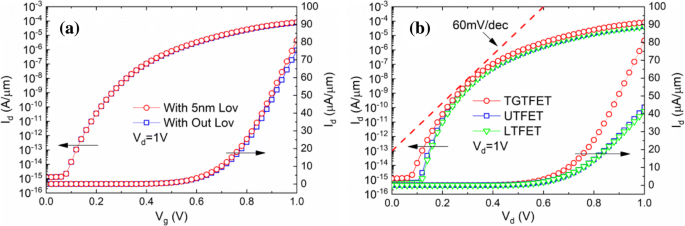

La figure 3a montre les caractéristiques de transfert du TGTFET avec et sans chevauchement de grille. Avec le chevauchement de porte supplémentaire, le I ON augmente de 7,5 × 10 −5 à 8.1 × 10 −5 A/μ m à V g = V d = 1 V. La figure 3b montre les courbes caractéristiques de transfert de TGTFET, UTFET et LTFET. Afin de rendre la comparaison plus précise, les modèles de simulation et les dimensions géométriques de ces trois dispositifs sont réglés pour être identiques. En conséquence, le TGTFET a environ deux fois plus de I ON par rapport à LTFET et UTFET, comme le montre la figure 3b. SSmin de TGTFET est de 24,4 mV/déc à V g = 0,1 V et SSmoy est de 51,5 mV/déc lorsque 0 V < V g < 0,5 V. Les rapports de commutation (I ON /Je OFF ) sont 6,7 × 10 10 à V g = V d = 1 V et 6,5 × 10 8 à V g = V d = 0,5 V.

a simulé caractéristiques de transfert du TGTFET avec/sans chevauchement de grille et b caractéristiques de transfert de TGTFET, UTFET et LTFET

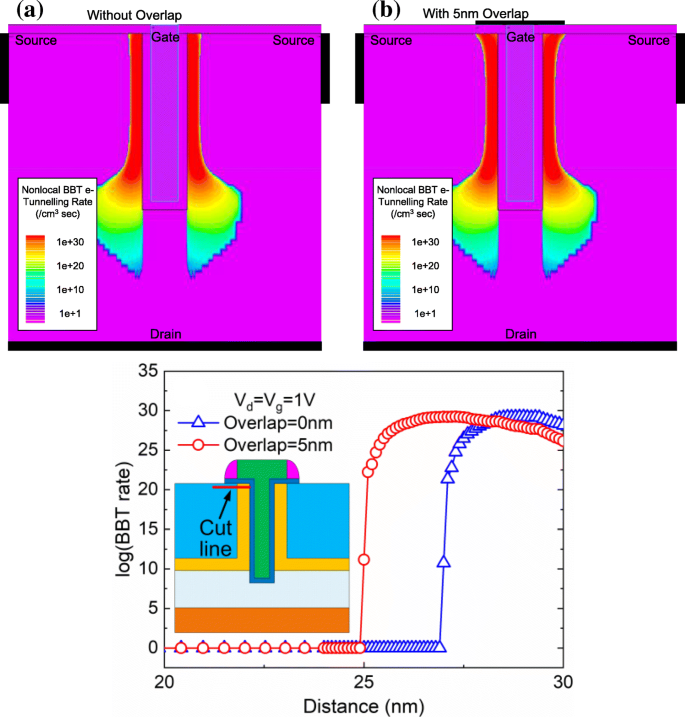

La figure 4a, b montre le taux de BBT de TGTFET avec et sans chevauchement de porte de 5 nm. À partir de la figure 4c, nous pouvons clairement voir que l'appareil avec un chevauchement de grille de 5 nm a une zone d'effet tunnel électronique plus large sous la surface de l'appareil, ce qui peut conduire au I ON augmente.

Diagrammes simulés de taux d'effet tunnel d'électrons BBT de a appareil sans chevauchement de porte, b dispositif avec chevauchement de porte de 5 nm, et c le taux d'effet tunnel électronique BBT de deux appareils, à 1 nm sous la surface de l'appareil ; V g = V d = 1 V

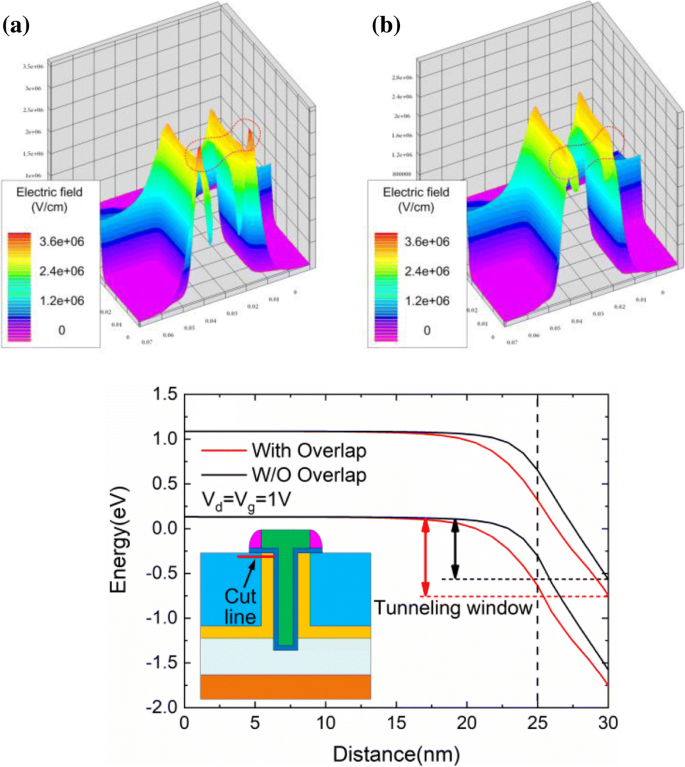

La figure 5a, b montre le diagramme 3D des champs électriques de TGTFET avec et sans chevauchement de grille. Deux pics de champ électrique apparaissent dans le TGTFET avec un chevauchement de grille de 5 nm, comme indiqué dans le cercle en pointillés de la figure 5a. Aucun pic de champ électrique n'apparaît sur la figure 5b attribué à l'absence de chevauchement de grille. La figure 5c montre la structure de la bande d'énergie sous la surface de l'appareil. L'encart de la Fig. 5c montre l'emplacement de la ligne de coupe. Avec le chevauchement de grille, une fenêtre tunnel plus grande peut être obtenue. Ainsi, un taux BBT plus élevé et I ON peut être atteint.

Schéma 3D des champs électriques de l'appareil a avec chevauchement et b sans chevauchement; c simulé diagrammes de bandes d'énergie de la source à la région de poche (1 nm en dessous de l'interface d'oxyde)

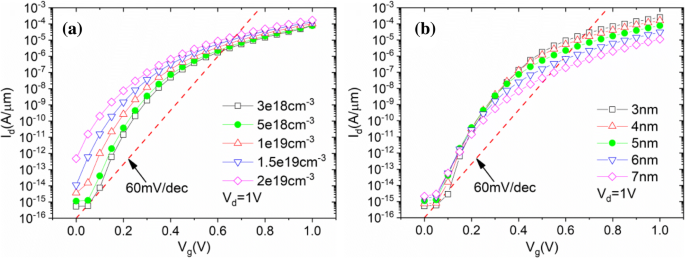

La figure 6 montre les effets de la poche n+ sur les performances du TGTFET. Le Je OFF augmente rapidement avec l'augmentation de la concentration de dopage de la poche n+, comme le montre la figure 6a. Le SS inférieur et le I supérieur ON peut être obtenu en diminuant l'épaisseur de la poche n+ (Tp) de 7 à 3 nm lorsque N P = 5 × 10 18 cm −3 , comme le montre la figure 6b. Dans le même temps, aucun courant sous-seuil significatif n'est noté sur la figure 6b. Il peut être confirmé à partir de la Fig. 6a qu'une concentration de dopage relativement faible de la poche n+ aidera à supprimer le courant sous-seuil.

Courants de drain simulés avec différentes poches n+ a concentrations et b épaisseurs à V d = 1 V

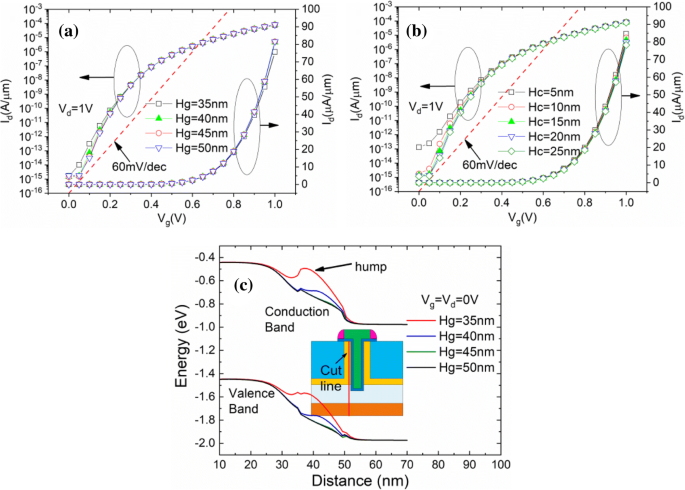

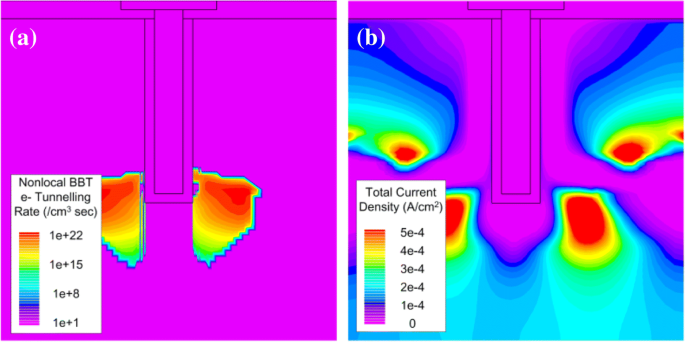

L'impact de la hauteur de la porte (Hg) et de l'épaisseur du canal (Hc) est illustré séparément sur les Fig. 7a, b. Un petit Je ON et l'amélioration de la SS apparaît lorsque le Hg augmente. Parce que lorsque Hg = 35 nm, il y a une bosse de bande d'énergie évidente sur le chemin du courant à l'état passant, devenant un certain obstacle pour les électrons chanceux (les électrons qui ont passé la jonction tunnel), comme le montre la Fig. 7c, ce qui peut entraîner Je sur diminuer. Lorsque Hg augmente, la bosse de la bande d'énergie est affaiblie, ce qui provoque le I ON et l'amélioration de la SS. Un léger Je ON l'amélioration est obtenue avec la diminution de Hc, comme le montre la figure 7b. Cependant, une dégradation sévère de la caractéristique sous-seuil peut être observée lorsque Hc diminue à 5 nm. Cela peut s'expliquer par l'augmentation du courant tunnel sous le seuil au coin de la poche n+, comme le montre la figure 8. La figure 8a montre le phénomène évident d'effet tunnel de bande à bande lorsque Hc = 5 nm tandis que la figure 8b montre le je OFF densité de courant lorsque Hc = 5 nm.

Caractéristiques de transfert simulées de TGTFET avec a Hg différent, b différents Hc, et c la bosse de la bande de conduction sur le chemin actuel

Diagrammes simulés de l'état désactivé a Taux d'effet tunnel d'électrons BTBT et b densité de courant lorsque Hc = 5 nm

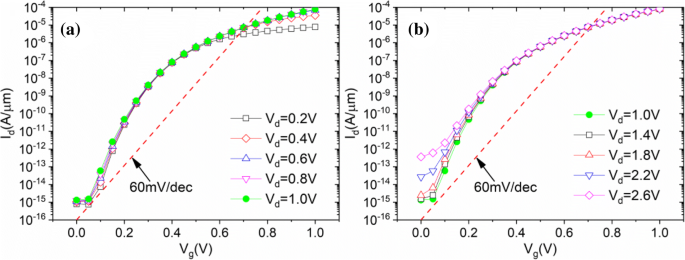

Comme le montre la figure 9, l'influence de la tension drain-source (V d ) est également pris en compte dans cet article. Pour V d < 0,6 V, I ON augmente évidemment avec l'augmentation de V d , comme le montre la figure 9a. Cela s'explique par le fait que le potentiel du canal p augmente lentement en réponse à l'augmentation du V d et entraîne la diminution de la résistance du canal p. Pour V d> 1,8 V, illustré à la Fig. 9b, le I ON n'augmente presque pas avec l'augmentation de V d , mais Je OFF augmente considérablement. Cela est dû au courant tunnel sous le seuil au coin de la poche n+ qui augmente rapidement avec l'augmentation de V d . Enfin, pour 0,6 V < V d < 1,8 V, le TGTFET présente des performances bonnes et stables. Par conséquent, le TGTFET est robuste à l'abaissement de la barrière induite par le drain (DIBL) et présente de bonnes performances stables dans une plage dynamique de tension appliquée plus large.

Courants de drain simulés pour a V d ≤ 1 V et b V d ≥ 1 V

Performances analogiques/RF de TGTFET, UTFET et LTFET

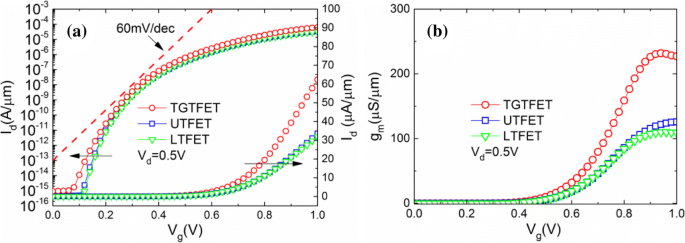

La figure 10 montre les caractéristiques de transfert et les courbes de transconductance de TGTFET, UTFET et LTFET à V d = 0,5 V. La transconductance (g m ) peut être obtenu à partir de la dérivée première de la courbe caractéristique de transfert, comme indiqué dans l'Eq. (1) [27,28,29] :

$$ {g}_{\mathrm{m}}={dI}_{\mathrm{d}s}/{dV}_{\mathrm{gs}} $$ (1)

un Caractéristiques de transfert et b courbes de transconductance de TGTFET, UTFET et LTFET à V d = 0,5 V

En conséquence, la transconductance maximale du TGTFET (232 μS/μm) est environ deux fois supérieure à celle de l'UTFET (120 μS/μm) et du LTFET (110 μS/μm), comme le montre la Fig. 10. le gain actuel contribué par la double source et le chevauchement de porte.

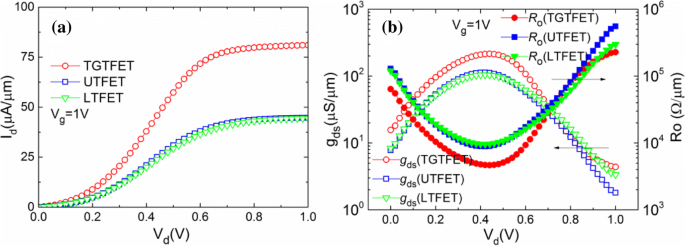

La figure 11 montre les caractéristiques de sortie, la conductance de sortie (g ds ) et l'impédance de sortie (R o ) des courbes TGTFET, UTFET et LTFET. Comme le montre la Fig. 11a, on peut clairement voir que le courant de sortie de l'appareil augmente avec l'augmentation de V d , mais quand V d atteint plus de 0,6 V, le courant de sortie a tendance à saturer. Grâce à l'observation, il est facile de constater que le courant de sortie du TGTFET est deux fois supérieur à celui de l'UTFET et du LTFET. La figure 11b montre la conductance de sortie (g ds ) et l'impédance de sortie (R o ) des courbes TGTFET, UTFET et LTFET. Le g ds peut être obtenu par la dérivation du courant de sortie, comme indiqué dans l'équation. (2) [27, 29] tandis que R o peut être exprimé comme l'inverse de la conductance de sortie.

$$ {g}_{\mathrm{ds}}={dI}_{\mathrm{ds}}/{dV}_{\mathrm{ds}} $$ (2)

un Caractéristiques de sortie, b conductance de sortie (g ds ), et c impédance de sortie (R o ) courbes TGTFET, UTFET et LTFET

En raison des avantages sur le courant de sortie, le TGTFET obtient le g le plus élevé ds et le R minimum o de ces trois appareils. Dans des conditions de polarisation de grille de 1 V, le TGTFET a obtenu le g maximum ds de 214 μS/μm et le R minimum o de 4,6 kΩ/μm sous 0,45 V V d . Dans la même condition de polarisation de grille, UTFET et LTFET ont obtenu le maximum de g ds de 113 μS/μm et 105 μS/μm et le R minimum o de 9,0 kΩ/μm et 9,6 kΩ/μm sous 0,4 V V d .

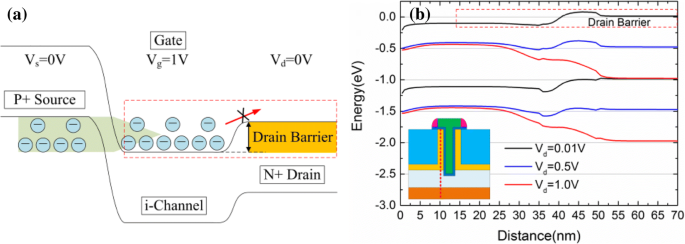

De plus, sur la figure 11, il n'est pas difficile de découvrir que la région linéaire des caractéristiques de sortie de l'appareil présente une certaine non-linéarité. Comme le montre la figure 11a, R o diminue d'abord puis augmente avec l'augmentation du V d . Certains groupes de recherche donnent le processus physique correspondant à ce phénomène [7, 30] mais il existe encore des problèmes qui n'ont pas été clairement expliqués. Comme nous le savons, R o est déterminé par la résistance de la région du canal et de la jonction tunnel. Quand V d < 0.4 V, R o diminue avec l'augmentation de V d . Considérez les situations suivantes, lorsque V d = 0 V et V g = 1 V, aucun des électrons chanceux ne peut être balayé vers le côté drain, et presque tous les électrons sont piégés dans la région du canal par une barrière de drain relativement élevée, comme le montre le cadre en pointillés rouges de la Fig. 12a, b. Lorsque 0 V < V d < 0.4 V, avec l'augmentation de V d , la barrière de drainage s'affaiblit (comme illustré à la Fig. 12b). Ainsi, les électrons piégés dans la région du canal peuvent traverser la barrière de drain puis être collectés par drain. Il s'agit d'un processus d'excitation thermique des électrons du canal au drain. Enfin, comme la jonction tunnel a été complètement allumée (lorsque V g = 1 V), le courant tunnel est toujours en excès et la résistance introduite par la jonction tunnel peut être ignorée. A ce moment, R o est déterminé par la résistance du canal et R o est décidé par le processus d'excitation thermique des électrons à travers la barrière de drain. Ainsi, R o diminue avec l'augmentation de V d . Quand V d> 0,6 V, ces trois appareils entrent progressivement dans la zone de saturation et R o devient plus grand. C'est parce que lorsque V d est grand, presque tous les électrons à travers la jonction tunnel sont balayés vers le côté drain par le champ électrique relativement élevé. Le courant tunnel devient la limite du courant de drain. Dans cette condition, R o est principalement déterminé par la jonction tunnel. Cependant, l'efficacité du tunneling ne peut pas augmenter de manière significative pendant que V d augmente. V d a un petit effet sur la structure de bande d'énergie de la jonction tunnel (côté poche n+), comme le montre la Fig. 12b. En conséquence, le courant tunnel ne peut évidemment pas augmenter, et il n'y a presque pas de I ON augmente avec le V qui augmente continuellement d (quand V d> 0,6 V), ce qui signifie qu'une impédance augmente. De plus, lorsque 0,4 V < V d < 0.6 V, R o est déterminé à la fois par la résistance du canal et la jonction tunnel.

un Schéma de principe de la bande d'énergie à V d = 0 V et V g = 1 V. b Résultats de simulation du diagramme de bande d'énergie à différents biais de V d

Il peut être obtenu de l'analyse ci-dessus que le R o du TFET est influencé à la fois par le processus d'effet tunnel et par le processus d'excitation thermique des électrons du canal. Les principaux mécanismes physiques peuvent dominer R o décalages avec V d variation. Enfin, le R o diminue d'abord puis augmente, provoquant ainsi la non-linéarité des caractéristiques de sortie. Incidemment, grâce à l'observation de la figure 11b, il est facile de constater que l'impédance de sortie du TGTFET est beaucoup plus petite que celle de l'UTFET et du LTFET. Cela est dû à la meilleure efficacité de tunnelage grâce à la structure à double source et à chevauchement de grille latérale du TGTFET.

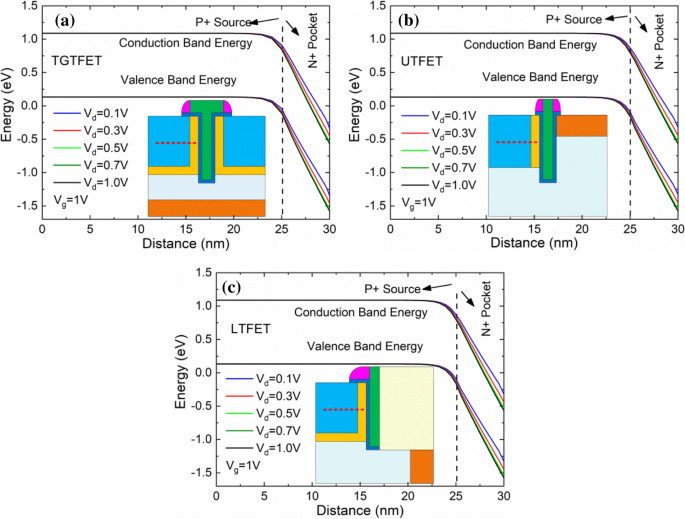

La figure 13 montre la structure de bande d'énergie de TGTFET, UTFET et LTFET avec différentes tensions appliquées. Les lignes pointillées rouges dans l'encart représentent la position pour tracer la bande d'énergie (qui se trouve à 15 nm sous la surface, juste à la moitié de la hauteur de la région source). On voit qu'avec un V d passer de 0,1 à 0,5 V, la structure de bande de TGTFET, UTFET et LTFET a une tendance évidente à la flexion. En effet, la tension de drain peut abaisser le potentiel électrique de la jonction tunnel près du côté drain. Cela indique que, pour TGTFET, UTFET et LTFET, l'augmentation de V d de 0,1 à 0,5 V est bénéfique pour l'efficacité du tunneling. Cependant, lorsque V d> 0,5 V, le changement de la bande d'énergie avec V d l'augmentation ne vaut pas la peine d'être mentionnée. Ceci est cohérent avec les résultats de l'analyse de la figure 12b.

La structure des bandes d'énergie de a TGTFET, b UTFET, et c LTFET à V g = 1

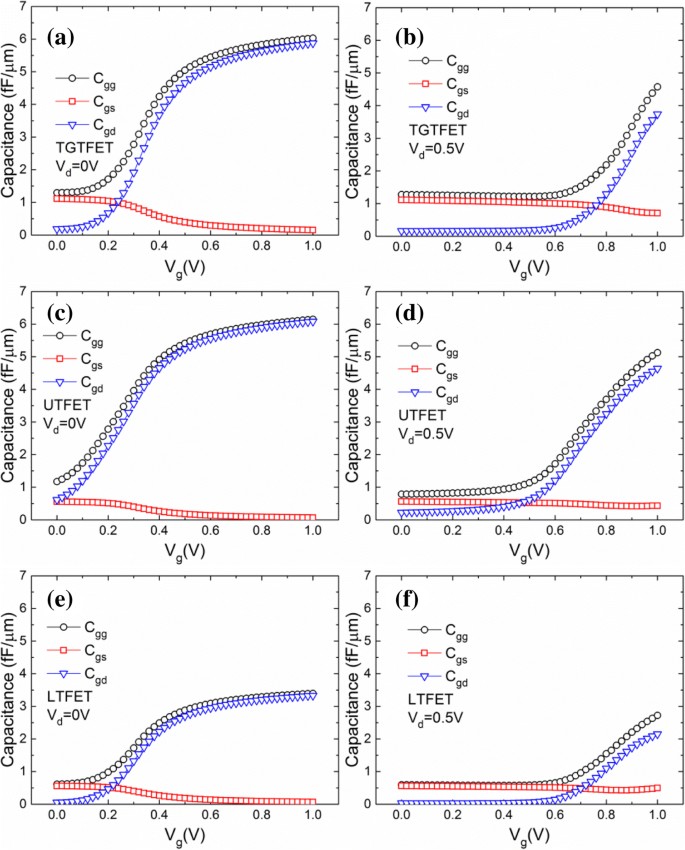

Comme nous le savons, la capacité de grille (C gg ) du dispositif peut grandement affecter les caractéristiques de fréquence des circuits intégrés. Pour TGTFET, UTFET et LTFET, C gg se compose généralement de C gs (capacité de grille à source) et C gd (capacité grille à drain). Par conséquent, la caractéristique de C gg , C gs , et C gd est d'une grande importance pour évaluer les caractéristiques de fréquence et la capacité d'application analogique des appareils. Surtout pour le TFET, les caractéristiques de capacité sont assez différentes de celles du MOSFET. En raison de l'existence de la jonction tunnel au niveau de la zone source, le TFET a généralement un petit C gs [1, 11]. Par conséquent, le C gg de TFET est principalement déterminé par C gd . La figure 14 montre la capacité de TGTFET, UTFET et LTFET par rapport à V g sous V d = 0,5 V et V d = 0 V, séparément.

Capacité du TGTFET versus V g sous a V d = 0 V et b V d = 0,5 V. Capacité de l'UTFET par rapport à V g sous c V d = 0 V et d V d = 0,5 V. Capacité du LTFET par rapport à V g sous e V d = 0 V et f V d = 0,5 V

Grâce à l'observation de la Fig. 14a, b, il est facile de trouver que le C gs de TGTFET sous une tension de grille de 1 V est de 0,15 fF/μm à V d = 0 V et 0,7 fF/μm à V d = 0,5 V, ce qui est bien plus petit que celui du C gd (5,8 fF/μm à V d = 0 V et 3,7 fF/μm à V d = 0,5 V). Ainsi, le C gg de TGTFET est principalement déterminé par C gd . Quand V d = 0 V, C gg et C gd augmenter rapidement avec l'augmentation du V g , comme le montre la figure 14a. C'est parce qu'avec l'augmentation de V g , les électrons sont agrégés à l'interface de grille dans le canal du dispositif, ce qui fait augmenter rapidement la capacité. Quand V d = 0,5 V, C gd n'augmente évidemment pas jusqu'à ce que V g est augmentée à plus de 0,6 V, comme le montre la figure 14b. C'est parce que lorsque V g est faible, seuls quelques électrons chanceux peuvent traverser la jonction tunnel et entrer dans le canal. Certains de ces électrons chanceux participeront au processus de recombinaison, et la plupart des autres seront rapidement collectés par le drain en raison de la tension de drain de 0,5 V. Par conséquent, il est très difficile pour ces électrons chanceux de rester dans le canal de l'appareil. Cependant, avec le V g augmenter, le nombre d'électrons chanceux augmente rapidement. À ce moment, ni la collection de drains ni le processus de recombinaison électron-trou ne peuvent épuiser rapidement ces électrons chanceux. Ainsi, la concentration en électrons dans le canal augmente et la capacité augmente rapidement. En conséquence, la courbe caractéristique de capacité a tendance à se déplacer vers la droite tandis que V d augmente, comme le montre la Fig. 14a, b. L'analyse et les phénomènes ci-dessus sont également applicables à UTFET et LTFET, comme le montre la Fig. 14c–f. De plus, la capacité de grille de l'UTFET à 0 V et 0,5 V V d a atteint 6,2 fF/μm et 5,1 fF/μm, respectivement, et celle du LTFET a atteint 3,4 fF/μm et 2,7 fF/μm, respectivement.

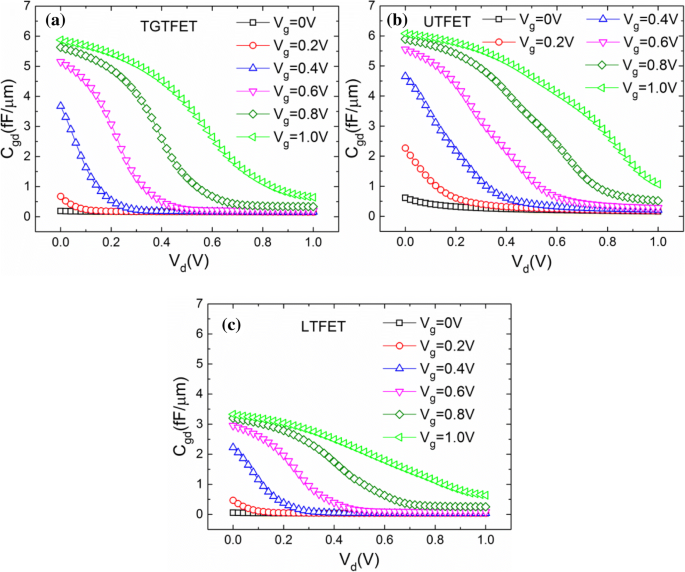

Comme il n'y a pas de chevauchement direct entre la grille et le drain du LTFET et que la distance entre la grille et le drain est relativement importante, le LTFET a les meilleures caractéristiques de capacité et le plus petit C gg . En revanche, il y a un chevauchement direct entre la grille et le drain de l'UTFET. Par conséquent, les électrons près du côté drain sont plus facilement contrôlés par la grille, ce qui entraîne un grand C gg de l'UTFET. Pour le TGTFET, bien que la distance entre la grille et le drain soit proche, mais il existe une région de canal légèrement dopée qui peut isoler la grille et le drain. Ainsi, la capacité du TGTFET est meilleure que celle de l'UTFET, mais légèrement inférieure au LTFET. La figure 15 montre le C gd caractéristiques de TGTFET, UTFET et LTFET par rapport à V d sous différents V g . D'après l'observation des Fig. 15a–v, il n'est pas difficile de trouver que le C gd les caractéristiques de ces trois appareils sont similaires. C'est-à-dire pour un V fixe g , C gd diminue avec l'augmentation du V d . En revanche, pour un V fixe d , C gd augmente avec l'augmentation de V g .

C gd caractéristiques de a TGTFET, b UTFET, et c LTFET contre V d sous différents V g

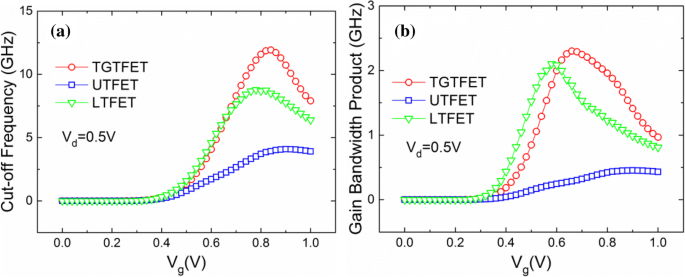

Comme nous le savons, la fréquence de coupure (f T ) et la bande passante de gain (GBW) sont les critères d'évaluation pour évaluer les caractéristiques de fréquence des appareils. f T dépend du rapport de g m à C gg , comme le montre l'éq. (3) [30, 31]. Pour un certain gain DC égal à 10, GBW peut être exprimé par le rapport de g m à C gd , comme le montre l'éq. (4) [17] :

$$ {f}_T=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gs}}\sqrt{1+2{C}_{\mathrm{gd} }/{C}_{\mathrm{gs}}}}\approx \frac{g_{\mathrm{m}}}{2\pi \left({C}_{\mathrm{gs}}+{C }_{\mathrm{gd}}\right)}=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gg}}} $$ (3) $$ \ mathrm{GWB}={g}_{\mathrm{m}}/2\pi 10{C}_{\mathrm{gd}} $$ (4)La figure 16 montre les courbes caractéristiques du f T et GBW de TGTFET, UTFET et LTFET. Bénéficiant d'avantages structurels, tels que le chevauchement de grille à double source et latéral introduit par la grille en forme de T, le TGTFET obtient les caractéristiques de fréquence les plus remarquables par rapport à l'UTFET et au LTFET. Sous la condition de V d = 0,5 V, le f T et GBW de TGTFET ont atteint les valeurs maximales de 11,9 GHz et 2,3 GHz, respectivement. Bénéficiant de la grande distance entre grille et drain et sans chevauchement grille/drain, LTFET obtient un petit C gg et de bonnes caractéristiques de fréquence. Le f T et GBW de LTFET atteignent les 8,7 GHz et 2,1 GHz, séparément. Les caractéristiques de capacité de l'UTFET sont inférieures à celles du TGTFET et du LTFET. This is because the direct gate/drain overlaps. As a result, the maximum value of f T and GBW of UTFET can only reach 4.1 GHz and 0.5 GHz separately.

The characteristic curves of a f T et b GBW of TGTFET, UTFET, and LTFET versus V g at V d = 0.5 V

Conclusions

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON /Je OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd et C gg . Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

Abréviations

- C gd :

-

Gate to drain capacitance

- C gs :

-

Gate to source capacitance

- f T :

-

Cut-off frequency

- GBW:

-

Gain bandwidth

- g ds :

-

Output conductance

- g m :

-

Transconductance

- Hc:

-

Height of the channel layer

- Hg:

-

Height of the gate electrode

- Hs:

-

Height of the source layer

- LTFET:

-

L-shape gate tunnel field-effect transistor

- N D :

-

Doping concentration of n+ drain

- N P :

-

Doping concentration of n+ pocket

- N S :

-

Doping concentration of p+ source

- N sous :

-

Doping concentration of p− substrate

- R o :

-

Output impedance

- TGTFET:

-

T-shape gate dual-source tunnel field-effect transistor

- Tox:

-

Thickness of the HfO2 gate dielectric

- Tp:

-

Thickness of n+ pocket

- UTFET:

-

U-shape gate tunnel field-effect transistor

- V d :

-

Drain to source voltage

- V g :

-

Gate to source voltage

- Wg:

-

Width of the gate electrode

Nanomatériaux

- Transistors, jonction effet de champ (JFET)

- Transistors, effet de champ à grille isolée (IGFET ou MOSFET)

- Transistors à effet de champ de jonction

- Transistors à effet de champ à grille isolée (MOSFET)

- Le transistor à effet de champ à jonction (JFET) en tant que commutateur

- Tunnel

- Le premier transistor de température ambiante tout optique ultrarapide au monde

- Performances photocatalytiques induites par la lumière visible des nanocomposites ZnO/g-C3N4 dopés N

- Préparation et performances photocatalytiques des photocatalyseurs à structure creuse LiNb3O8