Clé d'innovation matérielle jusqu'à 7 nm et au-delà

Alors que notre équipe de recherche sur les semi-conducteurs à Albany, NY continue de faire évoluer la technologie CMOS vers les futurs nœuds - jusqu'à 10 nm, 7 nm et au-delà - la résistance du canal du transistor qui détermine le flux de courant et la façon dont nous nous y connectons, continue de jouer un rôle de plus en plus important dans les performances globales d'une puce. Ainsi, afin d'assurer la compétitivité des performances d'une future technologie de semi-conducteur donnée, l'innovation des matériaux de canal pour réduire la résistance du canal des transistors est un domaine d'étude critique. C'est pourquoi nous explorons le silicium germanium (SiGe) - les éléments nécessaires pour obtenir les avantages en termes de performances énergétiques décrits dans l'annonce de la puce 7 nm de l'année dernière.

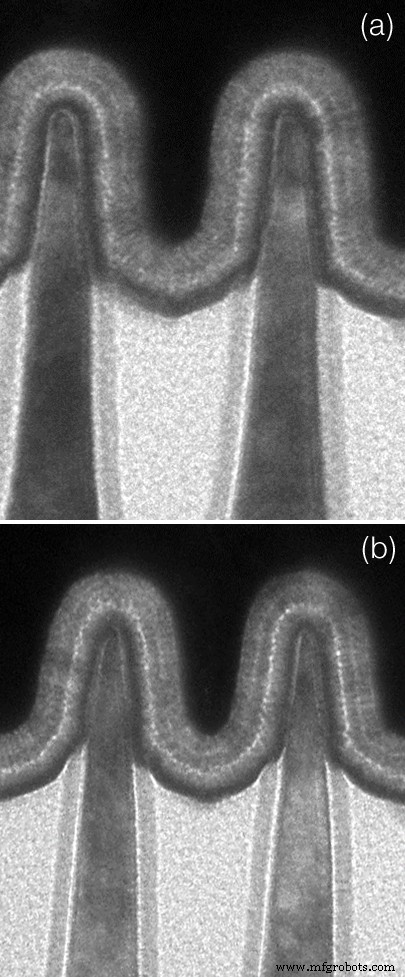

Symétrique Si Profils FinFET (a) et SiGe FinFET (b) à 10 nm réalisés par IBM Research au complexe NanoTech de SUNY Polytechnic à Albany, NY. Cela illustre que SiGe Fin peut fournir des propriétés électriques supérieures à Si Fin.

Les puces à base de FinFET* à nœud 14 nm d'aujourd'hui utilisent des canaux uniquement en silicium (le silicium n'est pas stable au-delà de cette échelle). La technologie FinFET basée sur SiGe, alternativement, a démontré une amélioration des performances avec les règles de base de la technologie 10 nm (normes de l'industrie), fournissant des solutions élégantes vers une option de technologie CMOS viable. L'une de ces solutions SiGe FinFET élégantes est sa capacité à prendre en charge les appareils à faible consommation et à hautes performances sur la même puce, sans perte de performances ou de variabilité d'un type d'appareil par rapport à l'autre.

La technologie SiGe FinFET offre également une fiabilité électrique supérieure par rapport au Si FinFET. Et cela conduit à une meilleure stabilité des performances au niveau de la puce que le Si FinFET sur la durée de vie de la puce. Cela signifie que le même flux d'intégration de processus convient aux conceptions de superordinateurs ainsi qu'aux conceptions mobiles.

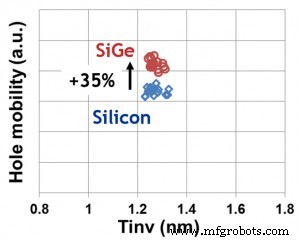

SiGe repousse les limites de la mise à l'échelle des puces en modifiant la façon dont le courant passe à travers le canal d'un transistor. Il s'avère qu'en ajoutant des atomes de germanium plus gros à un cristal composé d'atomes de silicium plus petits, le cristal développe un décalage de réseau, générant une contrainte dans le canal du transistor. Cette contrainte permet de déplacer plus de courant à travers le canal à des tensions plus basses. Ainsi, en utilisant SiGe comme matériau de canal, nous pouvons tracer une feuille de route à des dimensions plus petites tout en maintenant un équilibre entre puissance et performances.

SiGe pour les nœuds à venir :relever les défis de la production de puces 10 nm et 7 nm

La rétention des contraintes tout au long du flux d'intégration, ainsi que le contrôle des défauts, sont deux des principaux défis techniques pour la production de SiGe FinFET à un nœud de 10 nm et moins. Les canaux des transistors pourraient perdre de la tension pendant les processus de recuit thermique qui activent les dopants et stabilisent l'intégrité des transistors ; ou pendant les processus d'évidement source/drain qui forment la jonction uniforme du haut de l'aileron au bas de l'aileron ; ou même le motif des ailerons dans des conceptions spécifiques qui nécessitent des ailerons courts.

Le contrôle des défauts est également essentiel dans la production en série d'une technologie CMOS. Avec le décalage de réseau entre un canal SiGe et son substrat de plaquette de silicium, il est difficile de maintenir le niveau de défaut de fabrication requis sur l'ensemble de la plaquette. Mais avec notre gestion avancée de la croissance épitaxiale (cristal), l'intégration innovante du processus du module Fin et l'ingénierie source/drain, nous avons développé des solutions pour garantir la contrainte dans le canal tout au long du flux d'intégration, tout en maintenant une faible défectivité dans nos tests 10 nm et 7 nm nœuds.

Avec cette étude de faisabilité complète de la technologie SiGe FinFET aux règles de base de la technologie 10 nm, nous travaillons maintenant avec des concepteurs et des fabricants de puces pour produire en masse la technologie SiGe FinFET. Je prévois que notre technologie SiGe FinFET remplacera le silicium FinFET dans la prochaine génération de nœuds technologiques CMOS pour des utilisations informatiques, allant des superordinateurs aux appareils mobiles. Ils pourraient également être utilisés dans des applications « plus que Moore » dans le cloud et l'informatique cognitive, où une faible alimentation et une faible consommation d'énergie sont hautement souhaitables, telles que les applications dans le cloud et l'informatique cognitive.

Autres lectures

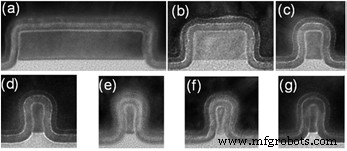

Coupes transversales de la pile d'ailerons et de portes pour une largeur d'aileron allant de 87 nm (a) à 3 nm (g) pour une teneur en Ge plus élevée pour l'aileron SiGe.

Lors du symposium IEEE de cette année sur la technologie VLSI (intégration à très grande échelle), nos équipes ont présenté un certain nombre de nouveaux dispositifs, matériaux et innovations d'intégration centrés sur l'utilisation de SiGe avec des règles de base de 10 nm, et également comme voie à suivre pour résoudre la mise à l'échelle et les problèmes de performances du nœud de test 7 nm que nous avons fabriqué l'année dernière.

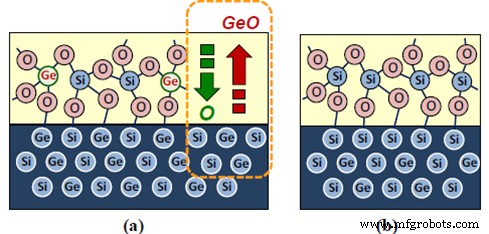

Nos présentations ont couvert les caractéristiques techniques critiques et l'innovation fondamentale des processus pour le contrôle des défauts ; innovations dans la pile de portes et la couche interfaciale adaptées à SiGe FIN ; ainsi que des techniques de contact avancées sur la plate-forme SiGe FinFET, rapportées dans le document de recherche T2.2 lors de la conférence VLSI. L'article de recherche T4.3 présentait le procédé inventif d'élimination sélective de l'oxyde de germanium pour construire une couche interfaciale robuste pour le canal SiGe.

Mobilité claire avantage de SiGe Fin sur Si Fin, conduisant à un gain de performances au niveau de la puce.

Notre recherche dirigée par le Dr Pouya Hashemi qui se concentre sur l'extensibilité de la technologie SiGe FinFET pour les futurs nœuds plus performants a également été présentée au VLSI. Dans le document de recherche T9.3, nous avons signalé la possibilité d'atteindre des performances plus élevées avec une teneur en Ge plus élevée et une largeur d'aileron plus petite et une mise à l'échelle supplémentaire de la pile de portes. Les participants au Symposium VLSI peuvent trouver ces documents techniques sur le site Web du VLSI. Vous pouvez également rejoindre leur groupe Linkedin pour plus d'informations.

T2.2 :Technologie FINFET avec canal SiGe à haute mobilité pour 10 nm et au-delà

T4.3 :GeO sélectivex -Récupération de la couche interfaciale sur Si1-x Gex Canal pour haute mobilité Si/Si1-x Gex Application CMOS

T9.3 :FinFET SiGe tendus à haute teneur en K/porte métallique de remplacement avec une mobilité élevée des trous et un excellent SS et une fiabilité à EOT agressif ~ 7Å et des dimensions réduites jusqu'à des largeurs d'aileron inférieures à 4 nm

T7.2 :Contacts en siliciure de revêtement Ti et NiPt/Ti pour les technologies avancées

Schéma de le procédé inventif de piégeage sélectif de GeOx (a) et la couche interfaciale sans GeOx (b) avec canal SiGe.

*-FinFET fait référence à une architecture de transistor qui élève le canal du transistor pour qu'il ressemble à des ailettes)

Dechao Guo est membre du personnel de recherche, maître inventeur et responsable de la conception et de l'intégration de périphériques avancés chez IBM Research.

Nanomatériaux

- Vers Cloud Infinity et au-delà

- IBM chez SPIE :sept avancées pour les puces au-delà de 7 nm

- IoT au-delà du PoC :un changement de mentalité

- Technologie des jumeaux numériques :au-delà de la science des fusées

- La vision artificielle est la clé de l'industrie 4.0 et de l'IoT

- Missouri Technology Corporation va lancer une initiative d'entrepreneuriat et d'innovation à l'échelle de l'État

- Comment l'IoT et l'automatisation industrielle stimulent l'innovation

- La collaboration est essentielle pour les entreprises européennes de fabrication et de technologie de pointe (AMT)

- AMRC stimule l'innovation dans la technologie et l'économie circulaire