Comment rendre les processeurs dignes de confiance

Les circuits intégrés (CI) modernes fournissent les capacités de calcul et de contrôle du système pour traiter d'énormes quantités de données, prendre des décisions critiques pour la sécurité en temps réel et protéger les données sensibles. La conception d'un circuit intégré spécifique à une application (ASIC) ou d'un système sur puce (SoC) à matrice de portes programmable sur site (FPGA) à partir de zéro serait excessivement coûteuse et prendrait beaucoup de temps. De nombreuses fonctions critiques sont implémentées à l'aide de propriétés intellectuelles (IP) tierces. Les cœurs de processeur, par exemple, proviennent d'organisations spécialisées et fournissent une fonction flexible et programmable par logiciel grâce à leur architecture de jeu d'instructions (ISA), qui définit l'interface entre le matériel et le logiciel. Les architectures de processeur open source offrent la possibilité d'un examen plus approfondi et d'une assurance de sécurité rigoureuse dans les systèmes qui sont déjà confrontés à un environnement de menace fluide. Cet article décrit une approche pour fournir une assurance de sécurité d'IP et de SoC basée sur l'ISA open source RISC-V.

Inventé à l'Université de Californie et géré par la fondation à but non lucratif RISC-V, RISC-V est le premier ISA open source à devenir un choix industriel véritablement viable pour un large éventail d'applications.

RISC-V est un ISA open source inventé à l'Université de Californie et géré par la Fondation RISC-V, une organisation à but non lucratif avec plus de 300 membres fondée en 2015. RISC-V est le premier ISA open source à devenir un un choix industriel véritablement viable pour un large éventail d'applications. L'écosystème d'outils, de logiciels et d'expertises est solide et en croissance constante. De nombreuses personnes et organisations ont déjà fait don d'adresses IP matérielles open source mettant en œuvre l'ISA RISC-V. Le groupe OpenHW, par exemple, vise à faire de la perspective tant attendue du matériel open source, en particulier des cœurs de processeur, une réalité pour les puces à grand volume.

L'essor de RISC-V a de nombreuses raisons. Construit à partir de zéro avec une extensibilité personnalisée à l'esprit, RISC-V permet un nouveau niveau d'optimisation matérielle pour des charges de travail spécifiques. La loi de Moore ralentit et la personnalisation est cruciale pour maintenir le niveau d'amélioration des performances que les avancées technologiques dans le processus de fabrication des semi-conducteurs ne peuvent plus fournir. De plus, l'architecture RISC-V est exempte de coûts de licence et de redevances, permettant à davantage d'entreprises de développer des produits innovants et abordables. Il se passe beaucoup de choses dans le domaine de l'IoT et des appareils portables dotés de capacités d'intelligence artificielle, par exemple.

Les intégrateurs SoC utilisent souvent des IP de processeur RISC-V open source ou tiers. Ces conceptions et leurs chaînes d'outils associées peuvent être complétées par des instructions personnalisées. Un environnement de vérification de haute qualité fourni avec l'IP et des tests supplémentaires au niveau du système peuvent fournir une certaine assurance que l'IP n'a pas de bogues critiques. Malheureusement, pour de nombreuses applications, cela ne suffit pas, et il existe d'autres risques sérieux à prendre en compte.

Vulnérabilités et chevaux de Troie

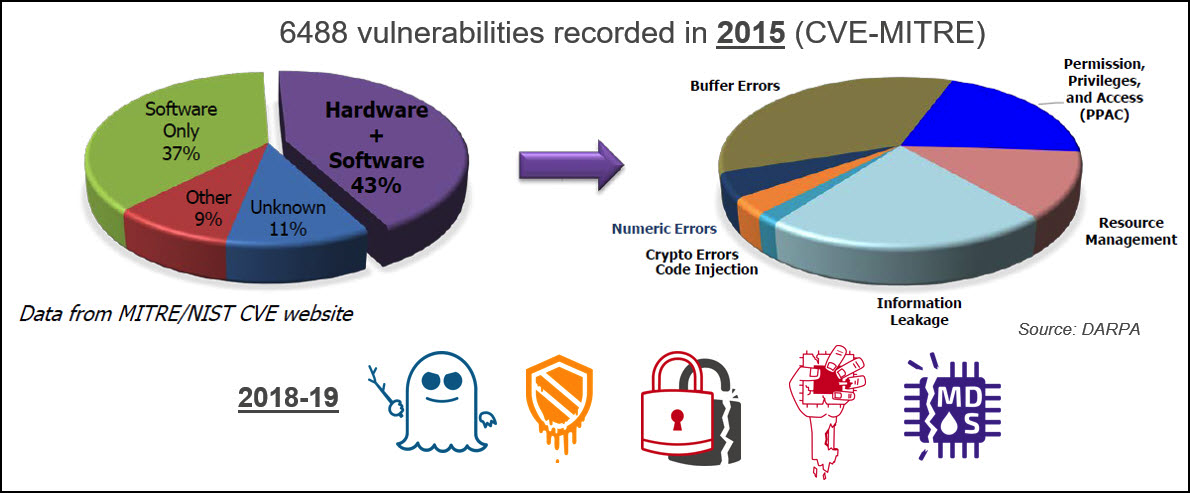

Traditionnellement, les vulnérabilités de sécurité dans les systèmes électroniques ont été associées à des problèmes au niveau du système et des logiciels. Plus récemment, les adresses IP matérielles, principalement les processeurs, sont également devenues une préoccupation centrale (voir Fig. 1). Les implémentations de processeurs utilisent des microarchitectures basées sur des pipelines et incluent souvent des fonctionnalités d'optimisation des performances et de la puissance. La complexité augmente le risque de manquer non seulement des bogues fonctionnels, mais également des vulnérabilités de sécurité. Les chercheurs en sécurité qui ont découvert les attaques Meltdown et Spectre au début de 2018 ont démontré que les fonctionnalités d'optimisation des performances des processeurs peuvent être utilisées de manière non intentionnelle à des fins néfastes. Depuis lors, de nombreuses autres vulnérabilités ont été découvertes dans les processeurs haut de gamme et bas de gamme. Les canaux secondaires et les attaques d'exécution transitoire peuvent violer des enclaves sécurisées et permettre à des applications malveillantes de divulguer des données confidentielles ou même de prendre le contrôle du système. Et contrairement aux logiciels, les problèmes matériels ne peuvent pas être facilement réparés avec des mises à jour sans fil. La résolution d'un problème matériel via un logiciel entraîne souvent une grave dégradation des performances.

L'architecture RISC-V possède de nombreuses fonctionnalités qui prennent en charge la mise en œuvre de systèmes embarqués sécurisés. La spécification de privilège définit quatre modes de privilège (machine, superviseur, hyperviseur et utilisateur), par exemple. Les instructions personnalisées et les extensions ISA en cours de ratification, telles que l'extension Cryptographic, offrent des capacités de sécurité supplémentaires. Les concepteurs peuvent implémenter plusieurs enclaves sécurisées pour isoler les applications et empêcher la fuite de données sensibles. Cependant, les fonctionnalités micro-architecturales RTL peuvent toujours entraîner des failles de sécurité. Ces risques ne peuvent pas être entièrement traités au niveau de l'ISA. Une nouvelle approche en cours d'exploration est l'utilisation d'un ISA augmenté (aISA) pour définir les aspects de l'exécution des instructions au niveau micro-architectural et, par exemple, contrôler l'état des tampons ou des registres non visibles au niveau ISA. Des bugs fonctionnels de RTL pourraient encore compromettre toutes ces fonctionnalités de sécurité.

Un risque moins probable mais avec une gravité beaucoup plus élevée est la présence d'une logique malveillante ou de chevaux de Troie matériels dans le noyau RISC-V. Un cheval de Troie matériel est une fonction logique délibérément conçue pour être furtive, qui s'active dans de très rares circonstances connues uniquement de l'attaquant. Une séquence spécifique d'événements de données et de contrôle qui ne se produirait pas pendant que le système fonctionne dans ses cas d'utilisation cibles déclenche la logique du cheval de Troie, qui à son tour fournit une charge utile dommageable, divulguant un secret ou corrompant de manière critique le comportement du système, par exemple. Les intégrations SoC utilisant des cœurs RISC-V open source ou tiers ne peuvent plus ignorer ce risque.

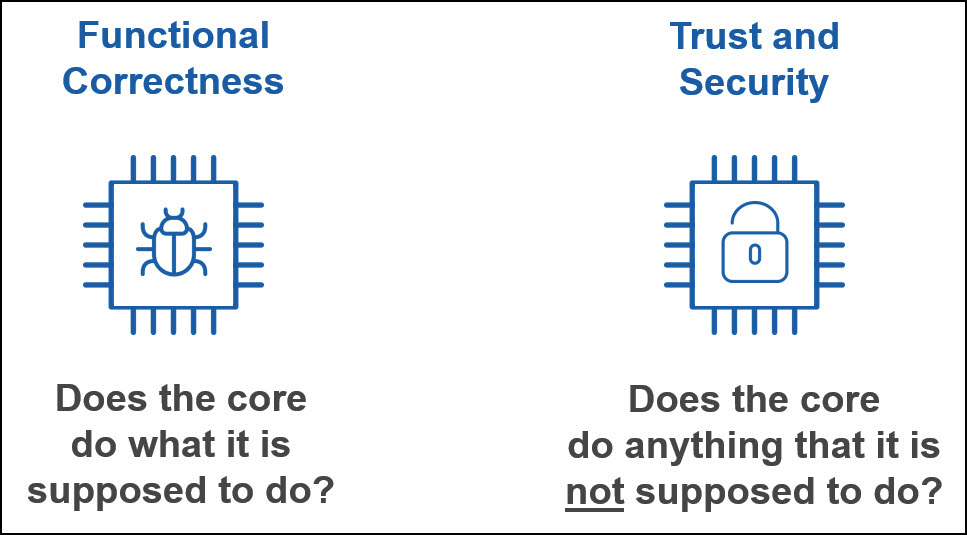

Veiller à ce qu'un processeur fasse ce qu'il est censé faire est difficile, mais s'assurer qu'il ne fait rien d'autre qu'il n'est pas censé faire est une tâche encore plus ardue qui reste en grande partie sans réponse. Les systèmes et systèmes critiques pour lesquels la protection de la confidentialité des données est primordiale, ont besoin de solutions efficaces et de haute qualité qui traitent le risque de failles de sécurité et de chevaux de Troie.

Figure 1 :La base de données CVE-MITRE a enregistré 6488 vulnérabilités en 2015, dont 43% peuvent être classées comme des vulnérabilités matérielles assistées par logiciel. En 2018 et 2019, des chercheurs ont découvert et signalé de nombreuses vulnérabilités dans les processeurs, notamment Meltdown et Spectre, Foreshadow, ZombieLoad, et RIDL et Fallout. (Source :DARPA et OneSpin)

Assurance matérielle intelligente

Assurer la confiance et la sécurité des IP RISC-V nécessite des solutions techniques innovantes et efficaces qui sont complémentaires aux approches de correction fonctionnelle, ciblant principalement les cas d'utilisation IP visés (voir Fig. 2). Les fournisseurs IP sont chargés d'appliquer des processus de vérification de confiance et de sécurité de pointe, tandis que les intégrateurs IP doivent avoir accès à des solutions d'assurance indépendantes qui peuvent être déployées rapidement et sans connaissance approfondie des détails de la mise en œuvre IP.

Les méthodes formelles peuvent analyser les fonctions matérielles de manière exhaustive et fournir la preuve que l'IP ou le SoC correspond précisément à un comportement attendu souvent capturé dans les assertions SystemVerilog. La vérification formelle du matériel à l'aide de vérificateurs de modèles commerciaux a été largement adoptée au cours de la dernière décennie. En règle générale, les fournisseurs d'IP et les intégrateurs de SoC ont des experts en vérification formelle dans leurs rangs, essayant de réduire au minimum le risque de manquer des bogues fonctionnels. Alors que certaines tâches de vérification formelle bien définies peuvent être automatisées via des Apps , en général, un effort d'ingénierie important est nécessaire pour capturer le comportement attendu de l'IP dans les assertions. De plus, il n'y a aucune garantie que suffisamment d'affirmations ont été écrites. Des fonctions non documentées ou des lacunes involontaires dans l'ensemble d'assertions pourraient conduire à une fonctionnalité IP non vérifiée.

La nature open source de RISC-V permet le développement de solutions d'assurance indépendantes et préconditionnées. La solution de vérification d'intégrité RISC-V de OneSpin, par exemple, peut être appliquée à un large éventail de microarchitectures. Il comprend des modèles d'ISA RISC-V et d'ISA privilégié qui sont extensibles et peuvent accueillir des instructions personnalisées. Un aspect crucial de cette solution est qu'elle est basée sur le processus GapFreeVerification™ de OneSpin, qui fournit une preuve rigoureuse que l'ensemble d'assertions modélisant l'ISA RISC-V est complet et exempt de lacunes. Cet aspect est de la plus haute importance lorsque la détection de chevaux de Troie matériels ou de logiques non documentées est un objectif crucial. La solution permet aux intégrateurs SoC ayant une expertise limitée sur RISC-V et la mise en œuvre RTL examinée de gagner en confiance dans la qualité et la fiabilité de l'IP. Les développeurs IP peuvent l'utiliser pour détecter les failles de sécurité et les bogues fonctionnels avant la publication.

Figure 2 :La vérification de l'exactitude fonctionnelle garantit qu'une implémentation de processeur se comporte comme spécifié et satisfait aux exigences des utilisateurs finaux. La vérification de la confiance et de la sécurité, en revanche, garantit que le processeur n'a pas de fonctions non documentées, de canaux secondaires imprévus, de chevaux de Troie matériels ou d'autres vulnérabilités qui pourraient être exploitées par des acteurs malveillants. (Source :OneSpin)

Ça marche ?

Le processus d'assurance d'intégrité RISC-V décrit dans la section précédente a été appliqué avec succès à plusieurs conceptions RTL. Edaptive Computing, une entreprise qui intègre des solutions innovantes pour optimiser, assurer et automatiser rapidement des systèmes de systèmes et de processus pour une variété de clients du département américain de la Défense et du secteur commercial, a appliqué le processus au RocketCore, par exemple. Le RocketCore est un cœur RISC-V 64 bits à code source ouvert et éprouvé avec un système de mémoire virtuelle de 39 bits. Il dispose d'un pipeline en cinq étapes, à problème unique, dans l'ordre, avec achèvement dans le désordre pour les instructions à longue latence telles que la division. Il inclut les fonctionnalités avancées de prédiction de branchement et de relecture d'instructions.

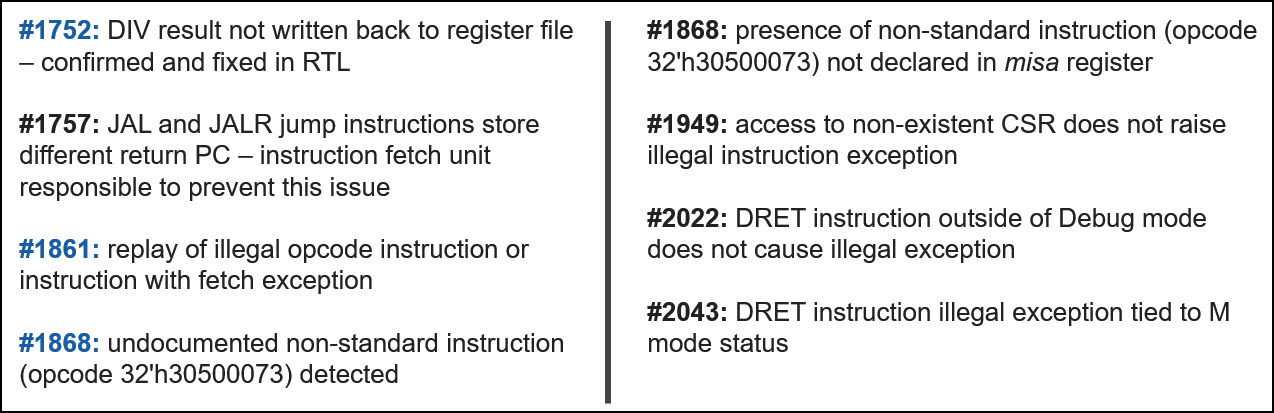

La solution de vérification de l'intégrité RISC-V a été appliquée à la conception avec toutes les instructions, les niveaux de privilège, les interruptions et le mécanisme d'exception, et 8 problèmes ont été détectés (voir Fig. 3). Des informations supplémentaires sur 3 d'entre eux sont rapportées ci-dessous.

Division corner-case :un bug grave associé à l'achèvement dans le désordre de l'instruction de division. Ce problème aurait pu provoquer un programme logiciel utilisant l'opération de division pour calculer des résultats incorrects et entraîner un mauvais comportement du système. Le problème n'apparaît que dans une combinaison de circonstances rares, et c'est pourquoi les efforts de vérification précédents l'avaient manqué.

Relecture de l'instruction illégale :ce n'est pas un bug du coin. La relecture d'une instruction illégale peut gaspiller des cycles de traitement, mais si cela ne se produit que dans de rares situations, l'impact sur les performances est négligeable. Cependant, il y a d'autres aspects à considérer. La relecture des instructions peut entraîner des demandes de mémoire inutiles. Ces demandes peuvent avoir des effets secondaires qui pourraient être exploités dans les attaques par canaux secondaires. Par conséquent, ce comportement doit être soit éliminé, soit clairement compris et documenté.

Instruction non documentée :une instruction non-standard non documentée appelée CEASE qui arrête le noyau a été détectée. En effet, le RISC-V RocketCore pouvait faire quelque chose qu'il n'était pas censé faire. Les fonctions cachées et non documentées ne sont pas acceptables lorsque la confiance et la sécurité sont un problème, même lorsqu'elles concernent des cas d'utilisation jugés non pertinents pour l'application finale.

L'étude de cas RocketCore est présentée en détail dans l'article GOMACTech 2019 intitulé Complete Formal Verification of RISC-V Processor IPs for Trojan-Free Trusted ICs. Pour obtenir une copie, visitez onespin.com/resources/white-papers.

Figure 3 : liste des problèmes détectés par les solutions de vérification d'intégrité RISC-V de OneSpin et signalés dans le projet GitHub RocketCore. (Source :OneSpin)

Quelle est la prochaine étape ?

Le processus d'assurance RISC-V présenté dans cet article détecte les scénarios qui pourraient affecter la sécurité et dévoile systématiquement les fonctions non documentées et les chevaux de Troie matériels qui ont un impact sur le comportement du processeur, quelle que soit leur rareté et leur furtivité. Cependant, les canaux secondaires ne sont pas systématiquement détectés. La détection exhaustive de tous les canaux secondaires potentiels nécessite une solution dédiée dotée d'une technologie appropriée. Il existe déjà des prototypes qui relèvent ce défi. Pour plus d'informations, rendez-vous sur onespin.com/resources/technical-articles et lisez l'article de l'EE Times Attaques latérales contre les processeurs intégrés.

Les cœurs de processeur sont des IP cruciales dans les systèmes embarqués. Cependant, un SoC typique intègre de nombreuses autres adresses IP qui peuvent également contenir des chevaux de Troie matériels. Contrairement aux cœurs RISC-V, les solutions d'assurance de confiance indépendantes peuvent ne pas être facilement disponibles. Dans ce cas, il serait utile de disposer d'un processus d'évaluation de la confiance automatisé et à faible effort applicable à toute propriété intellectuelle. Un processus qui n'inclut pas un modèle de confiance de l'IP ne peut pas garantir l'absence d'un cheval de Troie. Cependant, il est possible d'identifier des modèles de code inhabituels et suspects et des signatures de chevaux de Troie connues, ainsi que des faiblesses qui pourraient être exploitées dans des étapes de développement ultérieures à des fins malveillantes. Un article sur ce sujet intitulé An Automated Pre-Silicon IP Trustworthiness Assessment for Hardware Assurance , rédigé par AEROSPACE Corporation et les ingénieurs de OneSpin, sera présenté à la conférence GOMACTech 2020.

Embarqué

- Comment tirer le meilleur parti de vos données

- Comment créer une plate-forme robotique Arduino+Raspberry Pi

- Comment fabriquer de la fibre de verre

- Comment rendre les données de la chaîne d'approvisionnement fiables

- Comment faire une animation en coupe dans Solidworks

- Comment faire un prototype

- Comment remplacer un tuyau hydraulique

- Comment faire fonctionner un programme de sécurité complet

- Comment fabriquer un mandrin de tour à métaux