Un modulateur Delta-Sigma en temps continu avec une bande passante de 100 MHz et une plage dynamique de 80 dB avec une fréquence d'horloge de 2,4 GHz

Résumé

La bande passante d'un Δ Σ modulateur est limité par la fréquence d'horloge en raison de l'exigence de taux de suréchantillonnage. Comme les processus CMOS à l'échelle nanométrique se développent rapidement, il est possible de concevoir une large bande passante et une plage dynamique élevée en temps continu Δ Σ modulateurs pour applications haute fréquence. Cet article propose un Δ en temps continu à 4 bits d'ordre 3 Σ modulateur avec une topologie d'anticipation à boucle unique. Ce modulateur est conçu dans un processus CMOS de 40 nm et atteint une plage dynamique de 80 dB et une bande passante de 100 MHz à une fréquence d'horloge de 2,4 GHz. Le modulateur consomme 69,7 mW à partir d'une alimentation de 1,2 V.

Introduction

Poussés par les demandes croissantes des applications de communication sans fil telles que les normes cellulaires, les convertisseurs analogique-numérique (CAN) évoluent rapidement pour prendre en charge une bande passante de signal (BW) et une plage dynamique (DR) plus élevées. L'exigence de BW dans la norme de communication LTE-A (Long-Term-Evolution Advanced) est passée à 100 MHz. Les ADC Nyquist, généralement les ADC pipeline [1, 2], ont été utilisés dans les macrostations de base pour leur BW élevé. Cependant, les tampons d'entrée indispensables pour piloter des condensateurs d'entrée commutés à bruit thermique limité et un filtre anti-crénelage entraînent une consommation d'énergie et une complexité de conception importantes. De plus, le fait que les CAN en pipeline reposent sur un gain inter-étages précis, qui détermine l'amplificateur résiduel à large bande à gain élevé et la technologie d'étalonnage, entraîne une complexité et une dissipation de puissance. Δ Σ Les CAN sont connus pour leurs hautes performances et leur efficacité énergétique grâce à la technologie de suréchantillonnage et de mise en forme du bruit. Cependant, l'exigence de taux de suréchantillonnage (OSR), qui est généralement supérieure à 16 [3-6], détermine la fréquence d'échantillonnage au-delà du GHz. Récemment, Δ Σ Des CAN dépassant 50 MHz BW ont été proposés en utilisant des processus CMOS à l'échelle nanométrique, qui permettent une fréquence d'horloge multi-GHz. Auparavant, haute fréquence Δ Σ Les ADC adoptent généralement des réalisations en temps continu (CT) [3-9] au lieu de réalisations en temps discret (DT). Ce dernier est mis en œuvre par un circuit à condensateur commuté, et sa précision repose sur l'adaptation des condensateurs, ce qui signifie qu'un fonctionnement robuste en cas de variation de processus est offert. En outre, une immunité supérieure à la gigue d'horloge est fournie puisque les constantes de temps des condensateurs et des commutateurs sont suffisamment petites. Cependant, comme l'opération d'échantillonnage s'exécute avant le modulateur, le filtre anti-crénelage est nécessaire. D'autre part, en raison de l'exigence de stabilisation pour assurer la stabilité des étages, les amplificateurs opérationnels dans les modulateurs DT sont implémentés avec une bande passante à gain unitaire (UGBW) plus large que les modulateurs CT. En résumé, les modulateurs DT peuvent fournir un signal de haute précision mais étroit [10, 11] et sont largement utilisés pour mettre en œuvre des applications de mesure telles que les capteurs intelligents et l'imagerie biomédicale. En revanche, il y a eu plus d'efforts pour concevoir des modulateurs CT pour les applications haute fréquence que ceux DT avec une complexité et une consommation d'énergie comparables.

L'objectif de conception exigeant d'un BW plus élevé dans un processus donné détermine un OSR inférieur en raison de la fréquence d'horloge limitée du processus. Pour obtenir un DR suffisant, une mise en forme agressive du bruit mise en œuvre par ordre de fonction de transfert de bruit élevé, qui est classiquement réalisée par cascade de filtres à boucle et généralement égale ou supérieure à 3 dans les travaux précédents, est requise. Cependant, l'augmentation des ordres de filtrage de boucle entraîne une consommation d'énergie, une instabilité et une complexité de conception. L'architecture de mise en forme du bruit à plusieurs étages (MASH) [6, 8], mise en œuvre par des Δ locaux d'ordre faible en cascade Σ modulateurs sans chemin de rétroaction entre eux, a été utilisé pour atténuer les problèmes de stabilité mais avec une sensibilité aux décalages. De plus, un modulateur avec un quantificateur multi-bits obtient un DR conditionnellement élevé avec une quantité de comparateur croissante exponentielle.

Cet article décrit un modulateur CT en CMOS 40 nm qui atteint 80 DR sur 100 MHz BW avec une consommation de 69,7 mW en utilisant un processus CMOS 40 nm. Ce document est organisé comme suit. La section « Méthode » décrit la topologie du modulateur et la mise en œuvre du circuit. La section « Résultats et discussion » montre des résultats simulés, et la section « Conclusion » fournit un résumé de ce travail.

Méthode

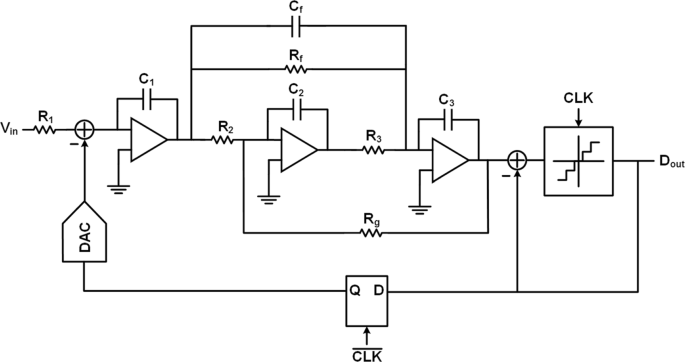

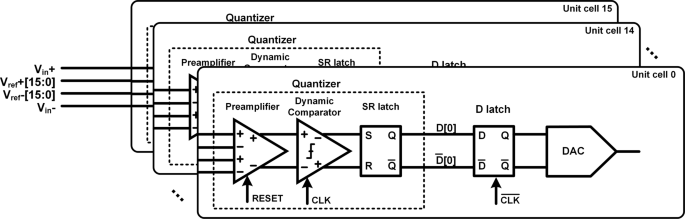

La figure 1 illustre le schéma général du TC proposé de 3e ordre Δ Σ modulateur avec la structure asymétrique pour la simplification. La mise en forme du bruit de 3ème ordre obtient un excellent compromis entre le DR et la stabilité de la boucle. Le modulateur proposé a une fréquence d'échantillonnage de 2,4 GHz avec un 12 OSR. L'OSR relativement élevé en Δ Σ modulateurs dépassé 100 MHz BW assure un DR élevé. Le modulateur contient trois intégrateurs RC, un quantificateur 4 bits et un DAC 4 bits à pilotage de courant. Les intégrateurs sont mis en œuvre par des amplificateurs à action directe innovants à dissipation de faible puissance pour une efficacité énergétique élevée. Le DAC de rétroaction a un délai supplémentaire d'une demi-période d'échantillonnage pour relâcher l'exigence de métastabilité du quantificateur. Un chemin de retour rapide mis en œuvre par un additionneur passif et piloté directement par le quantificateur réalise la compensation du retard de boucle excessive (ELD). Une topologie d'anticipation est utilisée pour l'efficacité énergétique au détriment de la fonction de transfert de signal hors bande.

Schéma général du CT proposé à 4 bits à boucle unique du 3e ordre Δ Σ modulateur avec une topologie feedforward

Conception de l'amplificateur

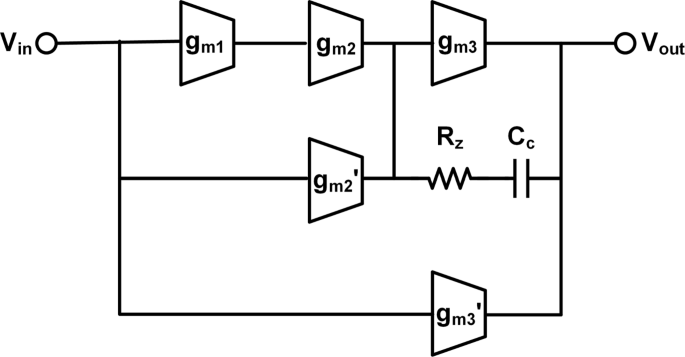

Un gain d'amplificateur élevé est requis dans Δ Σ modulateurs pour assurer la fonction de transformation de bruit souhaitée. Cependant, les technologies nanométriques utilisées pour atteindre une fréquence d'horloge multi-GHz souffrent d'un faible gain intrinsèque. Par conséquent, un amplificateur à trois étages est adopté pour mettre en œuvre un gain CC suffisant, comme le montre la Fig. 2. La topologie d'anticipation et la compensation Miller sont combinées pour améliorer la marge de phase sans réduction de la bande passante du gain unitaire. Les amplificateurs à action directe ont été une solution populaire pour obtenir un gain élevé avec une UGBW et une marge de phase (PM) adéquates. Le zéro du demi-plan gauche causé par le chemin d'anticipation est censé annuler efficacement le déphasage négatif des pôles. Il nécessite une transconductance élevée des amplificateurs sur le chemin d'anticipation et consomme une puissance importante. Le schéma avantageux de réutilisation du courant de polarisation économise de l'énergie alors qu'il limite g m valeurs. g insuffisant m provoque généralement le zéro au-delà de l'UGBW et ne peut pas fournir une marge de phase adéquate. Un zéro optimisé situé en dessous de l'UGBW global est fourni en ajoutant un condensateur de compensation Miller et une résistance d'annulation.

Topologie de l'amplificateur feedforward à trois étages proposé avec compensation Miller

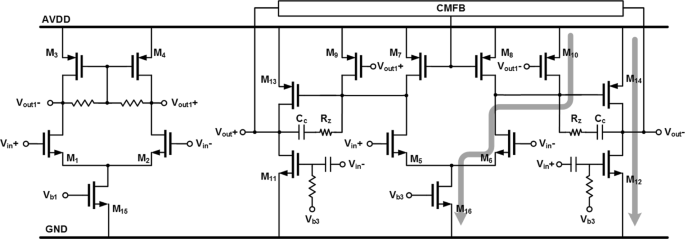

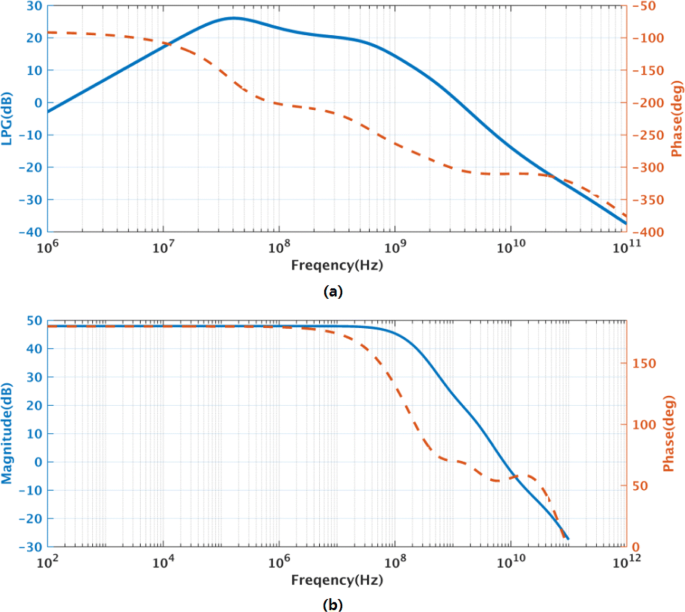

La figure 3 montre le schéma au niveau du transistor de l'amplificateur utilisé dans le premier intégrateur. Transistors M 1−4 forment l'étage d'entrée de l'amplificateur, tandis que les transistors M 9,10 et M 13,14 forment respectivement le deuxième et le troisième étage. Transistors M 5−8 et M 11,12 créer deux chemins d'anticipation à grande vitesse entre l'entrée et la sortie tout en partageant les courants de polarisation avec les amplificateurs des deuxième et troisième étages. Le mode commun de sortie du premier étage (CM) est fixé localement. Le CM de sortie du deuxième étage et du troisième étage est fixé par un chemin de retour de deuxième étage à travers un amplificateur CMFB, M 7,8 et M 13,14 . La figure 4a montre la réponse en boucle ouverte post-implantation simulée de l'amplificateur du premier intégrateur avec toutes les charges tandis que la figure 4b montre la réponse en boucle fermée. Le premier intégrateur atteint 3,6 GHz d'UGBW et 57,8 ∘ de PM avec tous les effets de charge tout en consommant 10,5 mW à partir d'une alimentation de 1,2 V. Les deuxième et troisième intégrateurs adoptent la même topologie mais avec des courants de polarisation mis à l'échelle, atteignant un UGBW de 4,7 et 3,3 GHz et un PM de 58,0 et 57,8 ∘ tout en consommant respectivement 4,3 et 17,3 mW.

Schéma de l'amplificateur niveau transistor

Les résultats simulés post-implantation de l'amplificateur dans le 1er intégrateur. un Réponse ca en boucle ouverte ; b Réponse ca en boucle fermée

Quantificateur et DAC

Comme le schéma du quantificateur et du DAC montré sur la figure 5, chacun se compose de 16 cellules unitaires. Le quantificateur est réalisé sous la forme d'un ADC flash à 4 bits avec un encodeur à 16 niveaux généré à partir d'une échelle résistive à 17 prises. Le quantificateur, dont la durée de fonctionnement est exigée par ELD à moins d'une demi-période d'échantillonnage pour assurer la stabilité de la boucle, est un élément clé en tant que limitation du BW maximum.

Le schéma simplifié des quantificateurs et des DAC

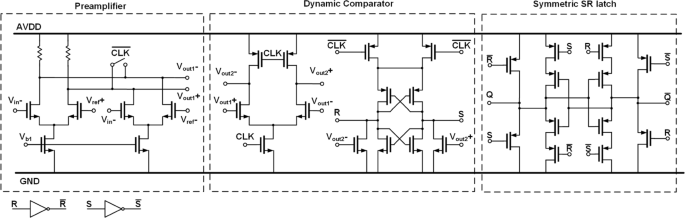

Pour mettre en œuvre des CAN flash à haute vitesse, une architecture de comparateur à trois étages composée d'un étage de préamplificateur, d'un étage de comparateur dynamique et d'un verrou de réglage et de réinitialisation (SR) symétrique [12], illustré par la figure 6, est utilisée. Le préamplificateur pour la réduction du décalage référencé en entrée est constitué de deux paires différentielles à charge résistive avec un commutateur de réinitialisation connecté aux sorties pour permettre une récupération rapide. Contrairement aux comparateurs dynamiques conventionnels, la paire différentielle et les onduleurs à couplage croisé sont divisés en deux parties pour minimiser la quantité de transistor dans chaque trajet de courant pour les alimentations basse tension. Lorsque l'horloge passe au niveau haut, les comparateurs dynamiques commencent à prendre la décision de comparaison dépendante de l'entrée. Ensuite, les deux sorties de chaque comparateur dynamique sont toutes deux remises à 0 lorsque le retour d'horloge passe de haut en bas, déclenchant la régénération et le verrouillage de la bascule SR symétrique. Étant donné qu'un seul transistor dans chaque branche est actif, la structure de verrouillage SR symétrique conduit à une forte capacité de commande de charge. Il permet une petite taille de transistor avec une vitesse de coupure importante et une faible consommation d'énergie. De plus, il en résulte des retards égaux des deux signaux de sortie. Les verrous D avant les unités DAC sont peu sensibles au niveau du signal d'horloge, garantissant une demi-durée ELD. Le circuit au niveau transistor de l'unité DAC de direction actuelle est illustré à la Fig. 7.

Circuit au niveau du transistor d'un élément unitaire du quantificateur proposé

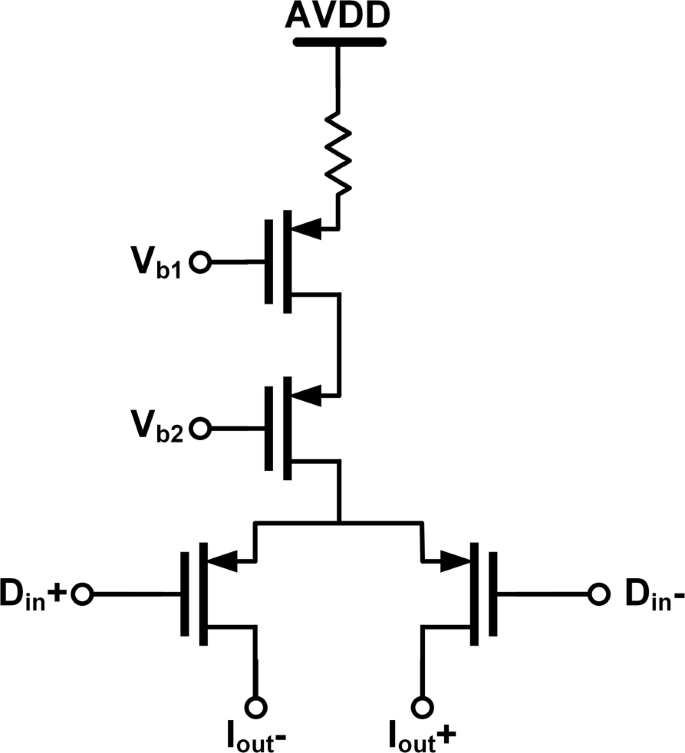

L'élément d'unité DAC de pilotage actuel PMOS

Résultats et discussion

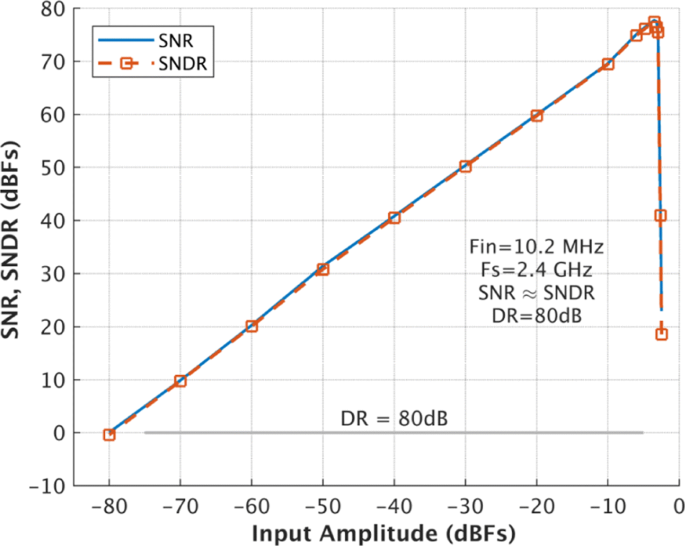

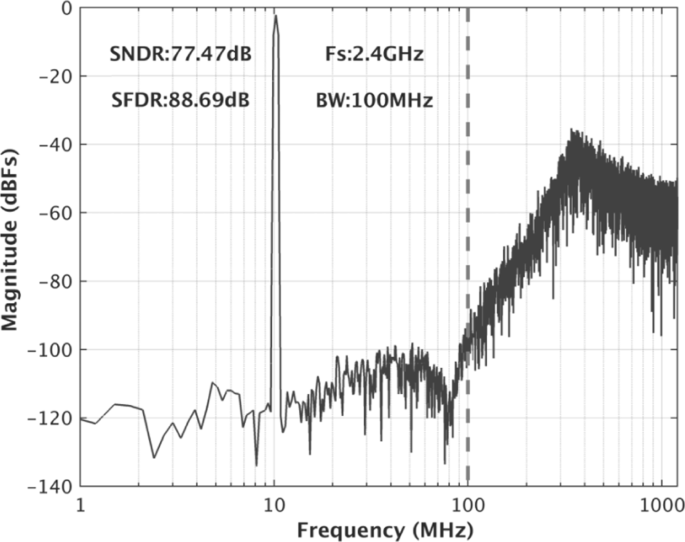

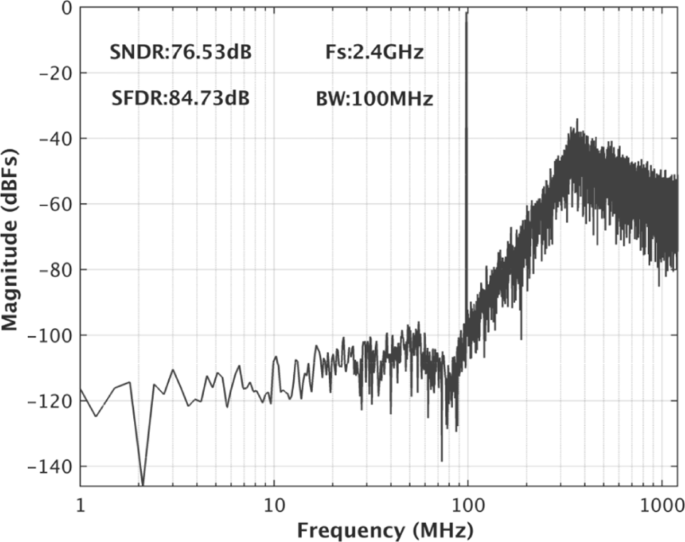

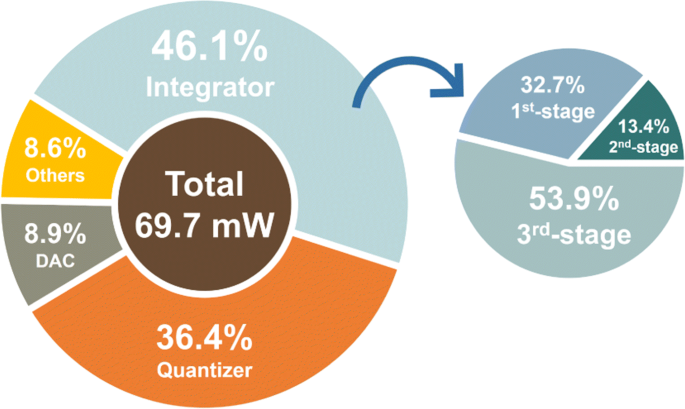

Le prototype Δ Σ modulateur est construit dans un processus CMOS 40 nm. Comme les résultats post-simulés du SNR et du SDNR par rapport à l'amplitude d'entrée à 10,2 MHz illustrés sur la figure 8, un DR de 80 dB est obtenu. Les figures 9 et 10 montrent les spectres simulés avec une entrée monotone de −3,52 dBF à 10,2 MHz et 97 MHz, respectivement, puisque 0 dBF correspond à la pleine échelle du modulateur 2,4 Vpp. Le SNDR est respectivement de 77,47 dB et 76,53 dB. Comme la consommation de panne illustrée sur la figure 11, le modulateur coûte 69,7 mW de consommation d'énergie. L'intégrateur, le quantificateur et le DAC consomment respectivement 32,1 mW, 25,4 mW et 6,2 mW. Une puissance de 6,0 mW est consommée par les autres courants, y compris les tampons d'horloge, les polarisations de courant et les références de tension. Le modulateur atteint un FOM Schreier de 171,6 dB basé sur DR. Le tableau 1 compare ce travail avec plusieurs travaux déjà publiés. Le modulateur proposé atteint un large BW avec le FOM le plus élevé.

SNR et SNDR post-simulés par rapport à l'amplitude du signal d'entrée avec une entrée de 10,2 MHz

Les spectres post-simulés avec une entrée monotone à 10,2 MHz

Les spectres post-simulés avec une entrée monotone à 97 MHz

La répartition de la consommation électrique post-simulée

Conclusion

Dans ce travail, nous avons proposé un CT 4 bits d'ordre 3 Δ Σ modulateur avec une topologie d'anticipation à boucle unique. Ce modulateur est conçu dans un processus CMOS 40 nm et atteint 80 dB DR sur 100 MHz BW à une fréquence d'horloge de 2,4 GHz. La construction de l'amplificateur à dissipation de faible puissance offre une efficacité énergétique élevée et le modulateur consomme 69,7 mw à partir d'une alimentation de 1,2 V et atteint un FOM Schreier de 171,6 dB.

Disponibilité des données et des matériaux

Toutes les données générées ou analysées au cours de cette étude sont incluses dans cet article publié.

Abréviations

- ADC :

-

Convertisseurs analogique-numérique

- BW :

-

Bande passante

- CT :

-

Temps continu

- DR :

-

Plage dynamique

- DT :

-

Temps discret

- ELD :

-

Délai de boucle excessif

- LTE-A :

-

Évolution à long terme avancée

- OSR :

-

Taux de suréchantillonnage

- MP :

-

Marge de phase

- UGBW :

-

Bande passante à gain unitaire

Nanomatériaux

- horloge IV9 Numitron DIY la plus simple avec Arduino

- Impression 3D haute vitesse avec AION500MK3

- Contrôle complet de la polarisation térahertz avec bande passante élargie via des métasurfaces diélectriques

- Fabrication de fosses à l'échelle nanométrique avec un débit élevé sur une couche mince de polymère à l'aide de la lithographie dynamique à base de pointes AFM

- RGO et réseaux tridimensionnels de graphène co-modifiés TIM avec de hautes performances

- Aérogel de graphène/polyaniline avec superélasticité et haute capacité en tant qu'électrode de supercondensateur hautement tolérante à la compression

- Convertisseur de polarisation avec biréfringence contrôlable basé sur une métasurface hybride entièrement diélectrique-graphène

- Cellule solaire hybride en silicium organique-nanostructuré à hautes performances avec structure de surface modifiée

- La réponse photocourante extrêmement améliorée dans les nanofeuillets isolants topologiques à haute conductance