Étude comparative de transistors à effet de champ à capacité négative avec différentes capacités MOS

Résumé

Nous démontrons l'effet de capacité négative (NC) de HfZrOx -à base de transistors à effet de champ (FET) dans les expériences. I amélioré DS , SS et G m de NCFET ont été obtenus par rapport au FET à semi-conducteur à oxyde métallique (MOS) de contrôle. Dans cette expérience, les transistors MIS inférieurs avec des temps de passivation différents sont équivalents aux dispositifs NC avec des capacités MOS différentes. Pendant ce temps, les propriétés électriques du NCFET avec une passivation de 40 min sont supérieures à celles du NCFET avec une passivation de 60 min en raison de la bonne correspondance entre C FE et C MOS . Bien que SS de moins de 60 mV/décade ne soit pas atteint, les caractéristiques de transfert non hystérétiques bénéfiques pour les applications logiques sont obtenues.

Introduction

Avec la réduction d'échelle du transistor, le niveau d'intégration du circuit intégré (IC) ne cesse de croître. Un problème de dissipation de puissance qui l'accompagne est urgent à résoudre. Afin de contourner ce problème, la tension de fonctionnement du transistor doit être réduite [1]. L'oscillation sous le seuil (SS) du MOSFET ne peut pas être inférieure à 60 mV/décade à température ambiante, ce qui restreint la réduction de la tension de seuil V TH et tension d'alimentation V DD [2]. De nombreux efforts ont été consacrés à la recherche et au développement de dispositifs dotés de nouveaux mécanismes de transport et de commutation pour dépasser la limite de Boltzmann, notamment le transistor à effet de champ à capacité négative (NCEFT) [3, 4], le FET à grille résistive [5], le nano- FET électromécanique (NEMFET) [6, 7], ionisation par impact métal-oxyde-semiconducteur (I-MOS) [8, 9] et FET à effet tunnel [10, 11]. Parmi eux, le NCFET a suscité beaucoup d'attention car il peut atteindre un SS raide sans perdre le courant d'entraînement [12,13,14,15]. HfO dopé2 (par exemple, HfZrOx (HZO) et HfSiOx ) a été largement utilisé dans les NCFET [4, 16, 17] ; il est compatible avec le procédé CMOS [18]. Une étude théorique a montré que l'hystérésis indésirable se produit en raison de la capacité ferroélectrique inégalée C FE à la capacité MOS sous-jacente C MOS dans NCFET [19]. Cependant, l'effet de la correspondance entre C FE et C MOS sur les caractéristiques électriques des NCFET est toujours une préoccupation dans les expériences.

Dans ce travail, les caractéristiques électriques des FET NC Ge avec différentes capacités MOS sont étudiées sur la base des différentes correspondances entre C FE et C MOS . Bien que SS inférieur à 60 µmV/décade n'apparaisse pas, les caractéristiques de transfert sans hystérésis et de meilleures propriétés électriques sont obtenues. Pics apparents de C FE contre V FE les courbes démontrent l'effet NC des NCFET à base de HZO. La meilleure correspondance de C FE et C MOS contribue à un SS plus raide et plus élevé sur le courant, ce qui est bénéfique pour les applications logiques.

Méthodes

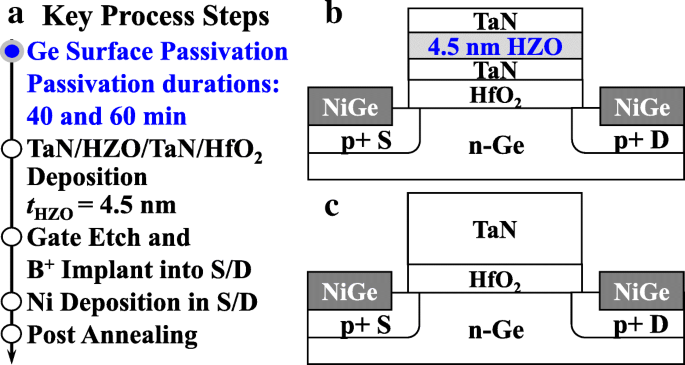

Le processus de fabrication clé des Ge NCFET est illustré à la figure 1a. Des plaquettes n-Ge(001) de quatre pouces avec une résistivité de 0,088-0,14 Ω·cm ont été utilisées comme substrats de départ. Après le nettoyage préalable de la grille, les plaquettes de Ge ont été chargées dans une chambre à ultra-vide pour la passivation de surface à l'aide de Si2 H6 . Deux durées de passivation de 40 et 60 min ont été utilisées. Ensuite, TaN/HZO/TaN/HfO2 pile a été déposée. Les épaisseurs du HfO2 la couche diélectrique et la couche HZO FE sont respectivement de 4,35 et 4,5 nm. Après la structuration de la grille et la gravure, des régions source/drain (S/D) ont été implantées à l'aide d'ions bore (B + ) à une énergie de 30 keV et une dose de 1 × 10 15 cm −2 . Le nickel métallique S/D a été formé à l'aide d'un processus de décollement. Enfin, un recuit thermique rapide à 450 °C pendant 30 µs a été réalisé. Contrôlez le MOSFET avec TaN/HfO2 pile a également été fabriqué. Les figures 1b et c montrent les schémas du NCFET fabriqué et du MOSFET de contrôle, respectivement. La grille métallique interne du NCFET fabriqué contrebalance le potentiel à la surface du canal, appelé structure MFMIS.

un Étapes clés du processus des appareils NC fabriqués. Les schémas du b fabriqué NCFET et c MOSFET de contrôle

Résultats et discussion

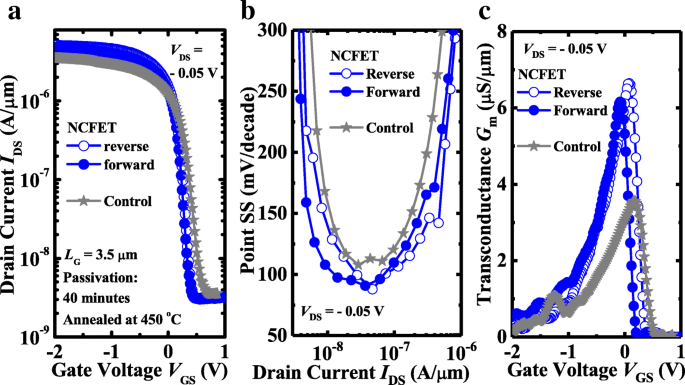

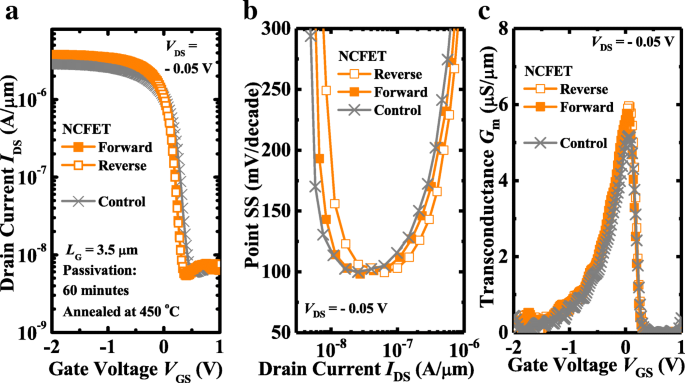

La figure 2a trace le I mesuré DS -V GS courbes d'une paire de NCFET et MOSFET de contrôle avec passivation de surface de 40 min. Les deux appareils ont une longueur de grille L G de 3,5 μm. Le dispositif NC avec passivation de 40 min a un I considérablement amélioré DS que le MOSFET de contrôle. Les courbes de transfert du NCFET présentent une caractéristique non hystérétique. Point SS contre I DS les courbes de la figure 2b montrent que le transistor NC a amélioré la SS par rapport au dispositif de commande, bien que la SS inférieure à 60 µmV/décade n'apparaisse pas. La figure 2c montre que le transistor NC obtient une transconductance linéaire considérablement augmentée G m sur le dispositif de contrôle en V DS de − 0,05 V. La figure 3 compare les performances électriques du NCFET et du MOSFET de contrôle avec passivation de surface pendant 60 min. De même, le I DS , point SS et G m du NCFET sont supérieurs à celui du MOSFET de contrôle.

un Le I mesuré DS -V GS courbes du NCFET et du MOSFET de contrôle avec passivation de 40 min. Comparaison de b point SS contre I DS et c G m caractéristiques entre NC FET et contrôle MOSFET

un Le I mesuré DS -V GS courbes du NCFET et du MOSFET de contrôle avec passivation de 60 min. Comparaison de b point SS contre I DS et c G m caractéristiques entre NCFET et MOSFET de contrôle

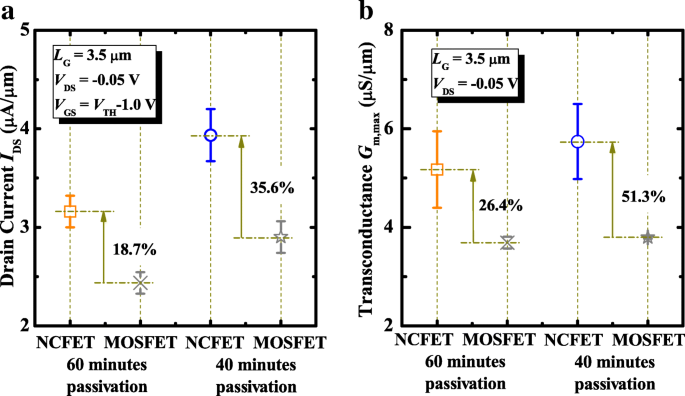

La figure 4a montre les résultats statistiques du courant d'entraînement des NCFET et des MOSFET de contrôle à V DS de − 0.05 V et V GS -V TH =− 1,0 V. Les NCFET démontrent une amélioration de 18,7 % et 35,6 % de I DS pour la passivation de surface 60 min et 40 min, respectivement, en comparaison avec les dispositifs de contrôle. Il est supposé que les NCFET passivés pendant 40 min ont une meilleure correspondance entre C MOS et C FE sur les appareils NC avec 60 min. La figure 4b montre que les NCFET obtiennent une amélioration de 26,4 % et 51,3 % de la transconductance maximale G m,max pour une passivation de surface de 60 min et 40 min, respectivement, en comparaison avec les dispositifs de contrôle. On voit que les MOSFET de contrôle avec passivation de surface pendant 40 min ont un I plus élevé DS et G m,max que les appareils passivés pendant 60 min, ce qui est dû au plus grand C MOS induite par la plus petite épaisseur équivalente d'oxyde (E OT ). La grille métallique interne fournit un plan équipotentiel; le dispositif peut être modélisé de manière équivalente comme un diviseur de tension capacitif. La capacité totale C G est une série de C FE et C MOS . La tension de grille interne est amplifiée en raison de l'effet NC. Le coefficient d'amplification de tension interne β = ∣ C EF / ∣ C EF ∣ − C MOS obtient le maximum lorsque |C MOS | =|C FE | [20, 21]. Atteindre la correspondance optimisée de C FE et C MOS est la condition préalable à l'amélioration du courant.

Les statistiques a Je DS et b G m résultats des NCFET et MOSFET de contrôle avec des durées de passivation de 40 et 60 min

Le V extrait int par rapport à la tension de grille V GS les courbes sont représentées sur la figure 5a. V int du transistor NC peut être extrait en raison de l'hypothèse que I DS -V int la courbe du transistor NC est exactement identique à I DS -V GS courbe du dispositif de commande. Le coefficient d'amplification de tension interne dV int /dV GS est représenté sur la figure 5b. dV int /dV GS> 1 est atteint dans la large plage de balayage de V GS pour le NCFET avec une passivation de surface de 40 min, contribuant à un SS plus raide que le dispositif de contrôle pendant le processus de mesure, ce qui est dû à la commutation de polarisation locale [22]. Il est cohérent avec les résultats susmentionnés de la figure 2b. Pour le NCFET avec passivation 60 min, le coefficient d'amplification de tension interne dV int /dV GS> 1 est atteint dans la plage de V GS <0 V pour le double balayage de V GS , ce qui est en accord avec le SS élevé de la figure 3b.

un V extrait int en fonction de V GS courbes. b Le coefficient d'amplification de tension interne par rapport à V GS courbes

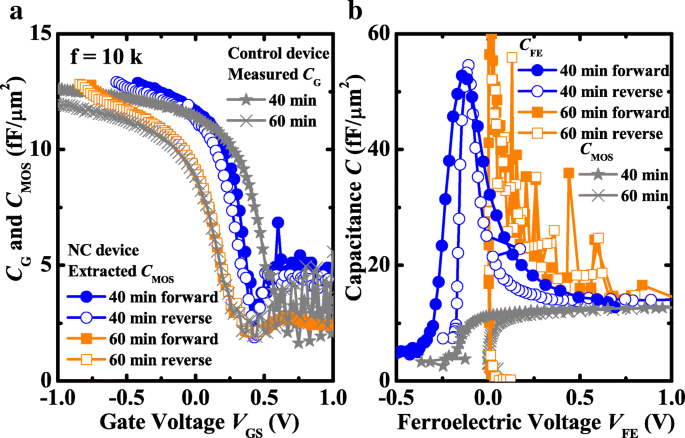

La figure 6a montre le C extrait MOS contre V GS courbes pour le transistor NC, qui s'appuie sur le V int -V GS dans la Fig. 5a et le C G -V GS courbes des MOSFET de contrôle. Le C extrait MOS est en bon accord avec le C mesuré G. Ainsi, la validité de la méthode de calcul est démontrée. Le C FE et C MOS contre V FE les courbes sont représentées sur la figure 6b. Dès le début de l'effet NC, la valeur absolue de C négatif FE du transistor dépasse C MOS pour le double balayage de V GS tout le temps sur la figure 6b. |C FE |> C MOS et C FE <0 peut provoquer des caractéristiques sans hystérésis et la correspondance de C MOS et C FE est bénéfique pour les applications logiques [23, 24]. Caractéristiques sans hystérésis dans les Fig. 2a et 3a sont observés attribués à l'ensemble de l'appariement de domaine et au piégeage de charge inhibé [25]. La commutation de polarisation stable est responsable des caractéristiques non hystérétiques [26]. De plus, le grand gain de grille interne dV int /dV G> 1 est attribué à la légère différence entre |C FE | et C MOS dans la région sous-seuil, ce qui entraîne la forte SS du dispositif NC. Pendant ce temps, il y a une meilleure correspondance entre C FE et C MOS pour le NCFET avec passivation 40 min que le NCFET avec passivation 60 min. Ainsi, cela fournit une preuve directe pour indiquer que le NCFET avec une passivation de 40 min possède une meilleure performance électrique que le NCFET avec une passivation de 60 min. La polarisation FE modifie le V FE; par conséquent, la charge de FE varie. La charge totale se multiplie, ce qui est attribué à la polarisation FE en plus de l'incrément de V GS . En d'autres termes, pour le V donné GS , la charge dans le canal augmente donc le I DS s'améliore. En conséquence, la forte SS de la caractéristique de transfert apparaît dans les expériences.

un Mesuré C G et extrait C MOS en fonction de V GS . b C FE et C MOS contre V FE courbes

Conclusions

Les caractéristiques de transfert sans hystérésis sont obtenues pour les NCFET avec passivation de 40 et 60 min. Les pFET NC Ge avec une passivation de 40 min ont de meilleures caractéristiques électriques que le dispositif NC avec une passivation de 60 min dans les expériences. Nous démontrons également l'effet NC des NCFET à base de HZO. Pour les NCFET, les SS et dV raides int /dV GS> 1 sont obtenus. Le NCFET avec passivation de 40 min a obtenu une bonne correspondance entre C FE et C MOS , ce qui contribue aux caractéristiques non hystérétiques. Les différents comportements NC sont considérés comme liés à la commutation de paroi de domaine microscopique dans les films minces FE.

Disponibilité des données et des matériaux

Les ensembles de données soutenant les conclusions de cet article sont inclus dans l'article.

Abréviations

- B + :

-

Ions de bore

- E OT :

-

Épaisseur d'oxyde équivalente

- FET :

-

Transistors à effet de champ

- HZO :

-

HfZrOx

- IC :

-

Circuit intégré

- I-MOS :

-

Ionisation par impact métal-oxyde-semi-conducteur

- MOS :

-

Semi-conducteur à oxyde métallique

- NC :

-

Capacité négative

- NCFET :

-

Transistor à effet de champ à capacité négative

- NEMFET :

-

FET nano-électromécanique

- S/D :

-

Source/drain

- SS :

-

Balançoire sous le seuil

Nanomatériaux

- Transistors, jonction effet de champ (JFET)

- Transistors, effet de champ à grille isolée (IGFET ou MOSFET)

- Transistors à effet de champ de jonction

- Transistors à effet de champ à grille isolée (MOSFET)

- Introduction aux transistors à effet de champ à jonction (JFET)

- Introduction aux transistors à effet de champ à grille isolée

- MoS2 avec épaisseur contrôlée pour l'évolution électrocatalytique de l'hydrogène

- Transistors multicouches à effet de champ SnSe Nanoflake avec contacts Au Ohmic à faible résistance

- Étude de l'effet de la direction d'impact sur le processus de coupe nanométrique abrasif avec la dynamique moléculaire