PMOSFET Ge à haute mobilité avec diélectrique ZrO2 :impacts du post-recuit

Résumé

Cet article étudie les impacts du recuit post-métal (PMA) et du recuit post-dépôt (PDA) sur les performances électriques des transistors à effet de champ métal-oxyde-semiconducteur de type p (pMOSFET) avec ZrO2 diélectrique. Pour les transistors sans PDA, le courant à l'état passant (I ON ), les caractéristiques d'oscillation sous-seuil (SS) et d'épaisseur équivalente de capacité (CET) sont améliorées avec une augmentation de la température du PMA de 350 à 500 °C. Cristallisation de ZrO2 diélectrique à la température plus élevée du PMA contribue à l'augmentation de la permittivité de ZrO2 et la diminution de la densité des états d'interface (D il ), résultant en un CET réduit et une mobilité effective élevée des trous (μ eff ). Il est démontré que les pMOSFET Ge avec un traitement PDA à 400 °C ont un CET plus faible et une SS plus raide mais un μ plus faible eff par rapport aux appareils sans PDA.

Contexte

Le germanium (Ge) a été considéré comme l'un des matériaux de canal p attrayants pour le CMOS avancé car il offre une mobilité des trous beaucoup plus élevée que le Si [1,2,3]. Un diélectrique de grille de haute qualité et une passivation efficace de la surface Ge sont les clés pour réaliser la mobilité effective supérieure des porteurs (μ eff ) et un courant de commande élevé dans le transistor Ge [4,5,6,7]. Plusieurs matériaux à haut κ tels que HfO2 [8], ZrO2 [7, 9], La2 O3 [10], et Y2 O3 [11] ont été étudiés comme diélectriques de grille alternatifs pour les transistors à effet de champ métal-oxyde-semiconducteur de type p (pMOSFET) pour atteindre une évolutivité d'épaisseur équivalente de capacité (CET) vers moins de 1 nm. Parmi ceux-ci, ZrO2 Le diélectrique a attiré le plus d'attention en raison de la valeur beaucoup plus élevée [12, 13] et de la meilleure qualité interfaciale [14] par rapport à ceux à base de Hf. Il a été largement rapporté que la cristallisation de ZrO2 peut encore améliorer les performances électriques du Ge pMOSFET, par exemple en réduisant le CET et en augmentant le μ eff [15, 16]. Cependant, il y a un manque d'étude sur les impacts des étapes de processus pour le ZrO2 cristallisation sur les performances de l'appareil des transistors Ge.

Dans cet article, nous étudions les impacts du recuit post-métal (PMA) et du recuit post-dépôt (PDA) sur les performances électriques des pMOSFET Ge avec ZrO2 diélectrique. μ considérablement amélioré eff et un CET réduit peut être obtenu dans des appareils à une température PMA plus élevée.

Méthodes

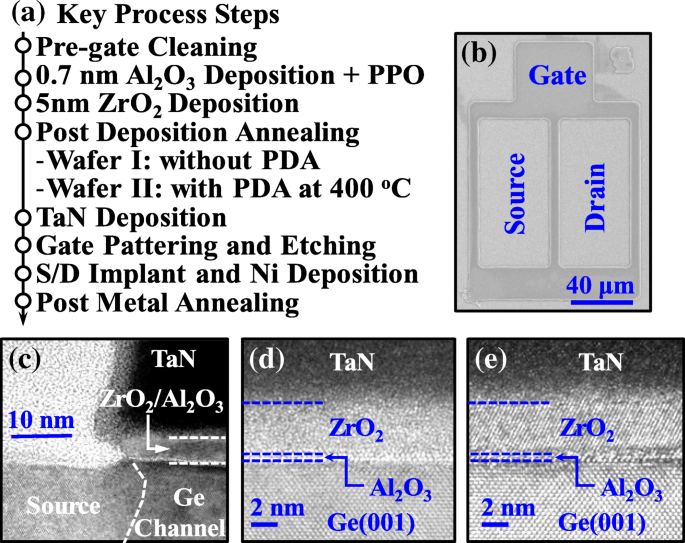

Étapes clés du processus de fabrication des pMOSFET Ge avec ZrO2 diélectrique sont représentés sur la figure 1a. Les pMOSFET Ge ont été fabriqués sur une plaquette Ge(001) de type n avec une résistivité de 0,088-0,14 Ω∙cm. Après plusieurs cycles de nettoyage chimique dans la solution HF diluée (1:50) et rinçage à l'eau déminéralisée. La plaquette de Ge a été chargée dans une chambre de dépôt de couche atomique (ALD). La surface du Ge a été passivée par une post-oxydation à l'ozone (OPO), c'est-à-dire un Al2 ultrafin O3 couche a été déposée à 300°C, puis, l'OPO in situ a été réalisée à 300°C pendant 15 min. Après cela, un ZrO2 de 5 nm d'épaisseur a été déposé à 250 °C dans la même chambre ALD en utilisant TDMAZr et H2 O comme précurseurs de Zr et O, respectivement. Lors du dépôt, Zr[N(CH3 )2 ][sub>4 source a été chauffée à 85 °C. Le processus PDA a été réalisé sur certains échantillons à 400 °C pendant 60 s en utilisant le recuit thermique rapide. Les échantillons avec et sans PDA ont été notés wafer II et I, respectivement. Ensuite, une électrode de grille TaN de 100 nm d'épaisseur a été déposée par pulvérisation cathodique réactive. Après la structuration de la grille et la gravure, les régions source/drain (S/D) ont été formées par BF2 + implantation à une énergie de 30 keV et une dose de 1 × 10 15 cm −2 . Des contacts S/D en nickel de quinze nanomètres ont été formés par un processus de décollement. Enfin, le PMA à 350, 400, 450 et 500 °C pendant 30 s a été réalisé pour l'activation du dopant et la métallisation S/D.

un Étapes clés du processus de fabrication des pMOSFET Ge avec ZrO2 diélectrique. b Image SEM du transistor fabriqué. c Image XTEM de Ge pMOSFET montrant les régions de grille et S/D. d , e Images HRTEM d'empilements de grilles de pMOSFET Ge sur la plaquette I recuites à 400 °C et 500 °C, respectivement

La figure 1b montre l'image au microscope électronique à balayage (MEB) d'un pMOSFET Ge fabriqué. La figure 1c montre l'image au microscope électronique à transmission en coupe (XTEM) de Ge pMOSFET, montrant la région source/drain, la grille métallique et ZrO2 diélectrique. Les figures 1d et e montrent les images TEM haute résolution (HRTEM) des empilements de grilles de pMOSFET Ge avec un PMA à 400 et 500 °C, respectivement, sur la plaquette I. On observe que le ZrO2 diélectrique a été entièrement cristallisé et a subi un PMA à 500°C. L'épaisseur de Al2 O3 couche interfaciale est d'environ 0,7 nm.

Résultats et discussion

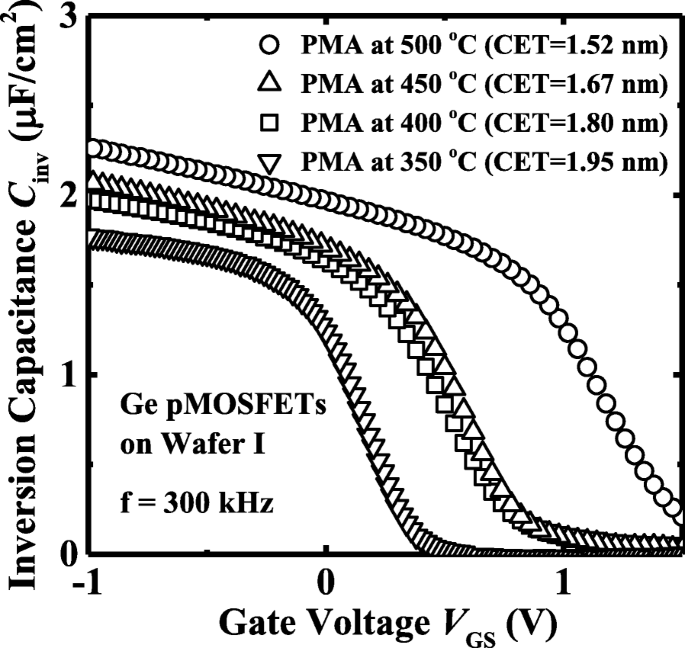

Capacité d'inversion C inv contre V GS les courbes mesurées à une fréquence de 300 kHz pour les dispositifs sur la plaquette I sont présentées sur la Fig. 2. Les valeurs CET sont extraites pour être ∼ 1.95, 1.80, 1.67 et 1.52 nm pour les dispositifs avec PMA à 350, 400, 450, et 500°C, respectivement. Le CET plus petit est obtenu à une température PMA plus élevée en raison de la cristallisation de ZrO2 . En général, les valeurs de pour le ZrO2 amorphe et cristallin sont respectivement d'environ 20-23 et 28-30. Un ZrO2 cristallin de 5 nm d'épaisseur contribue à un EOT de ~ 0.7 nm. Le changement de C-V courbes avec différentes températures de PMA est due au fait que la cristallisation réduit la densité des pièges en vrac en ZrO2 diélectrique.

Inversion C inv -V GS courbes pour les pMOSFET Ge sur wafer I avec un PMA à 350°C, 400 °C, 450°C et 500 °C

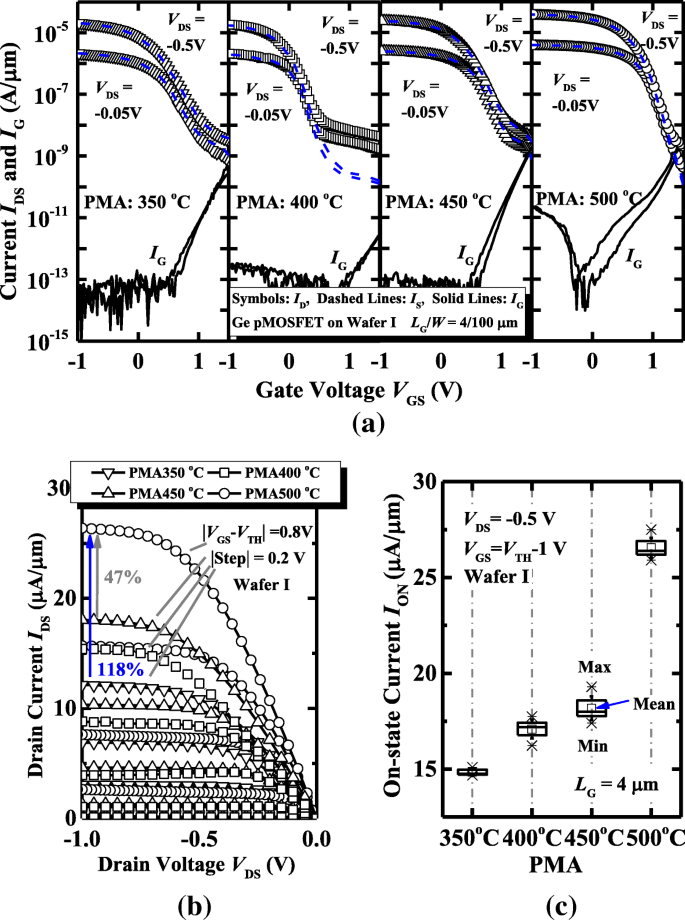

La figure 3a montre les caractéristiques de transfert mesurées et les courants de fuite de grille I G de Ge pMOSFET sur la plaquette I avec les différentes températures de PMA. Tous les appareils ont une longueur de grille L G de 4 μm et une largeur de portail W de 100µm. Les pMOSFET Ge présentent le I beaucoup plus faible G par rapport à I DS pour toutes les températures PMA. Un Je ON /Je OFF rapport supérieur à 10 4 est atteint pour l'appareil avec un PMA à 500°C. Le Je DS -V DS courbes des appareils mesurées aux différents overdrives de grille |V GS -V TH | sont représentés sur la figure 3b. Il est à noter que la tension de seuil V TH est défini comme le V GS à Je DS de 10 -7 A/μm. Le transistor Ge avec un PMA à 500 °C obtient l'amélioration du courant d'entraînement ~ 47% et 118% par rapport aux dispositifs recuits à 450 °C et 350°C, respectivement, à un V DS de − 1.0 V et un |V GS -V TH | de 0,8 V. La figure 3c montre le tracé statistique du I ON à un V DS de − 0,5 V et un V GS -V TH de - 1 V pour les pMOSFET Ge avec les différentes températures du PMA. Tous les transistors de ce tracé ont un L G de 4 μm et un W de 100µm. Les appareils avec un PMA à 500 °C présentent un I amélioré ON par rapport à ceux avec les températures PMA plus basses, ce qui est attribué à la résistance S/D diminuée, au CET réduit et au μ plus élevé eff , qui sera discuté plus tard.

un Mesuré I D , Je S , et Je G vs. V GS courbes des pMOSFET Ge sur la plaquette I avec le PMA à 350, 400, 450 et 500°C. b Je DS -V DS courbes mesurées aux différents V GS -V TH pour les appareils. c L'appareil recuit à 500 °C a un courant à l'état passant I plus élevé ON par rapport aux transistors avec le PMA aux températures plus basses

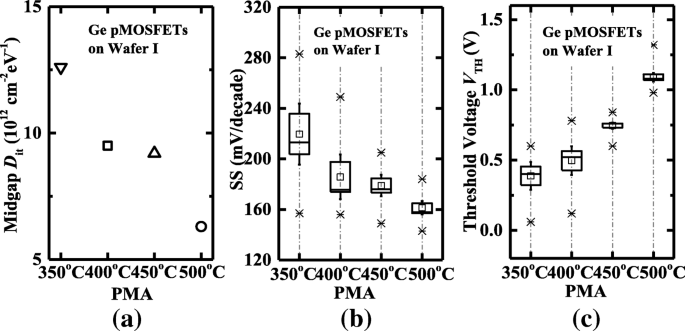

La figure 4 montre les graphiques statistiques de midgap D il , SS et V TH caractéristiques pour les appareils avec les différentes températures PMA. Comme le montre la figure 4a, sur la base de la méthode de conductance maximale [17], le midgap D il les valeurs sont extraites pour être 1,3 × 10 13 , 9,5 × 10 12 , 9.2 × 10 12 , et 6,3 × 10 12 cm −2 eV −1 pour les appareils avec le PMA à 350, 400, 450 et 500 °C, respectivement. La figure 4b montre que les pMOSFET Ge recuits à 500 °C ont des caractéristiques SS améliorées par rapport aux transistors recuits à des températures plus basses, en raison du plus petit midgap D il et CET. Les valeurs de D il et SS des pMOSFET Ge avec PMA sont toujours plus élevés que ceux des transistors Ge les mieux rapportés. Il pourrait éventuellement être réduit en optimisant le module de passivation OPO, par exemple, Al2 O3 l'épaisseur et la température et la durée d'oxydation de l'ozone. V TH passe au V positif GS avec l'augmentation de la température du PMA, qui provient du CET et du D réduits il . Il est conclu que les meilleures performances électriques sont obtenues pour les pMOSFET Ge avec un PMA à 500 °C.

Comparaison de a entrefer D il , b SS, et c V TH pour les pMOSFET Ge sur wafer I avec le PMA à 350, 400, 450 et 500 °C

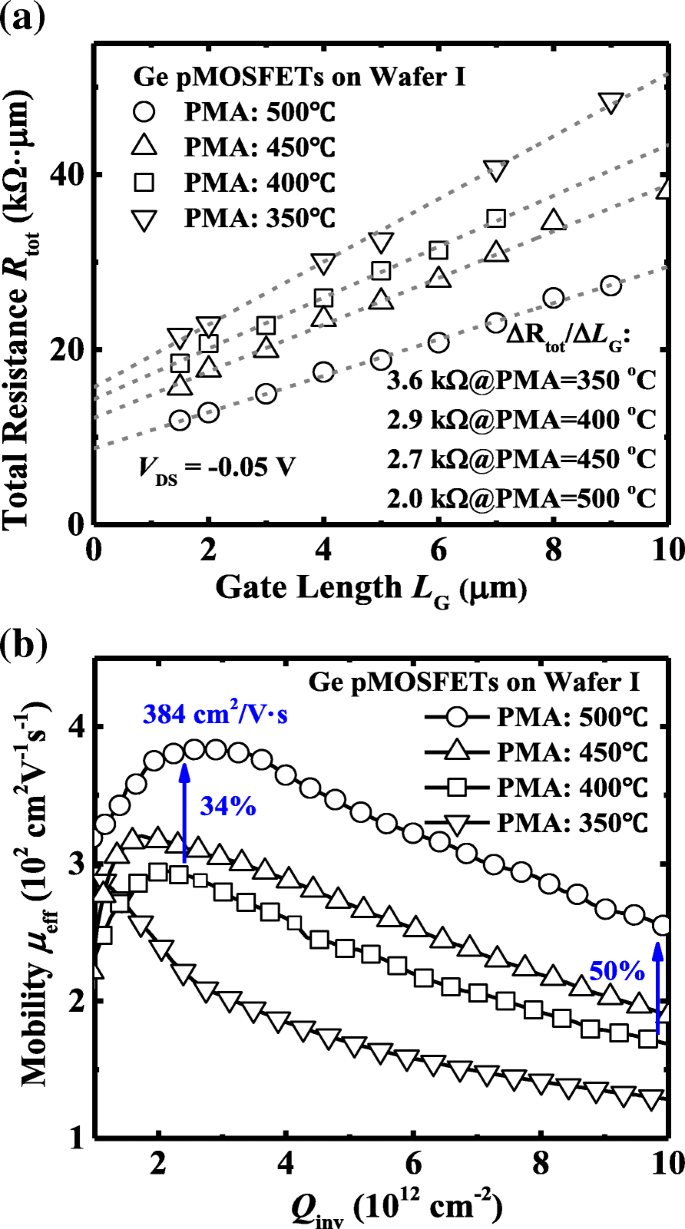

μ eff , en tant que facteur crucial affectant le courant d'entraînement du dispositif et la transconductance dans les pMOSFET Ge, a été mesuré à l'aide du ΔR tot /ΔL G méthode [18]. Un grand nombre d'appareils ont été mesurés avec L G allant de 1,5 à 9 µm. La figure 5a illustre la résistance totale R tot extrait à un |V GS -V TH | de − 1 V et un V DS de − 0.05 V en fonction de L G . Le R SD est la valeur à laquelle la ligne d'ajustement se coupe au y -axe. Le R SD les valeurs ont été estimées à environ 7,85, 7,15, 6,10 et 4,35 kΩ ·μm pour les appareils avec PMA à 350, 400, 450 et 500 °C, respectivement. Cela indique une meilleure activation du dopant du S/D à une température de PMA plus élevée. μ eff peut être extrait par μ eff = 1/[QT inv (ΔR tot /ΔL G )], où Q inv est la densité de charge d'inversion dans le canal Ge et ΔR tot /ΔL G est la pente du R tot contre L G comme le montre la figure 5a. Le plus petit ΔR tot /ΔL G pour les appareils avec PMA à 500 °C indique une amélioration de μ eff par rapport aux transistors avec PMA à 450°C. La figure 5b montre μ eff en fonction de Q inv courbes, extraites à l'aide de la division C -V méthode. La mobilité maximale du trou est de 384 cm 2 /V ·s pour les appareils avec un PMA à 500 °C, soit 31 % de plus que celui des appareils avec un PMA à 400 °C. À un Q élevé inv de 1 × 10 13 cm −2 , Les pMOSFET Ge qui ont subi un PMA à 500°C obtiennent une amélioration de la mobilité par rapport aux dispositifs recuits à 400°C. Transistors Ge avec ZrO2 cristallin ont la plus faible densité de charge de piège en vrac, ce qui entraîne une plus faible diffusion coulombienne à distance des trous, par rapport aux dispositifs avec ZrO2 amorphe . En raison de l'interface lisse entre le ZrO2 cristallin et Ge, les dispositifs Ge recuits à 500 °C ont une diffusion de rugosité de surface inférieure et montrent un déplacement de la mobilité maximale vers le Q plus élevé inv .

un R tot en fonction de L G à un V GS -V TH de − 1 V et un V DS de − 0,05 V pour les appareils sur plaquette I avec différentes températures de PMA. b μ eff vs. Q inv extrait par la scission C -V méthode. La mobilité la plus élevée est obtenue dans les appareils avec un PMA à 500 °C

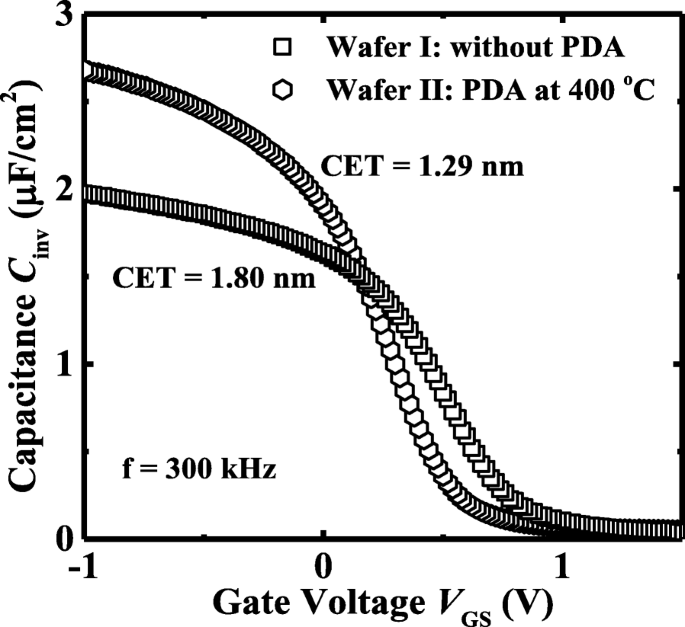

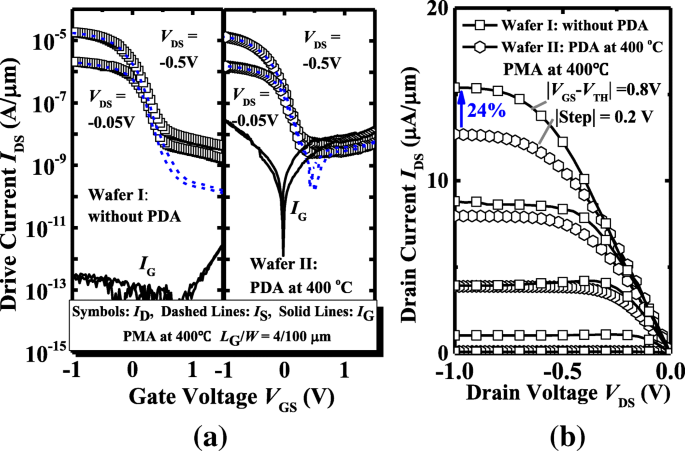

Ensuite, nous discutons des impacts du PDA sur les caractéristiques électriques des pMOSFET Ge. La figure 6 montre le C mesuré inv contre V GS des pMOSFET Ge sur wafer I et wafer II avec un PMA à 400°C. L'appareil qui a subi un PDA à 400 °C a une valeur CET beaucoup plus faible de 1,29 nm par rapport à l'appareil sans PDA, 1,80 nm. La figure 7a montre le I D , Je S , et Je G -V GS courbes caractéristiques des pMOSFET Ge sur wafer I et wafer II, et les dispositifs ayant subi un PMA à 400°C. Un courant de fuite de grille plus important est obtenu pour le dispositif avec PDA par rapport au transistor sans PDA, ce qui est dû au CET plus faible. Le I correspondant DS -V DS courbes des dispositifs mesurées à différentes surcharges de grille V GS -V TH sont représentés sur la figure 7b. Le transistor Ge sans PDA montre une amélioration de ~ 24% du courant de commande par rapport à celui avec PDA à 400 °C avec la même surcharge de − 0.8 V dans la région de saturation.

C inv -V GS tracés pour les appareils sur wafer I et II avec un PMA à 400 °C

un Je D , Je S , et Je G vs. V GS courbes de Ge pMOSFET sur wafer I et II avec PMA à 400°C. b Je DS -V DS courbes mesurées à différents V GS -V TH pour les appareils

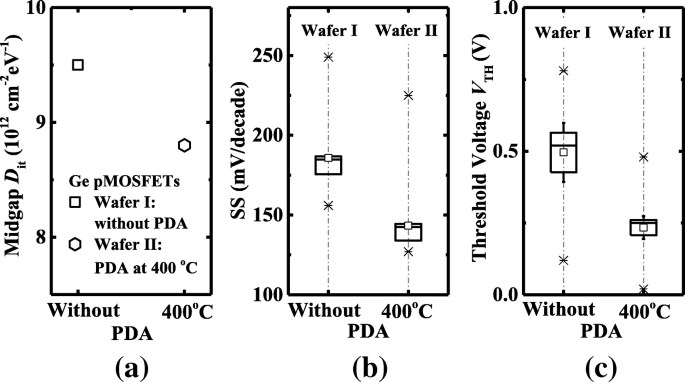

La figure 8 trace les résultats statistiques de midgap D il , SS et V TH des pMOSFET Ge avec et sans PDA. La figure 8a montre que le plus petit D il est réalisé dans des pMOSFET Ge avec PDA à 400 °C par rapport aux dispositifs sans PDA. Sur la figure 8b, la valeur inférieure de l'oscillation moyenne sous le seuil de 142 mV/décade est atteinte pour les appareils avec PDA à 400 °C, correspondant au CET inférieur et au D inférieur il . Il indique que les appareils avec PDA à 400 °C ont un ZrO2 supérieur /Ge interface. La figure 8c montre que les appareils avec et sans PDA ont un V différent TH; cela peut être attribué à la densité de pièges dans la bande interdite inférieure à moitié dominante dans le V TH .

Comparaison de a entrefer D il , b SS, et c V TH pour Ge pMOSFET sur wafer I et II avec PMA à 400 °C

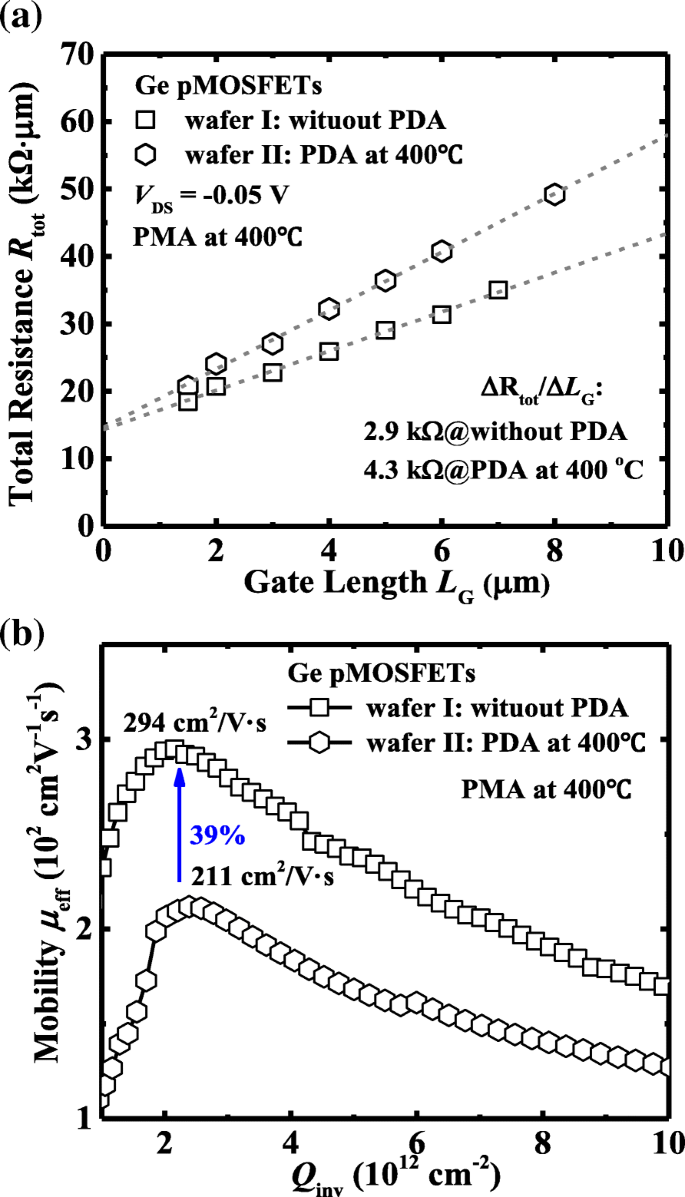

La figure 9a montre le R tot contre L G courbes à une surmultiplication de grille de − 1 V et V DS de − 0,05 V pour les appareils avec un PMA à 400 °C. Le R SD les valeurs sont estimées à environ 7,15 et 7,30 kΩ·μm pour les appareils sans et avec PDA à 400 °C, respectivement. Comme le montre la figure 9b, un pic plus élevé remarquable μ eff est atteint pour les pMOSFET Ge sans PDA, correspondant au plus petit ΔR tot /ΔL G dans la Fig. 9a, par rapport aux appareils avec PDA. Les appareils avec un PDA à 400 °C présentent un pic μ eff de 211 cm 2 /Vs; la mobilité du trou inférieur pourrait être principalement attribuée à la forte diffusion coulombienne à distance contribuée par la charge fixe dans ZrO2 diélectrique.

un R tot contre L G courbes pour appareils sur wafer I et wafer II avec PMA à 400°C. b Mobilité du trou μ eff contre Q inv pour appareils avec et sans PDA

Conclusions

En résumé, les impacts de PMA et PDA sur Ge pMOSFET avec ZrO2 diélectrique ont été largement étudiés. Cristallisation de ZrO2 Le diélectrique de grille permet une mobilité des trous considérablement améliorée et un CET réduit par rapport aux dispositifs à la température PMA inférieure. Une mobilité maximale des trous de 384 cm 2 /V·s et un courant d'entraînement amélioré ont été obtenus dans des appareils avec PMA à 500 °C. Les appareils avec PDA à 400 °C présentaient le CET inférieur et le D plus petit il mais la faible mobilité des trous et le courant de fuite plus important par rapport aux transistors sans PDA.

Disponibilité des données et des matériaux

Les ensembles de données soutenant les conclusions de cet article sont inclus dans l'article.

Abréviations

- ALD :

-

Dépôt de couche atomique

- BF2 + :

-

Ion fluorure de bore

- HEC :

-

Epaisseur effective capacitive

- Voir :

-

Germanium

- HF :

-

Acide fluorhydrique

- HRTEM :

-

Microscope électronique à transmission haute résolution

- IL :

-

Couche interfaciale

- MOSFET :

-

Transistors à effet de champ métal-oxyde-semiconducteur

- Non :

-

Nickel

- PDA :

-

Recuit post-dépôt

- PMA :

-

Post recuit métal

- SS :

-

Balançoire sous le seuil

- TaN :

-

Nitrure de tantale

- TDMAZr :

-

Tetrakis (diméthylamido) hafnium

- ZrO2 :

-

Dioxyde de zirconium

- μ eff :

-

Mobilité efficace des transporteurs

Nanomatériaux

- KUHMUTE repense la mobilité avec l'impression 3D SLS

- Impression 3D haute vitesse avec AFPM

- Impression 3D haute vitesse avec AION500MK3

- Contrôle complet de la polarisation térahertz avec bande passante élargie via des métasurfaces diélectriques

- Mémoire résistive ZrO2/ZrO2 − x /ZrO2 sans conformité avec comportement de commutation multi-états interfacial contrôlable

- Convertisseur de polarisation avec biréfringence contrôlable basé sur une métasurface hybride entièrement diélectrique-graphène

- Cellule solaire hybride en silicium organique-nanostructuré à hautes performances avec structure de surface modifiée

- Amélioration diélectrique des condensateurs MIM Al2O3/ZrO2/Al2O3 déposés par couche atomique par recuit par micro-ondes

- Une référence de tension sans résistance à faible puissance à l'échelle nanométrique avec un PSRR élevé