FET ferroélectriques à nanocristaux intégrés (NEI) pour dispositifs à capacité négative et applications de mémoire non volatile

Résumé

Nous rapportons un nouveau transistor à effet de champ ferroélectrique (FeFET) nanocristal-incorporé-isolant (NEI) avec une couche isolante unifiée ferroélectrique/diélectrique (FE/DE) très mince, ce qui est prometteur pour la logique basse tension et la mémoire non volatile ( NVM). La nature ferroélectrique des couches NEI comprenant du ZrO2 orthorhombique nanocristaux noyés dans Al2 amorphe O3 est prouvée par des mesures de tension de polarisation, une microscopie de force de réponse piézoélectrique et des mesures électriques. Les performances dépendantes de la température et le comportement d'endurance d'un FET à capacité négative NEI (NCFET) sont étudiés. Un FeFET avec un FE/DE de 3,6 nm d'épaisseur atteint une fenêtre de mémoire supérieure à 1 V, ouvrant la voie à une mise à l'échelle ultime de l'épaisseur du FE pour permettre des FeFET tridimensionnels avec un très petit pas d'ailette.

Contexte

Les transistors à effet de champ avec une couche d'isolant de grille ferroélectrique (FeFET) ont suscité un intérêt considérable pour une variété d'applications de circuits intégrés. En raison de ses propriétés inhérentes de capacité négative (NC), un FeFET peut obtenir un comportement de commutation plus raide qu'un MOSFET conventionnel, permettant un fonctionnement à plus basse tension [1]. Diverses structures de canaux [2,3,4] et matériaux [5,6,7] ont obtenu une oscillation sous-seuil (SS) inférieure à 60 mV/décennie. Aussi, l'hystérésis dans le courant-tension (I -V ) caractéristique due à la polarisation résiduelle (P r ) peut être utilisé pour une application de mémoire non volatile (NVM) [8]. Le développement de matériaux pour les FeFET s'est récemment concentré sur le HfO2 dopé polycristallin en raison de sa meilleure évolutivité en épaisseur [9] et de sa compatibilité avec les processus CMOS [2]. Cependant, il existe toujours une limite fondamentale pour HfO2 mise à l'échelle de l'épaisseur pour éviter un courant de fuite de grille indésirable ; ceci à son tour limite le FinFET [2]. Inspiré du concept de nanocristal MOS et de dispositif de mémoire [10, 11], une couche diélectrique isolante (DE) avec des nanocristaux ferroélectriques (FE) intégrés est introduite dans ce travail. La nouvelle conception de dispositif résultante illustrée sur la figure 1 est appelée FeFET « Nanocrystal-Embedded-Insulator » (NEI). Le principal avantage de cette conception est une couche FE/DE unifiée plus fine qui répond à l'exigence de faible fuite de grille.

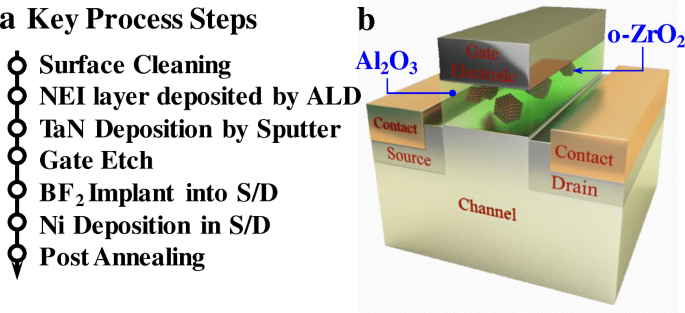

un Étapes clés du processus de fabrication des transistors ferroélectriques à effet de champ NEI. b Schéma 3D du NEI FeFET fabriqué

Dans ce travail, les NEI FeFET sont rapportés. Les propriétés physiques et la ferroélectricité des couches NEI avec différentes épaisseurs physiques sont caractérisées. Les performances électriques des FeFET NEI sont étudiées pour la logique basse tension et les applications NVM.

Méthodes

Les étapes clés du processus de fabrication des FeFET NEI sont illustrées à la figure 1a. Des plaquettes Ge(001) de type n de quatre pouces avec une résistivité de 0,088 à 0,14 cm ont été utilisées comme substrats de départ. Après nettoyage de la pré-grille à l'aide de HF dilué, des plaquettes de Ge(001) ont été chargées dans une chambre de dépôt de couche atomique (ALD) pour le dépôt de la couche NEI comprenant ZrO2 nanocristaux noyés dans Al2 amorphe O3 matrice. Des couches NEI de différentes épaisseurs ont été utilisées dans ce travail. La grille métallique TaN a été déposée sur les FeFET NEI en utilisant la pulvérisation cathodique réactive. Après la structuration et la gravure de la grille, BF2 + des ions ont été implantés dans les régions source/drain à une énergie de 20 keV et une dose de 1 × 15 cm −2 . Trente nanomètres de nickel (Ni) ont été déposés dans les régions source/drain à l'aide du procédé lift-off. Enfin, la fabrication du dispositif a été complétée par un recuit thermique rapide (RTA). Commandez des transistors à effet de champ à semi-conducteurs et à oxyde métallique (MOSFET) avec un Al2 purement diélectrique O3 une couche d'isolation de grille a également été fabriquée.

La figure 1b montre le schéma 3D du NEI FeFET fabriqué, qui comprend des nanocristaux FE intégrés dans une couche isolante de grille DE amorphe. Bien que le volume de matériau FE soit petit, il est suffisant pour les applications NCFET et NVM. Le matériau DE isolant est essentiel pour obtenir une faible fuite de grille et une faible tension de fonctionnement ; il doit avoir à la fois une large bande interdite et une permittivité diélectrique élevée (κ ). Il devrait également prévoir un champ coercitif élevé (E c ) des nanocristaux FE intégrés.

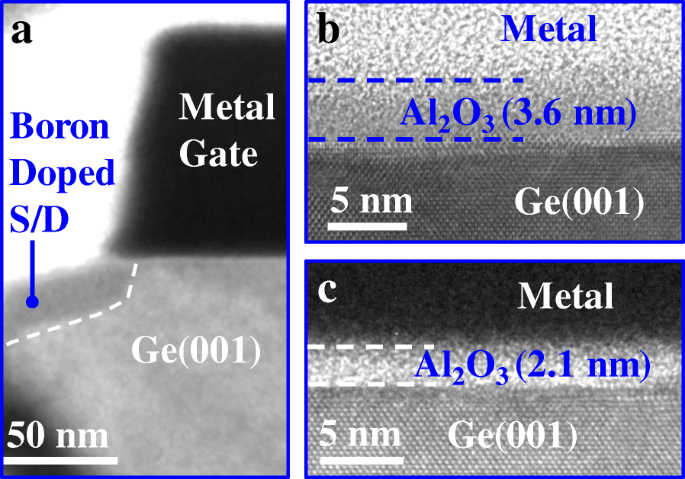

L'image au microscope électronique à transmission en coupe (XTEM) de la figure 2a montre les régions de bord de source/drain, de canal et de grille d'un FeFET fabriqué. Les figures 2b et c indiquent que les épaisseurs des couches NEI étudiées dans ce travail sont respectivement de 3,6 et 2,1 nm. A noter qu'une couche interfaciale de GeOx existe entre la couche NEI et Ge, bien qu'il ne soit pas visible.

un Image XTEM montrant les régions de grille, de canal et de source/drain de NEI-FeFET. b et c Images XTEM de la pile de grilles de FeFET avec des couches NEI de 3,6 et 2,1 nm d'épaisseur, respectivement

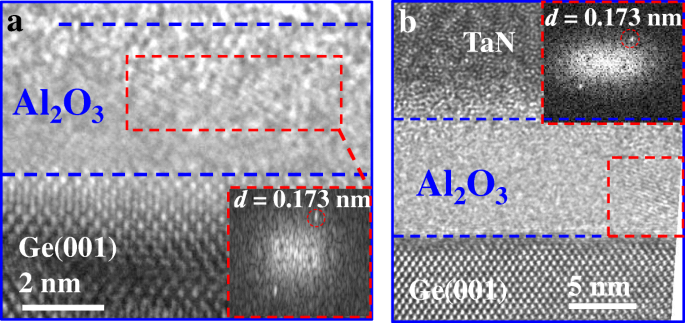

Les images TEM haute résolution (HRTEM) de la figure 3 montrent le ZrO2 nanocristaux noyés dans Al2 amorphe O3 sur Ge(001) dans les échantillons NEI avec des épaisseurs de 3,6 et 6 nm. Dans nos travaux précédents, nous avons montré que le pourcentage atomique de Zr dans la couche NEI est inférieur à 0,5% [12]. Sur la base des diagrammes de diffraction, l'espacement interplanaire d dans les nanocristaux est calculé à 0,173 nm, ce qui correspond à (111) orthorhombique orienté ZrO2 phase [13].

Images HRTEM montrant des nanocristaux noyés dans de l'Al2 amorphe O3 pour les échantillons d'épaisseurs a 3,6 nm et b 6 nm. Les encarts montrent que l'espacement interplanaire d dans le nanocristal est de 0,173 nm, correspondant à o-ZrO2 (111) phase

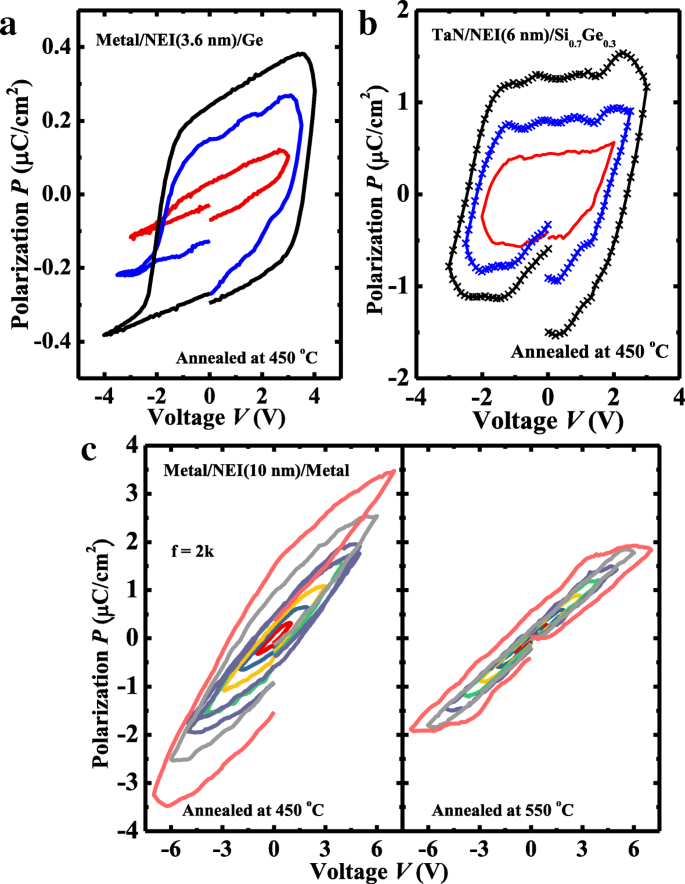

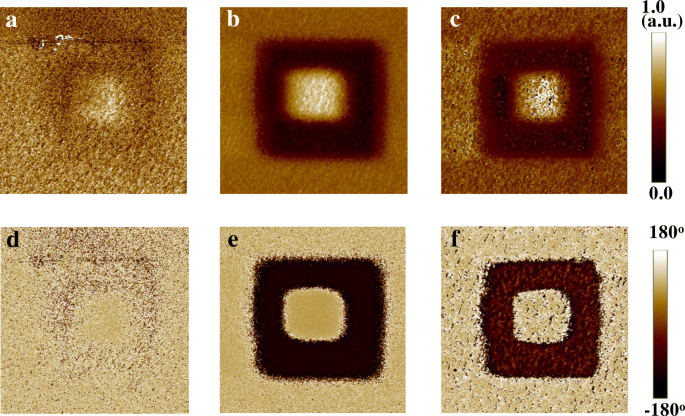

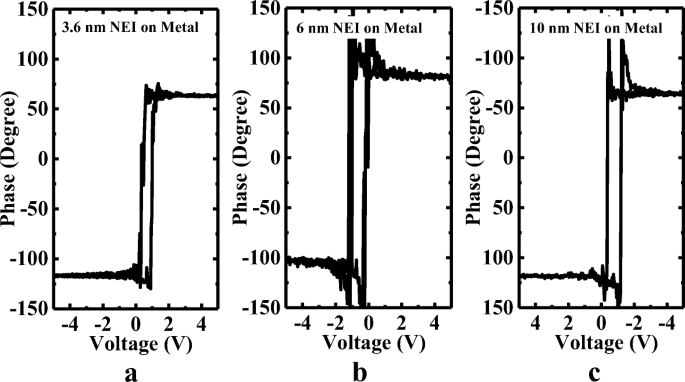

Polarisation par rapport à la tension (P -V ) et des mesures de microscopie de force à réponse piézoélectrique (PFM) ont été effectuées sur les échantillons NEI avec les différentes épaisseurs. Pour caractériser la ferroélectricité de la couche NEI, P -V courbes de TaN/NEI (3,6 nm)/Ge, TaN/NEI (6 nm)/Si0,7 Ge0.3 , et les condensateurs TaN/NEI (10 nm)/TaN sont représentés sur les figures 4a, b et c, respectivement. La couche NEI présente un P inférieur que les valeurs rapportées de HfZrO2 (HZO) [14], ce qui est dû au fait que le rapport volumique de ZrO2 nanocristal dans Al2 O3 matrice est assez faible. On voit que la polarisation résiduelle P r du film NEI augmente avec l'augmentation de l'épaisseur du film. P-V les courbes de la figure 4c indiquent que la ferroélectricité de la couche NEI dégénère tandis que la température de recuit augmente de 450 à 550 °C. Il est à noter que la raison de la non-fermeture du P-V boucles, c'est parce qu'une fuite existe bel et bien. Il a été rapporté que le décalage résultant à un champ électrique nul diminue à mesure que la plage de balayage de tension est réduite [3, 15, 16]. Les images d'amplitude (supérieure) et de phase (inférieure) de 3,6 nm, 6 nm et 10 nm NEI ont été mesurées, comme le montrent les figures 5a, b et c, respectivement. Comme le montre la figure 6, les motifs indiquant la polarité opposée écrits sur la surface de NEI sur TaN présentent le contraste le plus net avec l'augmentation de l'épaisseur du film.

un –c P mesuré -V courbes de TaN/NEI (3,6 nm)/Ge, TaN/NEI (6 nm)/Si0,7 Ge0.3 , et TaN/NEI (10 nm)/TaN, respectivement

un –c Images d'amplitude (supérieure) et de phase (inférieure) de la mesure PFM pour 3,6, 6 et 10 nm NEI sur TaN, respectivement

un –c Caractéristiques de changement de phase de 3,6, 6 et 10 nm NEI sur TaN, respectivement. On observe que la polarité opposée peut être écrite sur la surface de la couche NEI

Résultats et discussion

NEI NCFET

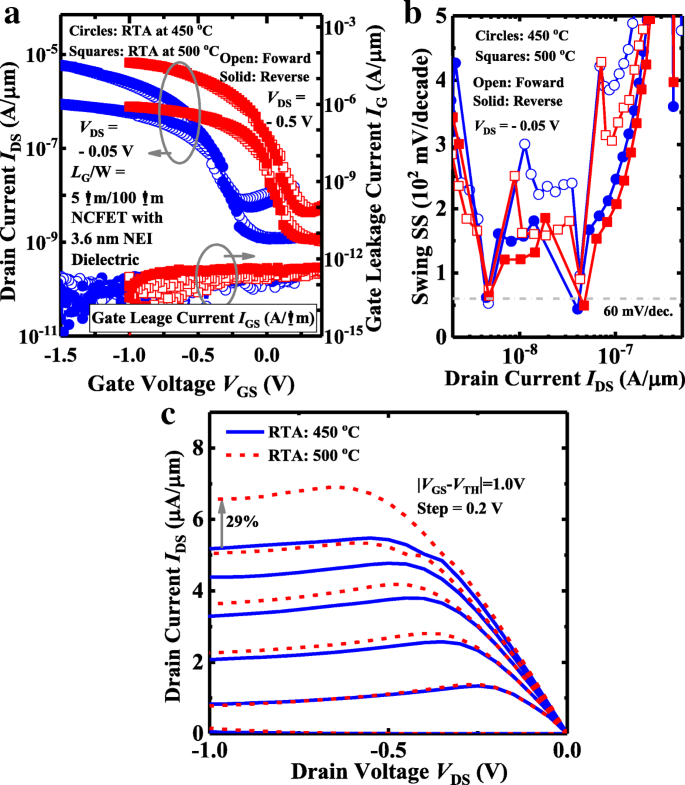

La figure 7a montre le I mesuré DS -V GS courbes des NEI NCFET d'une épaisseur NEI de 3,6 nm recuits à 450 °C et 500 °C. Les NCFET présentent peu d'hystérésis indiquant la bonne correspondance entre la capacité ferroélectrique et la capacité MOS dans les transistors. Les NCFET montrent l'effet NC induit dans le sens horaire I-V boucles, ce qui contraste avec les boucles dans le sens inverse des aiguilles d'une montre par piégeage/dépiégeage de charge [17]. La fuite de la porte I G en fonction de V GS de la même paire d'appareils démontre que la formation de nanocristaux dans Al2 O3 n'augmente pas la fuite de grille. La figure 7b montre que les NCFET atteignent les points SS abrupts inférieurs à 60 mV/décennie pour les balayages aller et retour. Les fluctuations SS dans le NEI NCFET, également observées dans les FinFET NC [2, 18], pourraient être dues à la commutation de polarisation par les différents nanocristaux ou domaines ferroélectriques. Le I mesuré DS -V DS les courbes pour la même paire de dispositifs sur la figure 7c montrent qu'à ∣V GS − V TH ∣ = ∣ V DS ∣ = 1,0 V, le NCFET avec RTA à 500 °C atteint 29% plus grand I DS par rapport au transistor recuit à 450 °C. Ceci est attribué au fait que la mobilité des porteurs dans les caractéristiques de résistance de canal et de contact peut être améliorée avec l'augmentation de la température de recuit [19]. La caractéristique typique induite par la couche ferroélectrique, la résistance différentielle négative (NDR), est observée dans le I DS -V DS courbes pour les NCFET recuits aux différentes températures.

un Mesuré I DS -V GS et Je G -V GS courbes de NCFET avec NEI de 3,6 nm recuits à 450 °C et 500 °C. b NEI NCFET a les points inférieurs à 60 mV/décade pour un V DS valeur de − 0,05 V. c Je DS -V DS courbes pour les NEI NCFET montrant les phénomènes évidents de NDR. Le transistor NC recuit à 500 °C atteint un I de 29 % DS amélioration par rapport à l'appareil avec RTA à 450 °C à une tension d'alimentation de 1,0 V

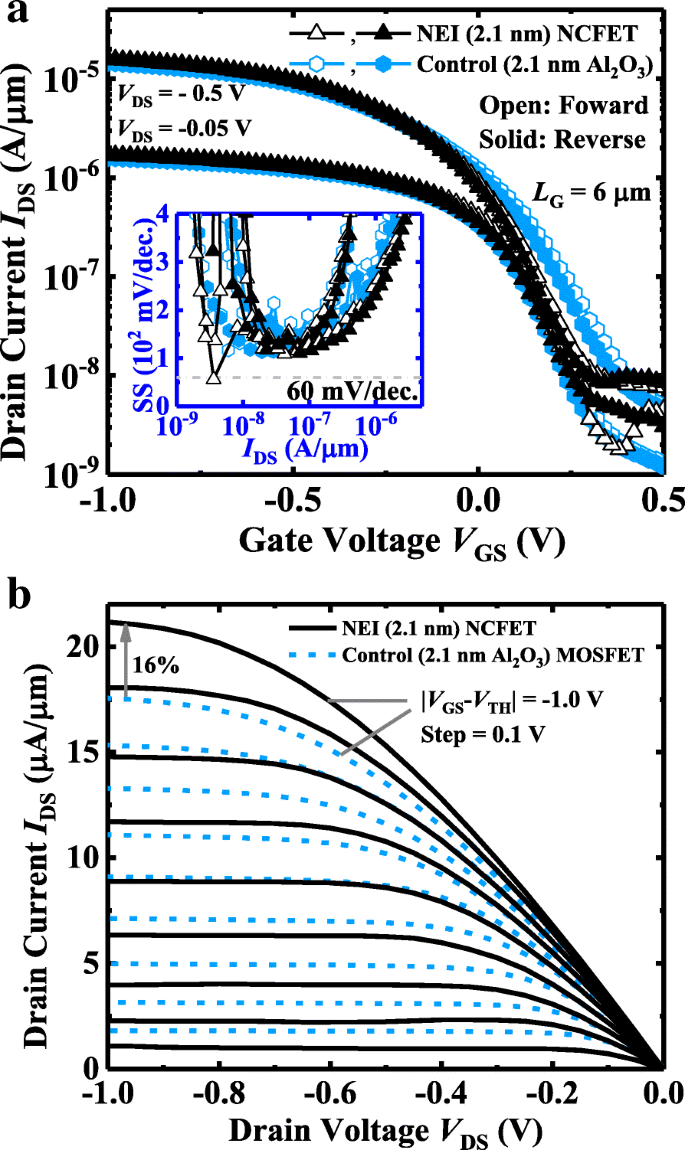

La figure 8a montre le I mesuré DS -V GS courbes d'un NEI NCFET et d'un MOSFET de contrôle avec la même épaisseur d'isolant de 2,1 nm. Les appareils ont un L G de 6 µm. Le NCFET présente les caractéristiques sans hystérésis. L'encart montre le point SS vs. I DS courbes pour les dispositifs, démontrant qu'une amélioration de la SS est obtenue dans le NCFET par rapport au dispositif de contrôle, jusqu'à la tension de seuil. La figure 8b montre le I DS -V DS courbes du NEI NCFET et du MOSFET de contrôle. NCFET présente le phénomène NDR pour le faible V GS . L'effet NDR correspond aux caractéristiques améliorées d'abaissement de la barrière induite par le drain (DIBL) dans le NCFET par rapport au MOSFET de contrôle, comme le montre la figure 8a. À ∣V GS − V TH ∣ = ∣ V DS ∣ = 1.0 V, un 16% I DS l'amélioration est obtenue en NCFET par rapport au dispositif de contrôle. Le NCFET avec un NEI de 2,1 nm a le NDR le moins important par rapport au transistor avec un NEI de 3,6 nm, ce qui est cohérent avec la conclusion de [20].

un Je DS -V GS courbes d'un NEI NCFET et MOSFET de contrôle avec Al2 pur O3 diélectrique. Les deux appareils ont l'isolateur de grille de 2,1 nm. L'encart montre que le NCFET a une SS plus raide que le dispositif de commande jusqu'à la tension de seuil. b Mesuré I DS -V DS courbes pour NCFET et MOSFET de contrôle. NDR est observé pour NCFET à très faible V GS . À ∣V GS − V TH ∣ = ∣ V DS ∣ = 1,0 V, le NCFET atteint un I de 16 % DS amélioration par rapport au dispositif de contrôle

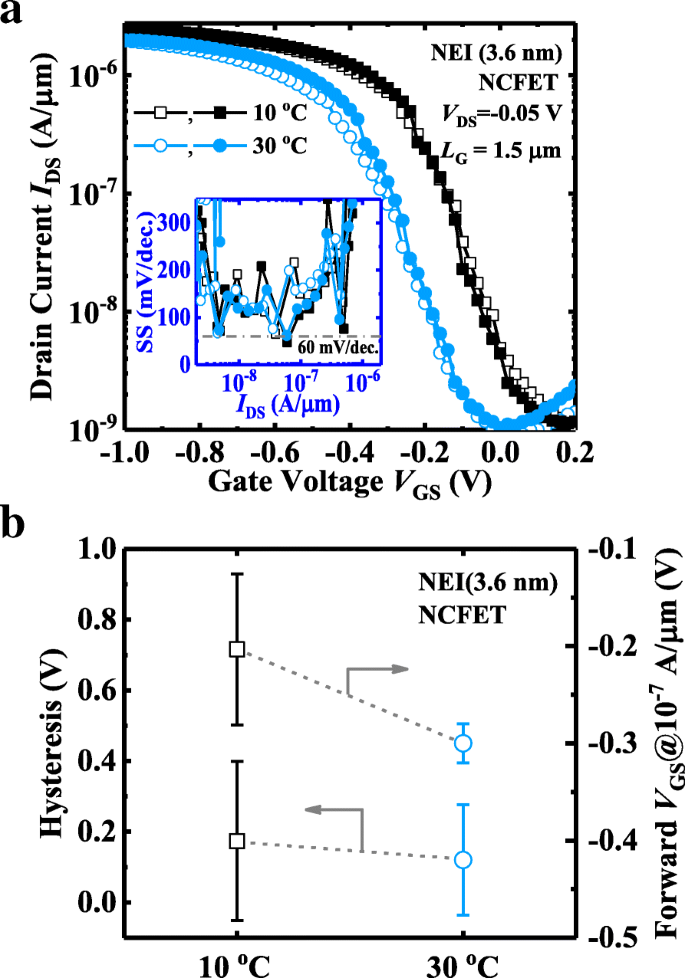

La dépendance à la température du NCFET avec un NEI de 3,6 nm d'épaisseur est étudiée ici. La figure 9a montre I DS -V GS courbes mesurées à 10 °C et 30 °C. L'encart indique que les performances SS du transistor ne se dégradent pas aux températures élevées. Lorsque la température augmente, le I -V la courbe se déplace vers un V plus négatif GS en raison de l'effet dominant de la ferroélectricité, qui est contraire à la tendance d'un MOSFET conventionnel. La figure 9b résume les décalages de la tension d'hystérésis et de la tension de seuil de commutation directe avec la température. Transférer V GS passe à des valeurs plus négatives à mesure que la température augmente, ce qui peut être dû à une augmentation de E c du NEI.

un Je DS -V GS d'un NCFET NEI (3,6 nm) mesuré à 10 °C et 30 °C. Les courbes montrent un décalage vers une tension plus négative avec l'augmentation de la température, comme prévu. L'encart montre le point abrupt SS. b Tracés statistiques de l'hystérésis (à gauche) et de l'avance V GS @ 10 −7 A/μm (à droite) pour les NCFET avec une couche NEI de 3,6 nm. Transférer V GS se déplace dans le sens négatif avec l'augmentation de la température

NEI FeFET pour application de mémoire non volatile

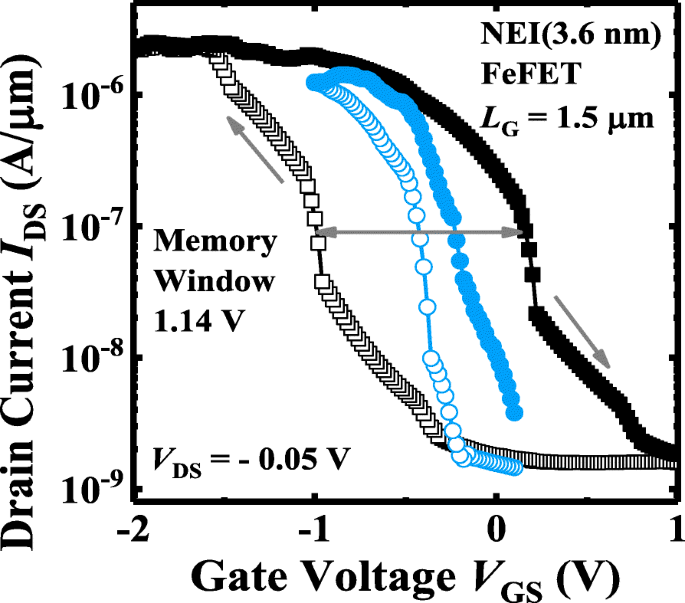

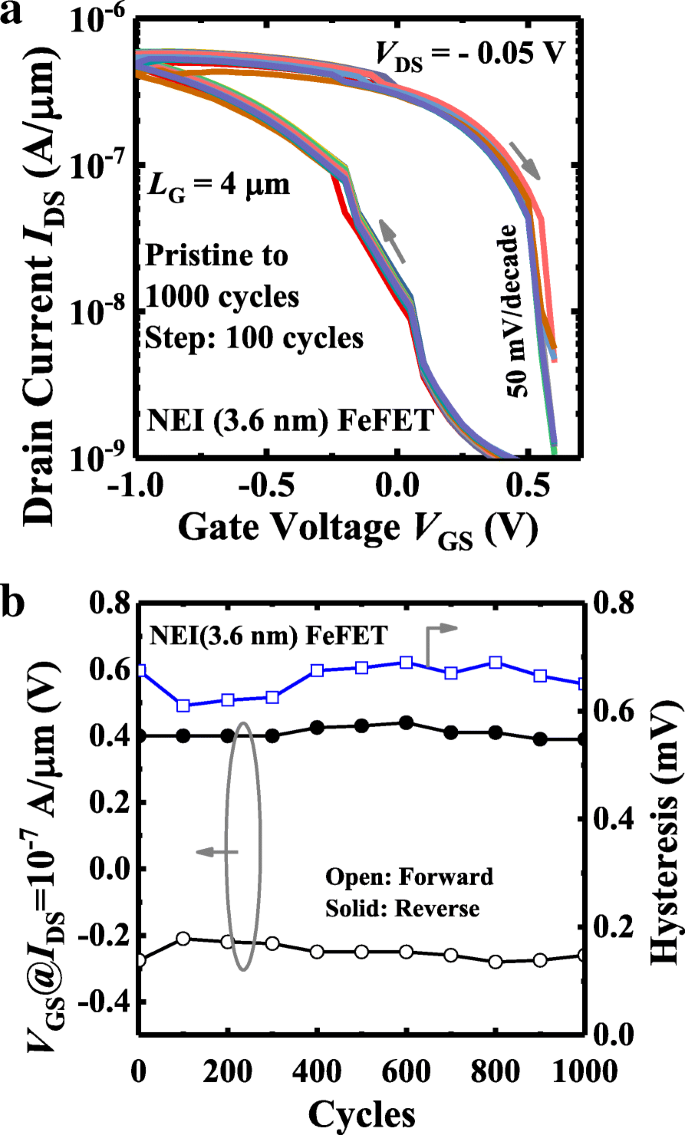

En augmentant la plage de V GS balayage, la tension d'hystérésis d'un NEI FeFET peut être augmentée pour obtenir une fenêtre mémoire (MW) large et stable pour les opérations de lecture et d'écriture. Comme le montre la figure 10, un FeFET avec un NEI de 3,6 nm démontre que le MW augmente de 0,2 à 1,14 V en tant que V GS la plage de balayage varie de (0,1 V, − 0,1 V) à (1 V, − 2 V). L'endurance de balayage CC d'un autre dispositif de mémoire FeFET est représentée sur la figure 11a, la figure 11b illustre les caractéristiques d'hystérésis en fonction du nombre de cycles de balayage CC. I-V stable une fenêtre d'hystérésis de ~ 0.65 V est visible.

Pour un grand V GS Plage de balayage DC, un MW de 1,14 V est observé pour le FeFET NEI (3,6 nm)

un Mesuré I DS -V GS courbes pour NEI (3,6 nm) FeFET, à travers 1000 cycles de balayage DC. b Les mesures d'endurance de balayage CC montrent que le NEI FeFET a un MW stable sur 1000 cycles

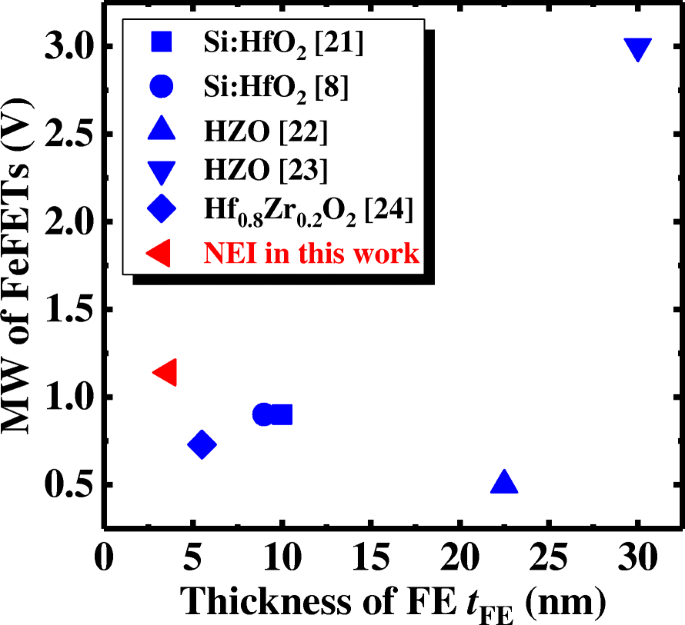

La figure 12 compare le dispositif de mémoire NEI FeFET aux FeFET rapportés, en ce qui concerne l'épaisseur des couches MW et FE [8, 21-24]. Il convient de noter que le dispositif NEI FeFET dans ce travail atteint un MW important (> 1 V) avec l'épaisseur FE la plus mince signalée de 3,6 nm. Nous supposons qu'il est plus facile d'atteindre la phase FE stable dans NEI avec une épaisseur plus petite, par rapport au HfO dopé 2 [28,29,30].

Analyse comparative du dispositif de mémoire NEI FeFET par rapport aux FeFET signalés, en ce qui concerne MW et t FE . Le FE le plus fin est obtenu grâce au dispositif de mémoire NEI FeFET

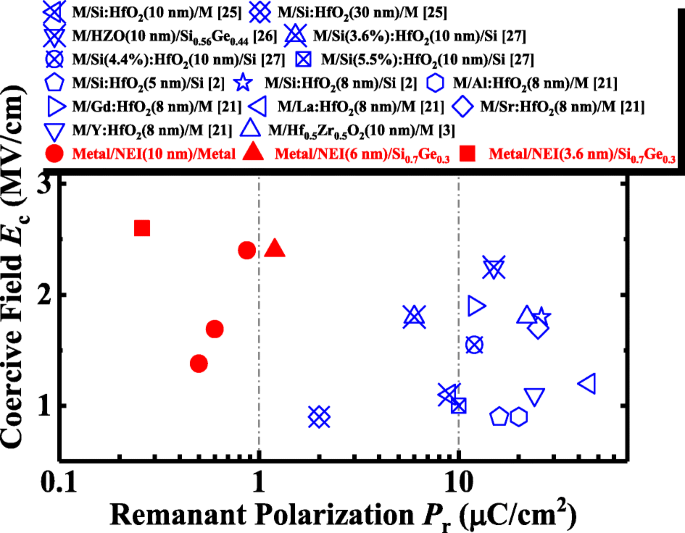

Enfin, les avantages du NEI FeFET apporté par ZrO2 les nanocristaux noyés dans l'isolant de grille amorphe sont discutés. La figure 13 compare la couche NEI au HfO dopé signalé2 films [2, 3, 21, 25-27], en ce qui concerne E c et P r . NEI peut atteindre un P bien inférieur r par rapport au HfO dopé2 pour un E similaire c . Nos expériences ont démontré qu'un P r en dessous de 1 C/cm 2 peut fournir le MW requis dans les FeFET. Une polarisation excessive pourrait conduire à une plus grande dépolarisation, entraînant de pires caractéristiques de rétention, ce qui a été rapporté dans [25]. De plus, les propriétés FE et DE de la couche NEI peuvent être ajustées séparément :P r est amélioré/réduit en augmentant/diminuant le volume de nanocristaux FE, et κ est augmenté en incorporant d'autres éléments dans la matrice amorphe (par exemple . , LaAlO3 ), pour optimiser les performances du FeFET.

Analyse comparative des couches NEI par rapport au HfO dopé signalé2 films, en ce qui concerne E c et P r . NEI atteint un P bien inférieur r par rapport au HfO dopé2 tout en conservant un E similaire c. [2, 3, 21, 25,26,27]

Conclusions

Nouveaux FeFET avec ZrO2 nanocristaux noyés dans un Al2 amorphe O3 couche d'isolation de grille sont signalés. Les analyses physiques indiquent que moins de 0,5 % de Zr dans Al2 O3 produit suffisamment de ferroélectricité pour les applications NCFET et NVM. Un effet NC stable est observé à différentes températures de mesure. Un fonctionnement stable de la mémoire FeFET avec un isolant de grille record (épaisseur totale de 3,6 nm) est démontré. Une MW stable est obtenue sur 1000 cycles d'endurance CC. La conception NEI FeFET proposée fournit une voie pour réduire l'épaisseur de la couche d'isolant de grille FE/DE pour être compatible avec les FinFET avec de très petits pas d'ailettes.

Abréviations

- Al2 O3 :

-

Oxyde d'aluminium

- ALD :

-

Dépôt de couche atomique

- BF2 + :

-

Ion fluorure de bore

- DC :

-

Courant continu

- Ec :

-

Champ coercitif

- FeFET :

-

Transistor ferroélectrique à effet de champ

- Voir :

-

Germanium

- GeOx :

-

Oxyde de Germanium

- HF :

-

Acide fluorhydrique

- HRTEM :

-

Microscope électronique à transmission haute résolution

- Je DS :

-

Courant de vidange

- MOSFET :

-

Transistors à effet de champ métal-oxyde-semiconducteur

- MW :

-

Fenêtre mémoire

- NC :

-

Capacité négative

- NDR :

-

Résistance différentielle négative

- NEI :

-

Isolant en nanocristaux

- Non :

-

Nickel

- Pr :

-

Polarisation résiduelle

- RTA :

-

Recuit thermique rapide

- SS :

-

Balançoire sous le seuil

- TaN :

-

Nitrure de tantale

- V GS :

-

Tension de grille

- V TH :

-

Tension de seuil

- ZrO2 :

-

Dioxyde de zirconium

Nanomatériaux

- Capteurs et processeurs convergent pour les applications industrielles

- Nanoparticules d'or multifonctionnelles pour des applications diagnostiques et thérapeutiques améliorées :une revue

- Avancées et défis des nanomatériaux fluorescents pour la synthèse et les applications biomédicales

- Technologies avancées de dépôt de couche atomique pour les micro-LED et les VCSEL

- Composites de graphène et polymères pour applications de supercondensateurs :une revue

- Évaluation des structures graphène/WO3 et graphène/CeO x en tant qu'électrodes pour les applications de supercondensateurs

- Variateurs pour applications de réfrigération et de refroidissement industriels

- Tours oscillants pour applications d'alésage et de tournage

- Métaux spéciaux pour les applications de dispositifs médicaux