Comment utiliser le type VHDL le plus courant :std_logic

Le type le plus couramment utilisé en VHDL est le std_logic . Considérez ce type comme un bit unique, l'information numérique transportée par un seul fil physique. Le std_logic nous donne un contrôle plus précis sur les ressources de notre conception que le integer type, que nous avons utilisé dans les tutoriels précédents.

Normalement, nous voulons qu'un fil dans une interface numérique ait soit la valeur '1' ou '0' . Ces deux valeurs sont les seules valeurs qu'un bit, un chiffre binaire, peut avoir. Mais en réalité, un signal numérique physique peut être dans un certain nombre d'états, dont le std_logic type fait un bon travail d'émulation. C'est donc le type le plus fréquemment utilisé en VHDL.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

Le std_logic type peut prendre les valeurs suivantes :

| ‘1’ | Logique 1 |

| ‘0’ | 0 logique |

| ‘Z’ | Haute impédance |

| ‘W’ | Signal faible, impossible de dire si 0 ou 1 |

| ‘L’ | Faible 0, pulldown |

| ‘H’ | Faible 1, pullup |

| ‘-‘ | M'en fiche |

| « O » | Non initialisé |

| ‘X’ | Inconnu, plusieurs pilotes |

Cela peut sembler être beaucoup d'états différents pour un type censé modéliser une seule valeur binaire. Ne vous inquiétez pas, nous n'utiliserons pas tous ces types dans cette série de tutoriels. Nous utiliserons '1' et '0' bien sûr. Et nous verrons également 'U' et 'X' , ce qui nous aidera à repérer les erreurs dans notre conception. Les autres valeurs sont des fonctionnalités VHDL avancées qui peuvent être utilisées pour des choses comme la modélisation de la communication avec par exemple I

2

périphériques C, ou pour créer des bus à trois états.

Si plusieurs processus essaient d'écrire des valeurs différentes sur un signal, on dit qu'il a plusieurs pilotes . Si un std_logic signal a plusieurs pilotes, ce ne sera pas une erreur de compilation ou d'exécution, du moins pas dans le simulateur. C'est parce que std_logic est un type résolu , ce qui signifie que sa valeur sera déterminée par une fonction de résolution.

La valeur d'un std_logic le signal avec deux pilotes sera déterminé sur la base de ce tableau de résolution :

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Exercice

Dans ce didacticiel vidéo, nous allons apprendre à utiliser déclarer et afficher std_logic signaux dans une forme d'onde :

Le code final que nous avons créé dans ce tutoriel :

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

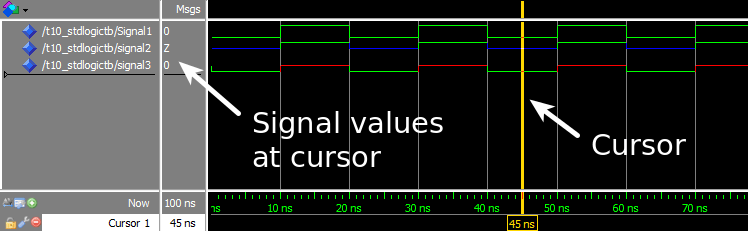

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

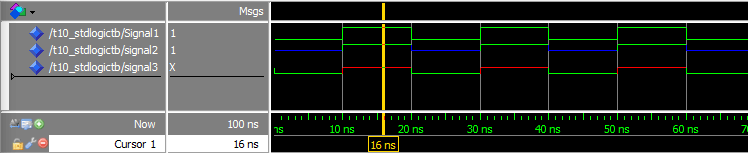

La forme d'onde avec le curseur placé sur l'autre partie du cycle de signal répétitif :

Analyse

L'exercice a démontré comment la fonction de résolution de VHDL fonctionne avec le std_logic taper. Lorsque vous travaillez avec la logique numérique, il est souvent plus pratique d'étudier la chronologie dans une forme d'onde plutôt que d'utiliser des impressions. Par conséquent, nous avons utilisé la forme d'onde ModelSim pour vérifier les valeurs du signal dans cet exercice.

Le premier processus et Signal1 n'est utilisé que pour changer la valeur que le troisième processus pilote sur Signal2 et Signal3 .

Le deuxième processus, le pilote A, essaiera de piloter un 'Z' sur Signal2 , et un '0' sur Signal3 constamment.

Le troisième processus, Conducteur B, alternera entre la conduite '1' et 'Z' sur les deux Signal2 et Signal3 .

Nous voyons dans les captures d'écran de la forme d'onde que Signal1 change entre '0' et '1' , car il n'y a qu'un seul processus essayant de piloter ce signal. Nous pouvons également voir que les signaux de plusieurs pilotes sont résolus selon le tableau de résolution publié dans les commentaires du code VHDL :

| Signal | Conducteur A | Conducteur B | Résultat |

|---|---|---|---|

| Signal2 | 'Z' | 'Z' | 'Z' |

| Signal2 | 'Z' | ‘1’ | ‘1’ |

| Signal3 | ‘0’ | 'Z' | ‘0’ |

| Signal3 | ‘0’ | ‘1’ | 'X' |

À emporter

std_logicest le type le plus couramment utilisé pour contenir une valeur de bit unique en VHDL- Pensez à un

std_logicsignal sous forme de fil physique dans notre conception numérique - Si plusieurs processus essaient de générer un

std_logicsignal, sa valeur est déterminée par une table de résolution

Aller au tutoriel suivant »

VHDL

- Les goulots d'étranglement du flux de travail d'impression 3D les plus courants – et comment les résoudre

- Les problèmes de système de refroidissement de voiture les plus courants

- Comment tirer le meilleur parti de vos données

- Comment créer une liste chaînée en VHDL

- Comment utiliser une procédure dans un processus en VHDL

- Comment utiliser une fonction en VHDL

- Comment utiliser en toute sécurité un treuil à moteur sur le lieu de travail

- Les causes les plus courantes d'accidents de grue (et comment les éviter)

- Les applications les plus courantes de a286