Une RRAM SRAM 4T intégrée avec charge de commutation résistive à auto-inhibition par un processus logique CMOS pur

Résumé

Cet article présente une nouvelle mémoire à accès aléatoire statique non volatile 4T2R entièrement compatible avec la logique (nv-SRAM) dotée de son mécanisme de stockage de données à auto-inhibition pour les applications SRAM basse consommation/haute vitesse. Avec une zone de cellule compacte et une compatibilité logique complète, cette nouvelle nv-SRAM intègre deux STI-ReRAM intégrées à la SRAM 4T. Les données peuvent être lues/écrites via une structure volatile à couple croisé pour maintenir une vitesse d'accès rapide. Les données peuvent être stockées de manière non volatile dans une nouvelle cellule SRAM grâce à une opération d'auto-inhibition unique sur la charge de la mémoire résistive à accès aléatoire (RRAM), atteignant une puissance statique nulle pendant la conservation des données.

Contexte

Ces dernières années, diverses mémoires statiques à accès aléatoire de faible puissance ont été développées pour répondre aux besoins des systèmes informatiques sur les appareils portables et les applications IOT [1,2,3,4,5,6]. À mesure que la technologie CMOS passe au régime nanométrique, le courant de fuite à l'état bloqué augmente considérablement, ce qui entraîne une aggravation de la consommation d'énergie statique pour les modules de mémoire volatiles [7, 8]. La consommation d'énergie statique augmentée par le courant de fuite dans les transistors à l'échelle nanométrique est devenue l'un des principaux défis pour l'avancement des SRAM de faible puissance. [9,10,11]. Au fil des ans, différentes structures cellulaires ou techniques de fonctionnement [12,13,14,15,16] ont été proposées pour minimiser la consommation d'énergie dans les SRAM. Certaines des cellules nouvellement proposées incorporent des éléments de stockage non volatils, tels que la mémoire vive résistive (RRAM) et la mémoire vive magnétorésistive (MRAM) [17,18,19,20], pour obtenir une puissance de maintien nulle tout en maintenant un faible fonctionnement puissance et vitesse d'accès rapide dans le traitement des données volatiles. Cependant, l'ajout d'éléments de stockage non volatils sur des matrices SRAM à base logique nécessite généralement des couches et/ou des processus supplémentaires aux plates-formes logiques standard [21,22,23]. Cela augmentera inévitablement la complexité des processus de leur développement. De plus, ces RRAM et MRAM back-end nécessitent une grande structure de connexion, composée de plusieurs piles de vias et de métaux vers les cellules SRAM. Ces structures de pontage augmentent la capacité parasite vers le nœud de stockage de données SRAM, affectant la vitesse d'accès de ces cellules SRAM non volatiles [24, 25]. Dans nos travaux précédents [26], une nouvelle nv-SRAM 4T à puissance statique nulle avec des RRAM à paroi latérale STI situées à côté des nœuds de stockage flottants de la SRAM 4T a été proposée pour la première fois. Dans cette lettre, cette nv-SRAM 4T2R dotée d'un stockage de données non volatile, d'une puissance de maintien nulle et d'une vitesse d'accès rapide sera analysée plus en détail et optimisée pour les applications NVM intégrées.

Méthodes

Structure cellulaire STI-ReRAM

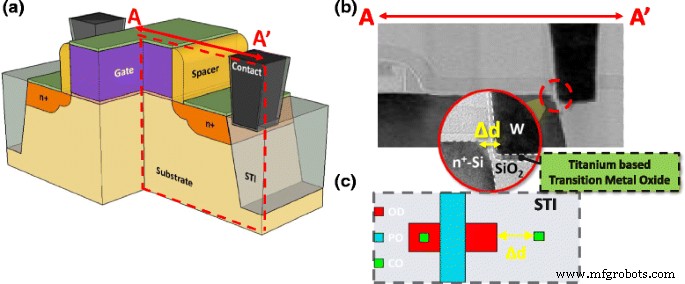

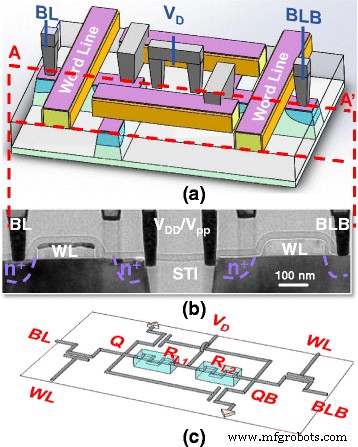

Dans la structure 3D STI-RRAM de la figure 1a, le nœud de stockage résistif est composé d'un oxyde de métal de transition (TMO) entre deux électrodes, la région N+ et un bouchon de tungstène sur les côtés gauche et droit, respectivement. Comme le montre l'image TEM de la figure 1b et la disposition de la figure 1c, en plaçant le contact sur la région STI avec une distance appropriée par rapport à la région N+, le SiO2 restant et la couche barrière sous la prise de tungstène deviennent un film TMO et présentent la qualité de commutation résistive.

un Illustration 3D d'une cellule 1T1R avec STI-ReRAM juste à côté de la jonction n+. b L'image TEM correspondante du nœud de stockage résistif composé d'oxydes métalliques de transition, formé entre un contact spécialement placé et la région n+ du transistor sélectionné. c Disposition

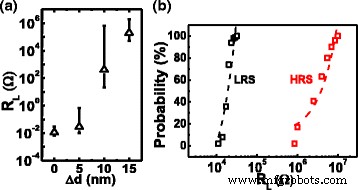

L'épaisseur du TMO peut être contrôlée en choisissant un espacement approprié Δd entre un contact et la région de diffusion N+. Sur la base de la mesure de la figure 2a, il existe une corrélation positive entre le niveau de résistance initial et la distance tracée,Δd, déterminée par les masques définissant les régions STI et de contact, respectivement. Pour l'étude suivante, la RRAM avec Δd égal à 10 nm est choisie pour sa tension de formation plus faible et préférablement RL distribution à la fois dans l'état de faible résistance (LRS) et dans l'état de haute résistance (HRS) comme résumé dans la figure 2b. Avec un contrôle approprié de la tension de la ligne de mots (WL) pendant les opérations de définition/formation, le courant défini peut être limité localement par le transistor sélectionné, permettant de meilleures performances d'endurance.

un La résistance initiale mesurée des échantillons STI-RRAM avec différents d. b Probabilité cumulée de la résistance de charge après la réinitialisation/le réglage de la STI-RRAM aux états de résistance élevée et faible

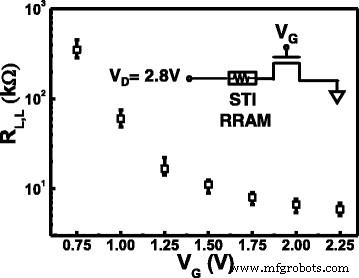

Les données de la figure 3 révèlent en outre que le niveau de courant de lecture dans LRS peut être bien contrôlé par la tension de grille, VG . Pendant le formage à VD =2,8 V, le transistor de sélection limite le courant maximum traversant la STI-RRAM une fois que l'appareil est réglé sur LRS. Le niveau de résistance d'état LRS ultérieur est inversement proportionnel au courant localement bloqué, qui a été trouvé dans divers dispositifs RRAM à base de TaO [27, 28].

Corrélation entre les niveaux de résistance de charge, RL,L , et la tension de grille appliquée pendant le réglage. Les données suggèrent que différents RL,L peut être obtenu en définissant un niveau différent de tension de grille sélectionnée

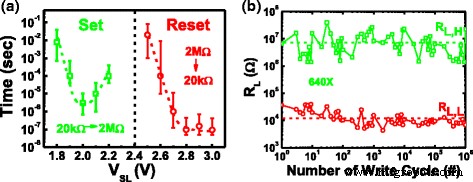

Pour garantir les caractéristiques de commutation résistive de la STI-RRAM, le temps de réglage et le temps de réinitialisation sont testés, comme le montre la figure 4a. Les opérations de définition et de réinitialisation peuvent être optimisées lorsque VSL = 2 et 2,8 V, respectivement. Le test d'endurance RRAM est résumé dans la figure 4b. En utilisant un algorithme de programmation d'impulsions incrémentielles, sa fenêtre de lecture peut rester stable après 1 million de cycles.

un Temps de réglage et de réinitialisation résumés par rapport à VPP . b Résultat du test d'endurance d'un million de cycles de la STI-RRAM utilisant l'algorithme de programmation d'impulsions incrémentielles

Concept SRAM non volatile

L'illustration 3D de la Fig. 5 montre la structure cellulaire nouvellement proposée 4T2R nv-SRAM et son image TEM en coupe transversale correspondante le long de la ligne de coupe AA'. Deux STI-RRAM servent à la fois de nœuds de stockage non volatils et de résistances de charge, qui sont pris en sandwich entre les régions de diffusion Q et QB N+ et un contact étroitement posé sur les bords STI avec une conception d'espacement appropriée. L'image TEM montre une STI-RRAM bien formée sur les côtés gauche et droit de la région d'isolement et donne une cellule assez compacte avec ces nœuds de stockage non volatils étroitement placés au même niveau des transistors.

un Illustration 3D de la structure cellulaire nv-SRAM 4T2R proposée et du b image MET transversale correspondante. c Le schéma de circuit d'une cellule SRAM est affiché avec deux résistances RRAM comme dispositifs de chargement

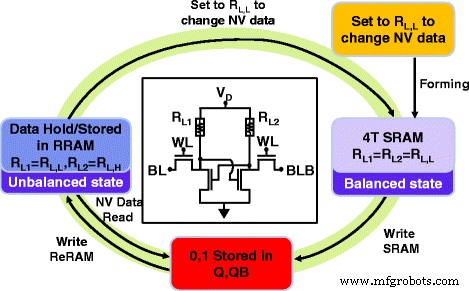

La nv-SRAM 4T proposée peut fonctionner en modes volatil et non volatil. Ses quatre états différents et son schéma de fonctionnement sont illustrés sur la figure 6.

Schéma de circuit de la cellule nv-SRAM et son organigramme correspondant pour basculer entre les opérations SRAM volatiles et non volatiles

Dans ses états initiaux, STI-RRAM porte généralement un niveau de résistance de 10 8 Ω, alors que le film TMO est intact. Grâce à une opération de formation de couverture, les cellules nv-SRAM peuvent être initialisées simultanément bloc par bloc à VD = 2.8 V. Les deux RL1 et RL2 (résistance de charge à gauche et à droite, respectivement) sont initialisés à RL,L . Le dernier RL,L un niveau de 20 ~ 370 kΩ peut être contrôlé en donnant une tension WL différente pendant l'opération de formage. La cellule atteint alors un état d'équilibre, c'est-à-dire que les deux résistances de charge sont au même état. Dans cet état, cette cellule peut maintenant fonctionner comme la SRAM 4T2R typique, traitant les données volatiles de manière conventionnelle, en stockant les données dans le verrou à couplage croisé.

Pour stocker les données de manière non volatile, les données verrouillées complémentaires peuvent être stockées sur les RRAM par un mécanisme d'auto-inhibition hérité dans cette cellule. Lorsque les données sont stockées avec succès dans la paire RRAM, on peut couper l'alimentation pour une conservation permanente des données. Pour accéder à l'état stocké, réappliquez simplement VDD au tableau. Les données non volatiles seront restaurées automatiquement sur les nœuds Q et QB et sont accessibles via le mode de lecture SRAM conventionnel. Enfin, pour actualiser les données non volatiles, une opération d'ensemble de couverture est appliquée aux matrices SRAM afin que la matrice revienne à son état d'équilibre.

Résultats et discussion

Analyse électrique

Les conditions de fonctionnement des transitions entre les différentes étapes sont résumées dans le tableau 1.

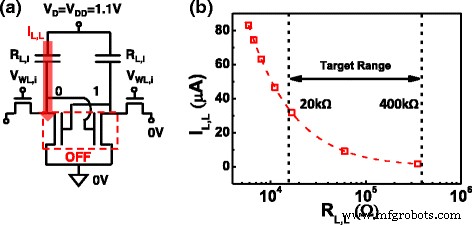

Différent RL,L Le niveau peut être obtenu en définissant une tension WL différente lors de l'initialisation d'un bloc ou d'un tableau. Compte tenu de la stabilité et de la tension de fonctionnement, le RL,L un niveau compris entre 20 et 400 kΩ est d'abord ciblé pour enquête dans cette étude. Correspondant à une tension WL de 0,75 à 1,25 V, la résistance de charge résultante diminue de manière assez linéaire, comme le montre la figure 3. Comme prévu, plus bas RL,L niveau conduira à un courant de veille plus élevé, voir Fig. 7. Cependant, RL,L doit rester suffisamment faible pour assurer une grande fenêtre de données agrandie entre les deux états de résistance. Les fenêtres de données statiques, dynamiques et non volatiles doivent être prises en compte pour une optimisation supplémentaire du RL,L ciblé , qui est défini par la condition d'initialisation.

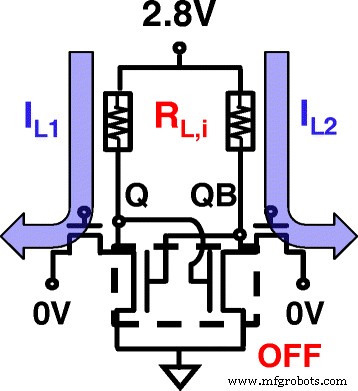

un Cellule SRAM 4T2R en condition de maintien. b Comme prévu, niveau de résistance de charge, IL,L pendant le maintien peut être abaissé efficacement en choisissant un RL,L plus élevé

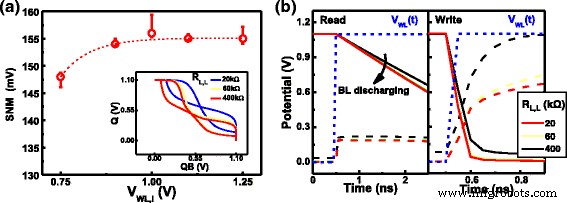

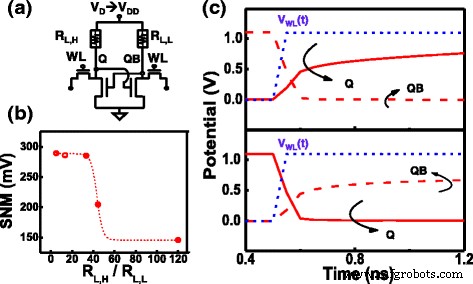

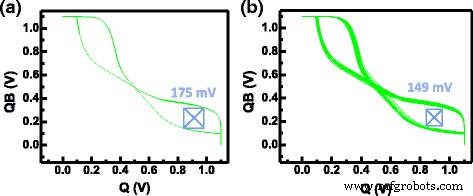

La caractérisation statique et dynamique de la nv-SRAM à l'état d'équilibre est d'abord étudiée, en considérant des cellules initialisées par différentes conditions. Sur la figure 8, la marge de bruit statique (SNM) obtenue par les multiples courbes papillon des cellules initialisées par différentes tensions WL. Les données révèlent que RL,L niveau a un effet minimal sur la marge de lecture des cellules équilibrées, lorsque les résistances de charge sont dans la plage cible. La distribution SNM de plusieurs cellules dans les états d'équilibre dans différentes conditions d'initialisation est résumée sur la figure 8a. Dans l'ensemble, les SNM restent assez stables d'une cellule à l'autre, tandis qu'une marge de lecture raisonnable peut être établie avec une tension WL inférieure à VDD , ce qui peut être bénéfique pour les applications à faible consommation. Pour étudier les caractéristiques dynamiques de lecture et d'écriture de cette cellule à l'état équilibré, les réponses transitoires de l'écriture « 1 » et « 0 » sont résumées sur la figure 8b. On constate que plus RL,L réduit la vitesse de remontée vers les nœuds Q, QB, ce qui peut augmenter légèrement le temps transitoire pendant les opérations de lecture et d'écriture. Cependant, la vitesse de réponse est toujours dans la plage attendue. Les données ci-dessus suggèrent qu'à l'état d'équilibre, cette nv-SRAM 4T2R peut traiter des données volatiles comme des SRAM conventionnelles.

un La marge de bruit statique de lecture (SNM) des cellules SRAM proposées avec une tension WL différente lors de l'initialisation. Un SNM raisonnable peut être maintenu dans une plage assez large de RL,L de 20~400 kΩ. b Les caractéristiques dynamiques de lecture et d'écriture d'une cellule dans des conditions de charge équilibrées révèlent un bon temps de réponse en quelques nanosecondes. RL,L plus élevé réduit légèrement la vitesse de traction pendant l'opération d'écriture

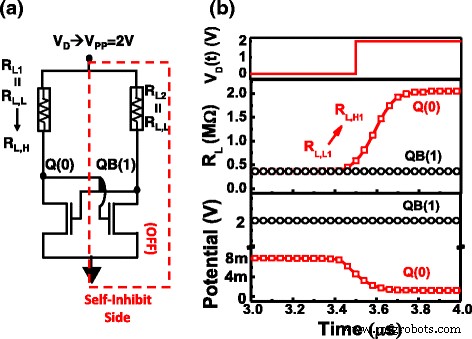

Pour stocker des données dans la paire STI-RRAM, cette cellule permet une réinitialisation auto-sélective d'une seule des RRAM dans la paire de résistances de charge, ce qui permet aux données d'être écrites de manière non volatile en appliquant un Vpp tension au nœud d'alimentation au bloc de cellules uniformément. Une fois que les données de verrouillage sont stockées dans les nœuds Q et QB, une écriture non volatile est réalisée par le mécanisme d'auto-inhibition dans la structure de couplage croisé avec RRAM, comme illustré sur la figure 9a. Un seul côté de la RRAM avec une basse tension au nœud Q sera réinitialisé sur RL,H . Le courant sur l'autre branche est presque nul car le transistor pull-down est désactivé par le faible VQ .

un Illustration du mécanisme d'auto-inhibition lors de l'écriture de données non volatiles en réinitialisant un côté de deux RRAM. b Changement dynamique de RL et Q, le potentiel QB vérifient l'auto-inhibition de l'écriture des données de verrouillage dans les RRAM

Les données sont stockées dans la paire RRAM en tant que VPP l'impulsion est appliquée au nœud d'alimentation. Lors de l'écriture de données non volatiles, la commutation dynamique de RL et la réponse transitoire du potentiel Q, QB sont résumées sur la figure 9b. Les données de mesure suggèrent que pour réinitialiser avec succès la STI-RRAM sélectivement d'un côté, une impulsion de 300 ns à Vpp = 2 V est suffisant. Pour garantir que le fonctionnement volatil ne soit toujours pas affecté lorsque les cellules sont à l'état déséquilibré comme la figure 10a, la distribution SNM des cellules avec différents RL,H /RL,L rapport sont résumés dans la figure 10b. On constate que le faible rapport de résistance entre les états ne dégrade pas le maintien SNM. Pour garantir qu'une cellule avec une charge déséquilibrée, une écriture dynamique de données dans une telle cellule est caractérisée. Les données révèlent que les deux états peuvent être écrits avec succès, surmontant le rapport de résistance de déséquilibre initial de 2 M/400 k, comme le montre la figure 10c.

un Structure de couple croisé pendant la charge de déséquilibre. b Marge de bruit statique avec différentes tensions WL lors de l'initialisation. c Écriture dynamique pour deux états de données différents. Déséquilibre RL,L = 400 kΩ peut aussi s'écrire

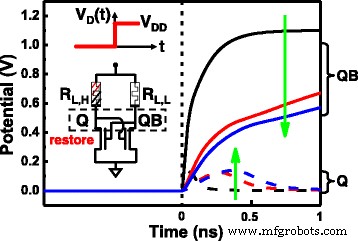

Pour recharger les données volatiles précédemment stockées dans la RRAM, on peut simplement appliquer VDD au nœud d'alimentation, la charge de déséquilibre dans les RRAM est auto-restaurée aux nœuds de verrouillage de Q et QB, comme illustré sur la Fig. 11.

Restauration des données non volatiles stockées dans Q et QB à partir d'un état de charge RRAM déséquilibré. Le potentiel des nœuds Q et QB peut tous deux être restauré après la remise sous tension en quelques nanosecondes

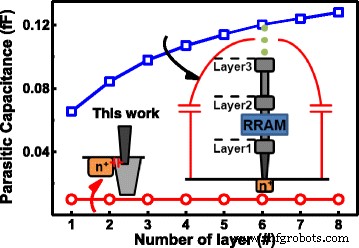

Effet parasite et comparaison

En incorporant la STI-RRAM entièrement compatible avec la logique dans cette nouvelle cellule SRAM, cette cellule peut être facilement implémentée par la plupart des processus logiques standard sans ajouter de couches de masquage ni d'étapes de processus. Cette fonctionnalité peut grandement améliorer ses applications et sa flexibilité dans divers modules IP de mémoire non volatile nécessaires dans de nombreux systèmes IC. De plus, la nv-SRAM 4T2R proposée présente une capacité parasite beaucoup plus petite par rapport aux autres nv-SRAM précédemment signalées [29, 30, 31] qui nécessitent des composants non volatils de fin de ligne (BEOL). Afin de connecter les nœuds Q et QB de la surface de Si à ces BEOL RRAM ou MRAM, plusieurs empilements de couches métalliques et via sont nécessaires. Ces grandes structures de pontage conduisent à un effet RC parasite important. Une grande capacité parasite introduite dans les nœuds internes à l'intérieur des cellules SRAM peut affecter de manière critique le temps de réponse des appareils.

Pour comparer l'effet parasite sur ceux-ci, les nv-SRAM sont étudiées sur la base de l'estimation de la simulation post-implantation. En supposant que toutes les cellules soient mises en œuvre par la même technologie CMOS standard, la capacité parasite sur les nœuds de verrouillage augmente à mesure que le nombre de couches métalliques augmente pour les cellules nécessitant de grandes structures de pontage. Pour la nouvelle nv-SRAM utilisant STI-RRAM, il y a très peu d'augmentation de la capacité globale sur les nœuds verrouillés. De plus, il est indépendant du nombre de couches métalliques adaptées dans un circuit particulier. Pour étudier plus en détail l'effet de la capacité parasite de la vitesse de la SRAM, la réponse dynamique simulée des cellules SRAM proposée dans [29,30,31] et ce travail sont comparés à la Fig. 12.

Capacité parasite sur les nœuds de verrouillage des cellules nv-SRAM de la référence [30] et qu'à partir de ce travail basé sur la technologie CMOS 40 nm, une augmentation significative de la capacité parasite est constatée à mesure que le nombre de couches métalliques augmente

Une capacité parasite beaucoup plus petite de cette nv-SRAM intégrée peut conduire à un temps de réponse plus rapide pendant l'opération de lecture dynamique dans la cellule SRAM. Cela empêche la grande capacité interne du pont de connexion d'avoir un impact sur le temps de réponse de la matrice SRAM basée sur la logique.

Le tableau 2 compare les principales caractéristiques des précédentes SRAM non volatiles rapportées incorporées avec des RRAM ou des MRAM back-end et ce travail. Malgré la tension de commutation d'état plus élevée, la nv-SRAM basée sur STI-RRAM est présentée avec une capacité parasite beaucoup plus petite sur les nœuds internes verrouillés à l'intérieur des cellules SRAM et une compatibilité logique totale.

Dégradation de la marge de bruit statique induite par la variation

Pour assurer le SNM stable avec des cellules soumises à des variations de processus, des fluctuations des niveaux de résistance RRAM et de la tension de seuil du transistor, VT , sont pris en compte dans les enquêtes suivantes :discordances dans VT est connu pour provoquer un décalage SNM dans la SRAM par des technologies à l'échelle [32, 33]. En outre, cela peut également entraîner un courant de conformité défini différent, ce qui peut à son tour entraîner une variation accrue du niveau de résistance des deux RL,L . Comme illustré sur la Fig. 13, différents VT conduire à un courant de conformité d'initialisation différent dans la cellule STI-RRAM, conduisant à une nouvelle inadéquation dans RL,L . Pour analyser l'impact de VT variation sur SNM, nous supposons VT être une variable aléatoire gaussienne avec une moyenne et une variation basées sur des rapports précédents [34]. Par simulation Monte-Carlo, la distribution des courbes papillon soumises à des variations de RL,L sont résumés dans la figure 14a. Lorsque les deux variations de RL,L et VT sont pris en compte, un rétrécissement significatif de la fenêtre SNM est observé, comme le montre la figure 14b. La variabilité accrue de la nv-SRAM doit être prise en compte dans les études futures.

VT la variation conduit à une conformité d'initialisation différente IL,1 et IL,2

Courbes papillon par simulations Monte-Carlo comparant les dégradations SNM causées par a variation de RL,L après initialisation et b variations dans les deux RL,L et VT

Conclusions

Une nouvelle SRAM non volatile basée sur 4T2R STI-RRAM entièrement compatible avec le processus logique CMOS a été démontrée avec succès dans un processus logique CMOS pur à un nœud technologique de 40 nm sans masques ni étapes supplémentaires. Cette cellule nv-SRAM est dotée d'un mécanisme d'auto-inhibition et d'auto-restauration pour les données non volatiles, une petite capacité parasite sur les nœuds de verrouillage et une alimentation statique nulle pendant la conservation des données. Ces caractéristiques supérieures font de la nv-SRAM basée sur STI-RRAM une solution prometteuse pour les futures applications de mémoire non volatile logique basse consommation/haute vitesse.

Nanomatériaux

- Introduction aux circuits intégrés numériques

- Circuits intégrés

- Logique numérique avec commentaires

- Circuits de commutation de diodes

- Alimentation dans les circuits CA résistifs et réactifs

- Correction pratique du facteur de puissance

- Modèle de rétention de TaO/HfO x et TaO/AlO x RRAM avec caractéristiques de commutateur auto-rectifiant

- Caractéristiques de commutation résistive bipolaire des dispositifs RRAM à structure tricouche HfO2/TiO2/HfO2 sur des substrats revêtus de Pt et de TiN fabriqués par dépôt de couche atomique

- Mémoire résistive ZrO2/ZrO2 − x /ZrO2 sans conformité avec comportement de commutation multi-états interfacial contrôlable