Synchronisation et distribution de réinitialisation asynchrone – ASIC et FPGA

Le manque de coordination entre les réinitialisations asynchrones et les horloges logiques synchrones entraîne des pannes intermittentes à la mise sous tension. Dans cette série d'articles, nous discutons des exigences et des défis de la réinitialisation asynchrone et explorons des solutions avancées pour les conceptions ASIC vs FPGA.

Les réinitialisations asynchrones sont traditionnellement utilisées dans les conceptions VLSI pour amener les circuits synchrones à un état connu après la mise sous tension. L'opération de libération de réinitialisation asynchrone doit être coordonnée avec le signal d'horloge logique synchrone pour éliminer les échecs de synchronisation dus à un conflit possible entre la réinitialisation et l'horloge. Un manque de coordination conduit à des pannes intermittentes à la mise sous tension. Le problème s'exacerbe lorsque de grandes conceptions de domaines à horloges multiples sont envisagées. En plus des problèmes de synchronisation, la distribution d'une réinitialisation asynchrone à des millions de bascules est difficile, nécessitant des techniques similaires à CTS (Clock Tree Synthesis) et nécessitant des ressources de zone et de routage similaires.

Les exigences et les défis de la réinitialisation asynchrone sont passés en revue, en se concentrant sur les problèmes de synchronisation et de distribution. Les inconvénients des solutions classiques de réinitialisation de la synchronisation (réinitialisation de la synchronisation de l'arbre source) et de la distribution (réinitialisation de la synthèse de l'arbre) sont discutés. Des solutions avancées pour une convergence temporelle plus rapide et plus simple et une synchronisation et une distribution de réinitialisation plus fiables sont présentées. Différentes approches pour les conceptions ASIC versus FPGA sont détaillées.

La partie 1 décrit les problèmes liés aux réinitialisations asynchrones et décrit les approches permettant de résoudre ces problèmes. La partie 2 (cet article) présente des solutions supplémentaires pour une réinitialisation asynchrone correcte dans ASIC et FPGA. Quelques cas particuliers utiles sont discutés dans la partie 3.

2. Techniques de convergence de synchronisation de réinitialisation asynchrone

L'un des principaux problèmes abordés dans la partie 1 était la complexité de la libération de réinitialisation pour les grandes conceptions (avec un réseau de distribution de réinitialisation à latence élevée), en particulier lorsqu'un cycle d'horloge court est utilisé. La convergence temporelle basée sur l'optimisation STA standard conduit à une conception coûteuse et dans certains cas est même impossible. Nous discutons ici de deux techniques qui atténuent ce problème de synchronisation. Les deux techniques sont applicables pour les conceptions ASIC et FPGA.

2.1. Pipeline de réinitialisation asynchrone

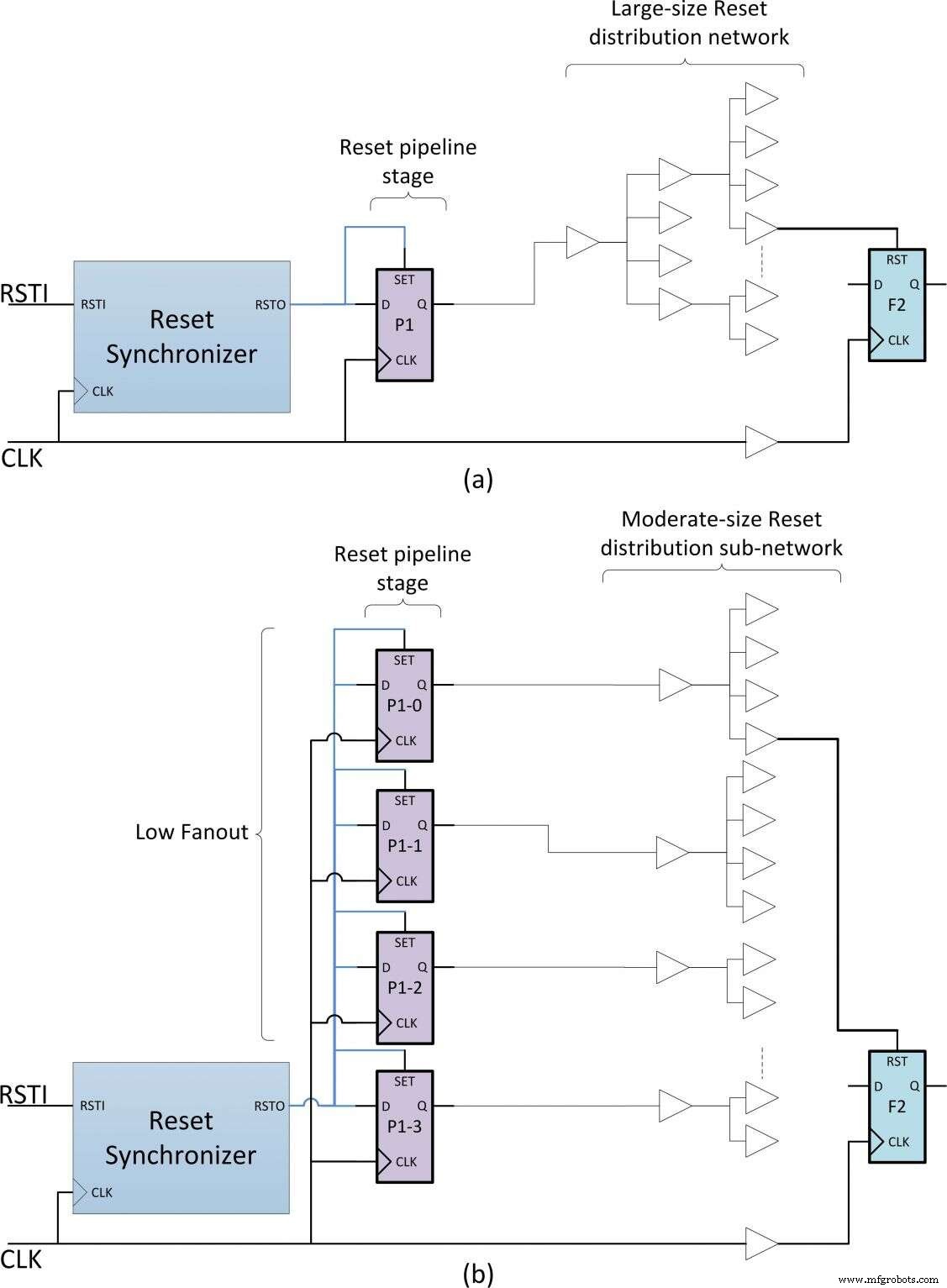

Une façon de traiter le problème de synchronisation de la libération de réinitialisation asynchrone consiste à troquer la latence de libération de réinitialisation pour une synchronisation plus souple. Ceci peut être réalisé en pipelinant l'arbre de réinitialisation de la manière suivante. Après chaque synchroniseur, un étage de bascule P1 à réglage asynchrone supplémentaire est inclus sur la ligne de réinitialisation (figure 6a). Les deux entrées SET et D de la bascule sont connectées au RSTO de réinitialisation haut actif provenant du synchroniseur de réinitialisation. Sur la version RSTO, les conditions de configuration et de maintien sont satisfaites pour les entrées P1 D et SET car elles sont contraintes comme des chemins synchrones réguliers.

cliquez pour agrandir l'image

Figure 6 :Réinitialisation asynchrone avec pipeline (Source :Circuits vSync)

Le fonctionnement fonctionnel du nouveau schéma est similaire à celui décrit dans la partie 1 (Figure 3d), à l'exception d'une latence à cycle unique supplémentaire sur la version de réinitialisation. La latence de réinitialisation plus élevée engendrée par cette technique est généralement acceptable pour la plupart des applications, car elle n'est engagée qu'une seule fois par mise sous tension.

Une partie complémentaire de cette technique couvre les contraintes de conception. Alors que les bascules du synchroniseur doivent être contraintes contre la duplication afin d'éviter les problèmes de chemin de reconvergence comme décrit dans la partie 1, l'étage de pipeline P1 est soumis à la contrainte MAX_FANOUT. Un exemple de contrainte de sortance maximale est illustré à la figure 6b. La bascule P1 est automatiquement dupliqué par l'outil de synthèse, créant quatre sous-réseaux pour la distribution de réinitialisation. Chaque sous-réseau a une latence inférieure à celle du réseau d'origine, répondant aux exigences de synchronisation pour la version de réinitialisation. De plus, la sortie du synchroniseur de réinitialisation rencontre facilement un fanout de huit.

Cette technique de pipeline de réinitialisation asynchrone est évolutive pour n'importe quelle taille de conception et ne nécessite aucune modification lorsque la conception change, car l'outil de synthèse duplique automatiquement l'étape P1, en gardant le sous-réseau de réinitialisation à latence modérée limité. La sortance de l'étage P1 dupliquée pour la sortie du synchroniseur est généralement petite et ne provoque pas de violations de synchronisation. Cependant, lorsqu'une seule étape de pipeline ne conduit pas à une convergence temporelle, des étapes de pipeline supplémentaires P2 - PN peuvent être incluses et contraintes avec différentes contraintes MAX_FANOUT.

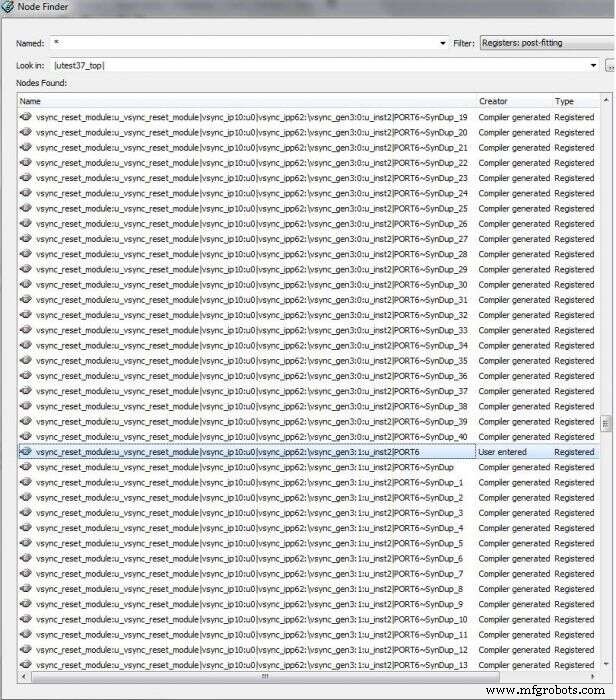

Un exemple de cette technique appliquée à une conception réelle est illustré à la figure 7. Le registre de l'étage P1, nommé PORT6, a été automatiquement dupliqué environ 40 fois par l'outil de synthèse [6] pour répondre à la contrainte MAX_FANOUT. Chacun des 40 sous-réseaux a respecté le timing pour son déploiement local.

cliquez pour agrandir l'image

Figure 7 :Exemple de pipeline de réinitialisation asynchrone (Source :Circuits vSync)

Embarqué

- Structures et classes en C++

- Boîtes aux lettres :présentation et services de base

- Sémaphores :introduction et services de base

- Anvo-Systems et Mouser signent un accord de distribution

- Mouser et Inventek Systems annoncent un accord de distribution mondial

- Rutronik et AP Memory signent un accord de distribution mondial

- Entreprises Séparées de Distribution et de Compoundage d'Albis Plastics

- L'art et la science de la sélection de sites de distribution

- Six façons de réduire les émissions dans l'entreposage et la distribution