Synchronisation et distribution de la réinitialisation asynchrone – défis et solutions

Le manque de coordination entre les réinitialisations asynchrones et les horloges logiques synchrones entraîne des pannes intermittentes à la mise sous tension. Dans cette série d'articles, nous discutons des exigences et des défis de la réinitialisation asynchrone et explorons des solutions avancées pour les conceptions ASIC vs FPGA.

Les réinitialisations asynchrones sont traditionnellement utilisées dans les conceptions VLSI pour amener les circuits synchrones à un état connu après la mise sous tension. L'opération de libération de réinitialisation asynchrone doit être coordonnée avec le signal d'horloge logique synchrone pour éliminer les échecs de synchronisation dus à un conflit possible entre la réinitialisation et l'horloge. Un manque de coordination conduit à des pannes intermittentes à la mise sous tension. Le problème s'exacerbe lorsque de grandes conceptions de domaines à horloges multiples sont envisagées. En plus des problèmes de synchronisation, la distribution d'une réinitialisation asynchrone à des millions de bascules est difficile, nécessitant des techniques similaires à CTS (Clock Tree Synthesis) et nécessitant des ressources de zone et de routage similaires.

Les exigences et les défis de la réinitialisation asynchrone sont passés en revue, en se concentrant sur les problèmes de synchronisation et de distribution. Les inconvénients des solutions classiques de réinitialisation de la synchronisation (réinitialisation de la synchronisation de l'arbre source) et de la distribution (réinitialisation de la synthèse de l'arbre) sont discutés. Des solutions avancées pour une convergence temporelle plus rapide et plus simple et une synchronisation et une distribution de réinitialisation plus fiables sont présentées. Différentes approches pour les conceptions ASIC versus FPGA sont détaillées.

La partie 1 (cet article) décrit les problèmes liés aux réinitialisations asynchrones et décrit les approches pour résoudre ces problèmes. La partie 2 présente des solutions supplémentaires pour une réinitialisation asynchrone correcte dans ASIC et FPGA. Quelques cas particuliers utiles sont discutés dans la partie 3.

1. Défis de réinitialisation asynchrone

Une fonction de réinitialisation est normalement incluse dans les conceptions VLSI numériques afin d'amener la logique à un état connu. La réinitialisation est principalement requise pour la logique de contrôle et peut être éliminée de la logique du chemin de données, réduisant ainsi la zone logique. La réinitialisation peut être synchrone ou asynchrone par rapport au signal d'horloge.

La réinitialisation synchrone nécessite une horloge active, entraîne une certaine latence liée au cycle d'horloge et peut avoir un impact sur la synchronisation des chemins de données. D'un autre côté, les réinitialisations synchrones sont déterministes et n'entraînent pas de métastabilité.

La réinitialisation asynchrone ne nécessite pas d'horloge active pour amener les bascules à un état connu, a une latence inférieure à une réinitialisation synchrone et peut exploiter des broches d'entrée de bascule spéciales qui n'affectent pas la synchronisation du chemin de données. Cependant, les réinitialisations asynchrones présentent un certain nombre d'inconvénients :

Ils peuvent provoquer une métastabilité dans les bascules, conduisant à un comportement non déterministe.

Les réinitialisations asynchrones doivent être rendues directement accessibles pour activer DFT.

Les réinitialisations asynchrones peuvent entraîner des problèmes de fiabilité dans les applications rad-hard, étant sensibles aux phénomènes de transitoires à événement unique (SET) [1].

Laissant de côté la discussion sur le meilleur type de réinitialisation [2], dans cet article, nous nous concentrons sur les problèmes et les solutions liés aux réinitialisations asynchrones. Certaines des techniques présentées dans cet article sont applicables aux réinitialisations asynchrones et synchrones.

Les réinitialisations asynchrones sont largement utilisées dans les conceptions numériques. Les pilotes typiques des réinitialisations asynchrones sont des ports externes, en fonction de l'état de l'alimentation (circuits RC, dispositifs de surveillance), des boutons de réinitialisation manuelle et des maîtres externes, tels que des microprocesseurs.

Dans de nombreux cas, les réinitialisations asynchrones peuvent être remplacées par des réinitialisations synchrones, mais il existe certaines situations dans lesquelles la fonctionnalité de réinitialisation asynchrone est obligatoire. Un exemple est une conception synchrone qui n'obtient aucune horloge active à la mise sous tension (l'horloge est soit instable soit fermée pour la réduction de puissance), mais nécessite un certain état connu pour ses interfaces externes. Un autre exemple est la conception à faible consommation d'énergie qui est requise pour minimiser l'alimentation pendant le processus de mise sous tension, sans horloge active.

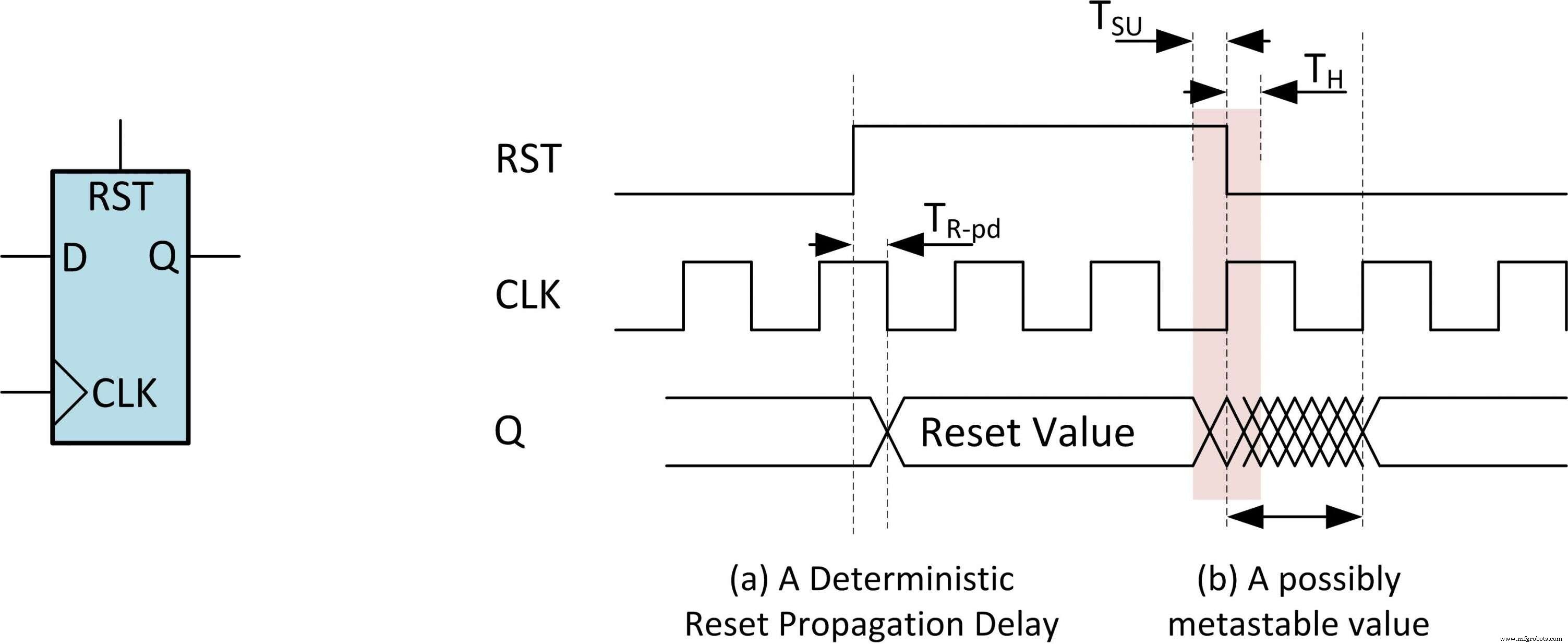

L'emploi de la réinitialisation asynchrone n'est pas simple. Bien que la synchronisation relative entre l'horloge et la réinitialisation puisse être ignorée pendant l'assertion de réinitialisation, la libération de réinitialisation doit être synchronisée avec l'horloge. Éviter la synchronisation de bord de libération de réinitialisation peut entraîner une métastabilité. En se référant à la figure 1, une réinitialisation asynchrone haute active est représentée. L'assertion de réinitialisation (a) affecte la sortie de bascule Q dans un temps déterministe délimité (délai de propagation, TR-pd ) et quel que soit le signal d'horloge CLK. Pendant la libération de réinitialisation (b), les conditions de synchronisation d'établissement et de maintien doivent être satisfaites pour le port RST par rapport au port d'horloge CLK. Une violation des conditions de configuration et de maintien du port RST (c'est-à-dire le temps de récupération et de suppression de réinitialisation) peut entraîner une métastable de la bascule, provoquant un échec de la conception en raison du passage à un état inconnu. Notez que cette situation est similaire à la violation des conditions de configuration et de maintien pour le port de données de la bascule, D.

cliquez pour agrandir l'image

Figure 1 : assertion et libération de réinitialisation asynchrone active élevée. (a) Une assertion de réinitialisation asynchrone (b) Une libération de réinitialisation asynchrone avec violation de synchronisation. (Source :Circuits vSync)

Embarqué

- Mises à jour en direct :cinq défis et solutions types

- Tendances et défis majeurs des PCB

- Anvo-Systems et Mouser signent un accord de distribution

- Swissbit :solutions de sécurité matérielles pour protéger les données et les appareils

- Rutronik et AP Memory signent un accord de distribution mondial

- Tendances et défis IIoT à surveiller

- Sécurité industrielle de l'IoT :défis et solutions

- Défis de la fabrication automobile et solutions IoT

- Cinq principaux défis et solutions logistiques pour l'industrie manufacturière