MOSFET Ge N-Channel avec diélectrique ZrO2 pour une mobilité améliorée

Résumé

nMOSFET Ge à haute mobilité avec ZrO2 diélectrique de grille sont démontrés et comparés à des transistors avec différentes propriétés interfaciales de l'ozone (O3 ) traitement, O3 post-traitement et sans O3 traitement. On constate qu'avec O3 traitement, les Ge nMOSFET avec ZrO2 diélectrique ayant un EOT de 0,83 nm obtenir une mobilité électronique effective maximale (μ eff ) de 682 cm 2 /Vs, qui est supérieur à celui de la mobilité universelle Si à densité de charge d'inversion moyenne (Q inv ). Par contre, le O3 post-traitement avec Al2 O3 couche interfaciale peut fournir considérablement amélioré-μ eff , atteignant environ 50 % μ eff amélioration par rapport à la mobilité universelle Si à moyen Q inv de 5 × 10 12 cm −2 . Ces résultats indiquent l'utilisation potentielle de ZrO2 diélectrique dans les nMOSFET Ge hautes performances.

Contexte

Le GERMANIUM (Ge) a présenté les avantages d'une mobilité plus élevée des porteurs et d'une température de traitement inférieure par rapport aux dispositifs Si. Ceux-ci font de Ge une alternative pour les applications de dispositifs logiques CMOS ultra-scalés et de transistors à couche mince (TFT) en tant que couche supérieure dans les circuits intégrés tridimensionnels [1,2,3]. Au cours des dernières années, de gros efforts ont été concentrés sur la passivation de surface, le diélectrique de grille et l'ingénierie des canaux pour les transistors à effet de champ métal-oxyde-semiconducteur à canal p (MOSFET), qui ont contribué à une amélioration significative des performances électriques pour le appareils à canal p.

Mais pour les MOSFET Ge à canal n, la faible mobilité effective des porteuses (μ eff ) causée par une mauvaise couche interfaciale de la pile de portes limite fortement les performances des appareils. Diverses techniques de passivation de surface, y compris la passivation Si [1], la post-oxydation plasma [4] et la passivation InAlP [5] et plusieurs diélectriques à κ élevé, notamment HfO2 , ZrO2 [6,7,8], Y2 O3 [9], et La2 O3 [10] ont été explorés dans les nMOSFET Ge pour stimuler l'électron μ eff . Il a été démontré que ZrO2 Le diélectrique intégré au canal Ge peut fournir une interface robuste grâce au fait qu'un GeO2 la couche interfaciale peut réagir et se mélanger avec le ZrO2 couche [7]. Un trou décent μ eff a été rapporté dans les transistors Ge à canal p [6,7,8], alors qu'il y a encore beaucoup de place pour l'amélioration des électrons μ eff pour leurs homologues.

Dans ce travail, Ge nMOSFETs avec ZrO2 les diélectriques de grille sont fabriqués pour obtenir une μ améliorée eff sur Si dans toute la plage de densité de charge d'inversion (Q inv ). Les transistors Ge obtiennent une amélioration de 50 % en électrons μ eff par rapport à la mobilité universelle Si à un Q moyen inv de 5.0 × 10 12 cm −2 .

Expérimental

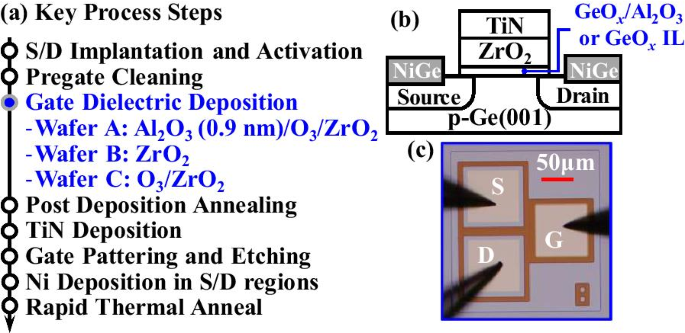

Les étapes clés du processus de fabrication des nMOSFET Ge sur des plaquettes p-Ge(001) de 4 pouces avec une résistivité de 0,136 à 0,182 Ω cm sont illustrées à la Fig. 1a. Les régions source/drain (S/D) ont été implantées avec de l'ion phosphore à une dose de 1 × 10 15 cm −2 et une énergie de 30 keV suivie d'un recuit d'activation du dopant à 600 °C. Après le nettoyage de pré-grille, les plaquettes de Ge ont été chargées dans une chambre de dépôt de couche atomique pour la formation de la ou des couches diélectriques de grille :Al2 O3 /O3 oxydation/ZrO2 , ZrO2 , ou O3 oxydation/ZrO2 pour les tranches A, B ou C, respectivement. Pour la plaquette A, 0,9 nm Al2 O3 a été utilisé pour protéger la surface du canal pendant O3 oxydation. O3 l'oxydation a été réalisée à 300 °C pendant 15 min pour les deux plaques A et C. Pour toutes les plaques, l'épaisseur de ZrO2 était d'environ 3,3 nm. Par la suite, le métal de grille TiN (100 nm) a été déposé par pulvérisation cathodique réactive physique, et une lithographie et une gravure ionique réactive ont été utilisées pour former l'électrode de grille. Après cela, une couche de Ni de 25 nm d'épaisseur a été déposée dans les régions S/D. Enfin, le recuit post-métallisation (PMA) à 350 °C pendant 30 s a été réalisé pour former le germanide de Ni et améliorer la qualité de l'interface. Des images schématiques et au microscope du transistor fabriqué sont illustrées respectivement aux figures 1b et c.

un Étapes clés du processus de fabrication des nMOSFET Ge. b Schéma en coupe et c image au microscope des dispositifs fabriqués

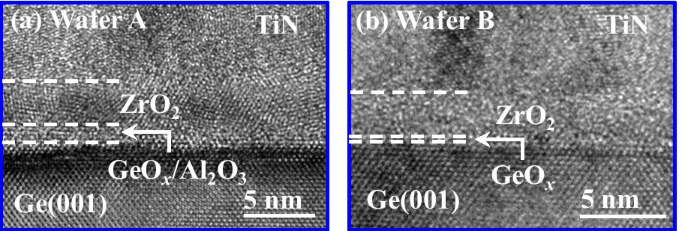

La figure 2a, b montre les images au microscope électronique à transmission à haute résolution (HRTEM) des empilements de grilles sur les plaquettes A et B, respectivement. L'épaisseur unifiée de l'Al2 O3 /GeOx la couche interfaciale (IL) pour la plaquette A est d'environ 1,2 nm, ce qui indique le GeO de 0,2 à 0,3 nmx . Pour le dispositif sur wafer B, un GeOx ultrafin L'IL a été démontré expérimentalement [7].

Images HRTEM de a TiN//ZrO2 /Al2 O3 /GeOx /Ge, b TiN/ZrO2 /GeOx /Ge stacks pour les appareils sur les tranches A et B, respectivement

Résultats et discussion

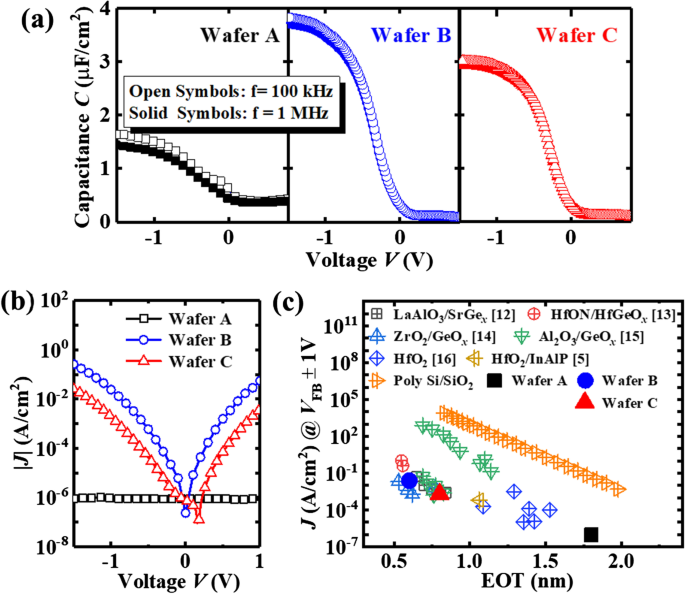

La capacité mesurée (C ) et le courant de fuite (J ) les caractéristiques des condensateurs Ge MOS sur les plaquettes A, B et C sont mesurées et illustrées sur les Fig. 3a, b, respectivement. L'épaisseur d'oxyde équivalente (EOT) des dispositifs sur les plaquettes A, B et C est extraite à 1,79, 0,59 et 0,83 nm, respectivement. En supposant le GeOx IL fournit un EOT supplémentaire de ~ 0,25 nm pour les plaquettes A et C en comparant les plaquettes B et C, le 3,3 nm ZrO2 contribue à un EOT de ~ 0,6 nm avec une valeur de ~ 21,8, ce qui est cohérent avec la valeur rapportée précédente de ZrO2 amorphe [11].Ces résultats dérivés confirment également que l'épaisseur en GeOx IL sur la plaquette B est négligeable.

un Mesuré C en fonction de la tension V caractéristiques des condensateurs Ge pMOS sur les tranches A, B et C. b J contre V courbes pour les appareils. c Analyse comparative de J (extrait à V FB ± 1 V) des condensateurs Ge MOS dans ce travail par rapport aux données obtenues pour des conditions de polarisation similaires dans la littérature

Le GeOx /Al2 O3 IL pour wafer A et GeOx IL pour la plaquette C produit l'EOT de ~ 1,2 et ~ 0,25 nm, respectivement. L'EOT des dispositifs peut être encore réduit en diminuant l'épaisseur de l'IL ou en améliorant la qualité de l'interface et en améliorant la permittivité de ZrO2 avec une passivation de surface, par exemple NH3 /H2 traitement plasmatique [6]. La figure 3c compare J par rapport aux caractéristiques EOT pour les nMOSFET Ge dans ce travail par rapport aux valeurs d'autres dispositifs Ge rapportés [5, 12, 13, 14, 15, 16, 17]. Il est également observé que les résultats sont cohérents avec le Ge MOS rapporté avec EOT ultra-mince suivant les mêmes tendances, indiquant que la différence de courant de fuite illustrée sur la figure 3b devrait être principalement attribuable à la différence d'EOT.

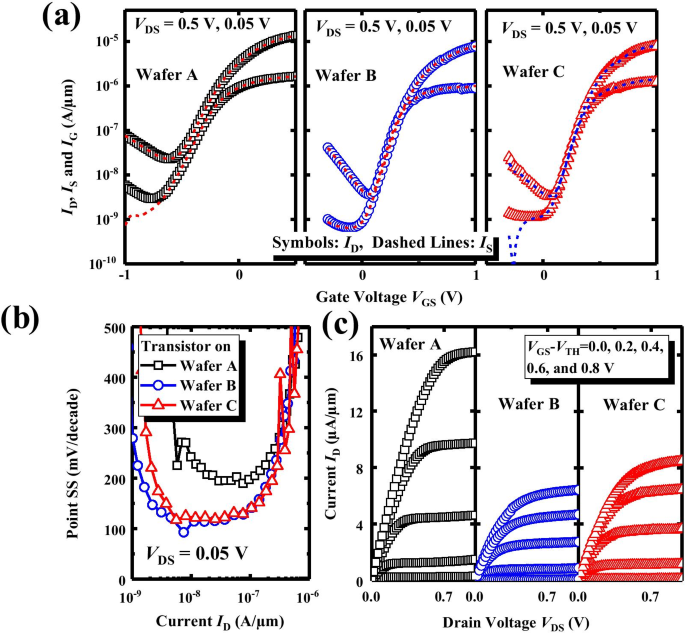

La figure 4a montre le courant de drain mesuré (I D ) et le courant source (I S ) en fonction de la tension de grille (V G ) courbes des nMOSFET Ge des tranches A, B et C. Tous les transistors ont une longueur de grille L G de 4 μm et une largeur de porte W de 100 μm. Le point d'oscillation sous le seuil (SS), défini comme dV G /d(logI D ), en fonction de I D Les courbes des transistors de la figure 4a sont calculées et illustrées sur la figure 4b. Il est précisé que le transistor sur la plaquette A présente le dégradé I D plancher de fuite et SS par rapport aux dispositifs sur les plaquettes B et C. Outre l'augmentation de l'EOT dans les dispositifs sur la plaquette A entraînerait l'incrément de SS, ces phénomènes devraient être en partie attribués au fait que le dispositif avec le Al 2 O3 couche insérée a une densité plus élevée de pièges d'interface (D il ) dans la bande interdite du canal Ge par rapport aux tranches B et C.

un Mesuré I D et Je S contre V GS courbes de Ge nMOSFET sur les tranches A, B et C. b Point SS en fonction de I D pour les transistors. c Je D –V D les caractéristiques montrent que le Ge nMOSFET sur la plaquette A a un courant de commande plus élevé que les dispositifs sur les plaquettes B et C

La figure 4c montre les caractéristiques de sortie mesurées, c'est-à-dire I D –V D courbes pour différentes valeurs d'overdrive de grille |V G –V TH | des dispositifs démontrant que le transistor Ge sur la plaquette A atteint un courant d'entraînement considérablement amélioré par rapport aux dispositifs sur les plaquettes B et C. Ici, V TH est défini comme V GS correspondant à un I D de 10 -7 A/μm. Compte tenu des conditions identiques pour la formation de S/D, le I boosté DS pour les transistors sur la plaquette A indique le μ le plus élevé eff [18,19,20,21]. L'Al2 O3 couche n'a pas conduit à la dégradation de D il performances proches de la bande de conduction du canal Ge.

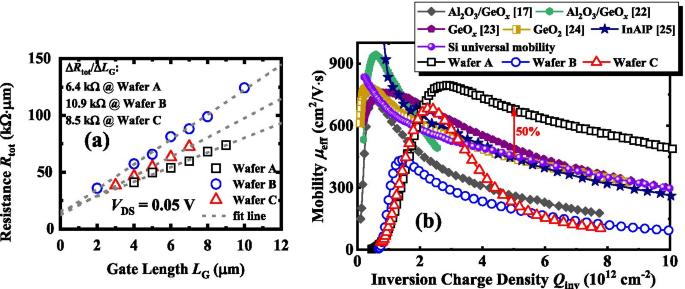

La figure 5a montre la résistance totale R tot en fonction de L G pour les nMOSFET Ge avec ZrO2 diélectrique avec un L G allant de 2 à 10 µm. Les valeurs de R tot sont extraits à une surmultiplication de grille de 0,6 V et un V D de 0,05 V. La résistance S/D R SD des transistors est extrait pour être ~ 13,5 kΩ μm, en utilisant les lignes ajustées se coupant au y -axe. Le similaire R SD est cohérent avec le processus identique de formation de PMA et de S/D. La résistance du canal R CH les valeurs des appareils sont obtenues par la pente des droites ajustées, c'est-à-dire ΔR tot /ΔL G , qui peut être utilisé pour calculer le μ eff caractéristiques des nMOSFET Ge. Pour évaluer la qualité de l'interface, les densités de pièges d'interface (D il ) ont été extraits par l'équation suivante selon la méthode de Hill [17] :

$$D_{{{\text{it}}}} =\frac{{2G_{{{\text{m}}\max }} /\omega }}{{qA\left[ {\left( {\ frac{{G_{{{\text{mmax}}}} }}{{\omega C_{{{\text{ox}}}} }}} \right) + \left( {1 - C_{{\ text{m}}} /C_{{{\text{ox}}}} } \right)^{2} } \right]}}$$où q est la charge électronique, A est l'aire du condensateur, G m,max est la valeur maximale de la conductance mesurée, avec sa capacité correspondante C m , ω est la fréquence angulaire, et C bœuf est la capacité d'oxyde de grille. Le D il les valeurs sont calculées pour être 3,7, 3,2 et 2,3 × 10 12 eV −1 cm −2 pour les appareils sur les tranches A, B et C, respectivement.

On sait que les valeurs calculées correspondent au midgap D il . L'appareil avec Al2 O3 IL sur la plaquette A a un midgap D plus élevé il par rapport aux dispositifs sur les tranches B et C. Ceci est cohérent avec les résultats des Figs. 3a et 4a, et le midgap supérieur D il donne lieu à une plus grande dispersion de capacité d'appauvrissement dans la plaquette A provoquant un courant de fuite plus élevé de I DS en comparaison avec les deux autres tranches. Notez que la plaquette A doit avoir le D inférieur il près de la bande interdite de conduction en raison de son μ plus élevé eff sur les plaquettes B et C.

un R tot contre L G courbes pour les nMOSFET Ge sur les plaquettes A, B et C. La ligne d'ajustement se coupant à l'axe des y et la pente des lignes d'ajustement linéaires sont utilisées pour extraire le R SD et R CH , respectivement. b μ eff pour les nMOSFET Ge dans ce travail par rapport aux résultats publiés précédemment pour les transistors Ge non contraints. Les appareils sur la plaquette A montrent l'amélioration μ eff que la mobilité universelle Si dans toute la gamme de Q inv

Il est bien connu que μ eff est le goulot d'étranglement pour le courant d'entraînement élevé et la transconductance dans les nMOSFET Ge. Ici, μ eff peut être calculé par \(\mu_{{{\text{eff}}}} =1/[WQ_{{{\text{inv}}}} (\Delta R_{{{\text{tot}}}} /\Delta L_{{\text{G}}} )]\), où ΔR tot /ΔL G est la pente du R tot contre L G comme le montre la figure 5a. Q inv peut être obtenu en intégrant le C mesuré inv –V G courbes. Dans la Fig. 5b, nous comparons le μ eff contre Q inv des nMOSFET Ge sur les plaquettes A, B et C avec ceux rapportés précédemment dans [18, 22, 23, 24, 25]. Le pic extrait μ eff les valeurs des transistors sur les tranches A et C sont de 795 et 682 cm 2 /V s, respectivement, et celui des nMOSFET Ge sur la plaquette B est de 433 cm 2 /Vs. Générer des MOSFET avec Al2 O3 IL obtient un μ considérablement amélioré eff en comparaison avec les transistors sur la plaquette B ou C, les dispositifs en [18, 22, 23, 24, 25] dans un champ élevé, et la mobilité universelle Si dans l'ensemble du Q inv intervalle. À un Q inv de 5 × 10 12 cm −2 , 50 % μ eff l'amélioration est obtenue dans les dispositifs sur la plaquette A par rapport à la mobilité universelle Si. Cela démontre qu'en protégeant la surface du canal pour empêcher le mélange de ZrO2 et GeOx en utilisant Al2 O3 , une interface de haute qualité entre l'isolant de grille et Ge est réalisée pour augmenter les caractéristiques de mobilité, ce qui est également rapporté dans les études précédentes des MOSFET Ge avec EOT ultramince [26]. μ eff dans les transistors sur la plaquette C est plus élevé que le Si universel à un Q inv de 2,5 × 10 12 cm −2 , bien qu'il décroisse rapidement avec l'augmentation de Q inv intervalle. Cela indique que le O3 utilisé oxydation avant ZrO2 le dépôt améliorerait la qualité interfaciale dans une certaine mesure; cependant, cela ne conduit pas à une surface de canal suffisamment plate pour supprimer efficacement la diffusion de la rugosité de surface du support à un Q élevé inv en raison du mélange de ZrO2 et GeOx , car il est rapporté que la génération de lacunes d'oxygène pendant le mélange augmenterait la rugosité de l'ordre à courte distance (SRO) [27]. Optimiser le O3 processus d'oxydation ou de réduction de l'Al2 O3 L'épaisseur IL peut permettre au transistor Ge d'atteindre un EOT réduit tout en maintenant un μ plus élevé eff au Q élevé inv .

Conclusions

Les impacts de la structure diélectrique de grille et de la morphologie sur les caractéristiques électriques du Ge nMOSFET sont étudiés. Un Al2 O3 /ZrO2 le diélectrique de grille permet d'améliorer considérablement μ eff par rapport à la mobilité universelle Si. μ eff peut être amélioré en insérant un Al2 O3 couche entre le ZrO2 et le canal Ge, qui, cependant, conduit inévitablement à un EOT plus important. Al2 O3 -Ge nMOSFETs libres avec O3 oxydation de la surface Ge avant ZrO2 le dépôt atteint un pic μ eff de 682 cm 2 /V s qui est supérieur à celui de Si au Q similaire inv .

Disponibilité des données et des matériaux

Les ensembles de données soutenant les conclusions de cet article sont inclus dans l'article.

Abréviations

- Voir :

-

Germanium

- ZrO2 :

-

Dioxyde de zirconium

- Al2 O3 :

-

Oxyde d'aluminium

- O3 :

-

Ozone

- Si :

-

Silicium

- PMA :

-

Recuit post-métal

- PDA :

-

Recuit post-dépôt

- IL :

-

Couche interfaciale

- TiN :

-

Nitrure de titane

- MOSFET :

-

Transistors à effet de champ métal-oxyde-semiconducteur

- ALD :

-

Dépôt de couche atomique

- HF :

-

Acide fluorhydrique

- µ eff :

-

Mobilité efficace des transporteurs

- OPP :

-

Post-oxydation plasmatique

- SS :

-

Balançoire sous le seuil

- HEC :

-

Epaisseur équivalente à la capacité

- EOT :

-

Épaisseur d'oxyde équivalente

- Qinv :

-

Densité de charge d'inversion

- HRTEM :

-

Microscope électronique à transmission haute résolution

- Non :

-

Nickel

- GeOx :

-

Oxyde de Germanium

- Je DS :

-

Courant de vidange

- V GS :

-

Tension de grille

- V TH :

-

Tension de seuil

Nanomatériaux

- Atteindre la durabilité avec les teintures et les pigments

- KUHMUTE repense la mobilité avec l'impression 3D SLS

- Contrôle complet de la polarisation térahertz avec bande passante élargie via des métasurfaces diélectriques

- Mémoire résistive ZrO2/ZrO2 − x /ZrO2 sans conformité avec comportement de commutation multi-états interfacial contrôlable

- Mécanisme de conduction et endurance améliorée dans la RRAM à base de HfO2 avec traitement de nitruration

- Amélioration diélectrique des condensateurs MIM Al2O3/ZrO2/Al2O3 déposés par couche atomique par recuit par micro-ondes

- 6 façons d'améliorer Protocase Designer avec la version 4.6

- Obtenir une finition phénoménale avec la métallisation

- Résistance à l'usure améliorée avec les électrodes en cuivre et tungstène