Dispositif LVTSCR robuste et insensible au verrouillage avec un PMOSFET intégré pour la protection contre les décharges électrostatiques dans un processus CMOS 28 nm

Résumé

Le redresseur au silicium à déclenchement basse tension (LVTSCR) devrait fournir une protection contre les décharges électrostatiques (ESD) pour un circuit intégré basse tension. Cependant, il est normalement vulnérable à l'effet de verrouillage en raison de sa tension de maintien extrêmement faible. Dans cet article, un nouveau LVTSCR intégré avec un MOSFET de type p supplémentaire appelé EP-LVTSCR a été proposé et vérifié dans une technologie CMOS 28 nm. Le dispositif proposé possède une tension de déclenchement inférieure de ~ 6,2 V et une tension de maintien nettement plus élevée de ~ 5,5 V avec seulement 23 % de dégradation du courant de défaillance sous le test d'impulsion de la ligne de transmission. Il est également démontré que l'EP-LVTSCR fonctionne avec une résistance d'activation inférieure de ~ 1,8 Ω ainsi qu'un courant de fuite fiable de ~ 1,8 nA mesuré à 3,63 V, ce qui le rend adapté aux protections ESD en CMOS 2,5 V/3,3 V processus. De plus, le mécanisme de déclenchement et les caractéristiques de conduction du dispositif proposé ont été explorés et démontrés avec la simulation TCAD.

Contexte

Avec la miniaturisation continue de la taille des caractéristiques des dispositifs semi-conducteurs, les dommages induits par les décharges électrostatiques (ESD) dans les circuits intégrés (CI) sont devenus un problème plus sérieux. De plus, le coût de fabrication du dispositif de protection ESD a été fortement augmenté en raison de la technologie de processus avancée [1]. Par conséquent, les conceptions de dispositifs de protection ESD à haute efficacité et robustesse sont d'une grande valeur.

Il a été vérifié qu'un dispositif de redressement contrôlé au silicium (SCR) supporte un courant ESD élevé avec une petite dimension de dispositif en raison de l'effet de rétroaction fortement positif dans ses transistors à jonction bipolaire parasites [2]. Mais le SCR a généralement une tension de déclenchement élevée (V t1 ) qui dépasse la tension de claquage de l'oxyde de grille de l'étage d'entrée en technologie CMOS nanométrique. Pour réduire le V t1 de SCR, le SCR latéral modifié (MLSCR) a été signalé pour la protection ESD d'entrée en insérant des n + fortement dopés ou p + régions à travers la frontière des puits n et p [3, 4]. Mais la tension de déclenchement du MLSCR est toujours supérieure aux tensions de claquage des transistors de sortie dans le tampon de sortie CMOS. Par conséquent, il ne peut pas fournir à lui seul une protection ESD de sortie efficace.

Pour protéger efficacement le tampon de sortie CMOS, un SCR déclenché à basse tension (LVTSCR) a été proposé en insérant un dispositif NMOS à canal court (PMOS) dans le SCR traditionnel pour obtenir une tension de déclenchement beaucoup plus faible [5,6,7] , ce qui équivaut à la tension de déclenchement du snapback du dispositif NMOS (PMOS) inséré. Cependant, comme les dispositifs SCR et MLSCR traditionnels, le LVTSCR souffre également des risques de verrouillage en raison de sa tension de maintien extrêmement faible (Vh ) d'environ 2 V [8]. Un tel effet de verrouillage entraînera un dysfonctionnement pendant le fonctionnement normal et un courant élevé incessant pour détruire le CI [9].

Il existe plusieurs méthodes possibles pour améliorer le V h du LVTSCR [10,11,12,13,14,15]. La solution la plus courante consiste à étendre la région de base des transistors à jonction bipolaire parasite (BJT) du SCR pour diminuer l'efficacité d'injection de leurs jonctions émetteur-base [10]. En adoptant cette solution, non seulement la zone de disposition de l'appareil augmentera, mais la résistance à l'allumage (R sur ) devrait également conduire à une dégradation drastique de son courant de défaillance (I t2 ). Ensuite, une méthode optimisée a été proposée en insérant une région flottante n-puits dans LVTSCR avec moins de sacrifice sur I t2 [11], mais il fonctionne également avec un grand R sur conduisant une tension de conduction exorbitante qui dépasse la tension de claquage de l'oxyde de grille contre un faible courant, réduisant ainsi son courant de protection ESD efficace. La méthode en ajoutant les couches supplémentaires N-LDD/P-HALO dans LVTSCR peut également élever le V h [12], alors que de tels dispositifs ne sont compatibles que pour le processus spécifique et ne peuvent pas être largement utilisés dans les processus CMOS ordinaires. De plus, un LVTSCR déclenché par NMOS gate-to-ground (GGSCR) a été signalé dans [13], ce qui augmente le V h en conduisant le drain du NMOS intégré à l'anode, mais cela pourrait endommager le NMOS intégré avant la conduction SCR dans un courant faible. Récemment, les structures composées LVTSCR ayant un faible V t1 ainsi qu'un V élevé h ont été démontrés dans [14, 15]. Ces structures composées sont conçues avec des exigences de complexité et de surface élevées, limitant ainsi leur application dans la technologie CMOS avancée compte tenu des coûts de conception. Par conséquent, un dispositif de protection ESD robuste, efficace dans la zone et immunisé contre le verrouillage est hautement souhaitable dans la protection ESD de processus avancé.

Dans cet article, une nouvelle structure LVTSCR avec un transistor PMOS intégré (EP-LVTSCR) est proposée pour les applications de tension d'alimentation 2,5 V/3,3 V. Le dispositif proposé a été fabriqué dans un processus CMOS 28 nm, et sa caractéristique électrique est vérifiée par la mesure de l'impulsion de ligne de transmission (TLP). Les mécanismes physiques du dispositif proposé sont explorés par des simulations technologiques de conception assistée par ordinateur (TCAD). En conséquence, la structure proposée possède une tension de maintien plus élevée, une tension de déclenchement plus faible avec un R plus faible sur , et juste une légère diminution de I t2 sans aucune étape de processus supplémentaire.

Méthodes

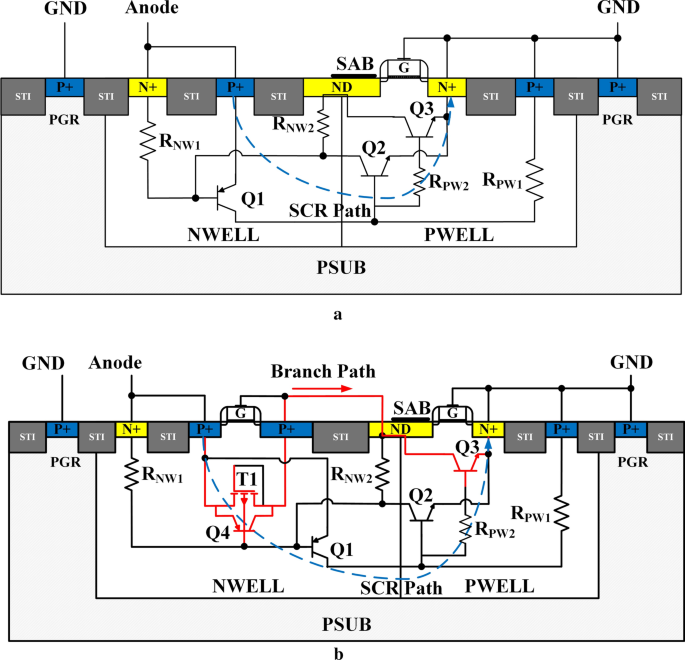

Le LVTSCR conventionnel et le EP-LVTSCR proposé ont été étudiés dans cet article. Les vues schématiques en coupe transversale des LVTSCR et EP-LVTSCR conventionnels sont illustrées respectivement aux figures 1a, b, tandis que leurs circuits équivalents sont représentés dans les structures avec les transistors parasites et les résistances de puits. Dans les deux dispositifs, des couches de blocs de siliciure (SAB) sont placées au sommet de la région ND partielle, ce qui induira des résistances de ballast en empêchant la formation de couches de siliciure [16, 17]. Dans le LVTSCR conventionnel, un transistor NMOS est inséré dans PWELL avec son réglage de drain (ND) entre NWELL et PWELL, tandis que sa source et sa grille sont connectées à la terre (GND) ensemble, comme on peut le voir sur la Fig. 1a. Pendant le stress ESD, le BJT latéral parasite p-n-p (Q1) et les BJT latéraux parasites n-p-n (Q2 et Q3) seront progressivement activés. Dans une telle condition, les transistors Q1 et Q2 sont couplés pour constituer le chemin de conduction SCR qui prédominera la décharge de courant, où le chemin de conduction SCR est indiqué par la ligne pointillée.

Vue en coupe de a le LVTSCR conventionnel et b le projet EP-LVTSCR

Par rapport au LVTSCR conventionnel, l'EP-LVTSCR possède un transistor PMOS supplémentaire (T1) intégré dans le NWELL car sa grille et son drain sont connectés à ND avec un métal, comme illustré à la Fig. 1b. Lorsqu'une impulsion ESD est appliquée à l'anode de l'EP-LVTSCR, la diode N+/NWELL/N+/PWELL/P+ polarisée en inverse conduira en premier si la tension de zapping est supérieure à la tension de claquage N+/PWELL. Ensuite, les trous/électrons générés par l'effet multiplicateur d'avalanche s'écouleront vers la cathode/anode, augmentant ainsi la densité de courant dans NWELL/PWELL, et élèveront davantage le potentiel de chute à travers le NWELL/PWELL. Une fois la chute de tension totale sur R NW1 et R NW2 , ce qui équivaut à la chute de tension entre la source et la grille (− V gs ) de T1, dépasse sa tension de seuil (V ème ) d'environ 0,9 V, le T1 s'allumera. Par la suite, les transistors latéraux parasites n–p–n Q2 et Q3 seront déclenchés en fonction de la conduction de leurs jonctions émetteur-base. On remarque que la conduction de T1 fera baisser le R sur à travers NWELL, et donc les Q2 et Q3 peuvent être déclenchés à des tensions plus basses. Alors que le courant continue d'augmenter, la tension chute sur R NW1 monte à environ 0,7 V et active le transistor Q1 et le transistor p–n–p latéral parasite du PMOS (Q4). Enfin, le chemin SCR s'active contre le chemin de dérivation conducteur.

Plusieurs rapports ont démontré que la tension de maintien du SCR est principalement déterminée par la différence de potentiel dans la région d'appauvrissement NWELL/PWELL V départ [18,19,20], qui est inversement proportionnel aux porteurs minoritaires (électrons/trous) injectés dans la région de déplétion. Alors que le chemin de dérivation de l'EP-LVTSCR peut extraire les trous/électrons injectés dans la région d'appauvrissement à partir du chemin SCR, élevant ainsi le V h de EP-LVTSCR.

Afin de démontrer davantage le mécanisme physique de l'EP-LVTSCR, une simulation TCAD a été réalisée, où les modèles physiques tels que la mobilité, la recombinaison, la thermodynamique et la densité intrinsèque effective ont été intégrés et les méthodes mathématiques telles que l'extrapolation, RelErrcontrol et le courant continu calcul ont été utilisés. La modélisation du courant ESD par des impulsions de 1,2 A avec un temps de montée de 10 ns a été appliquée aux anodes de l'EP-LVTSCR et du LVTSCR conventionnel, respectivement, où le substrat des dispositifs était considéré comme le seul dissipateur thermique et la température ambiante était fixée à 300 K.

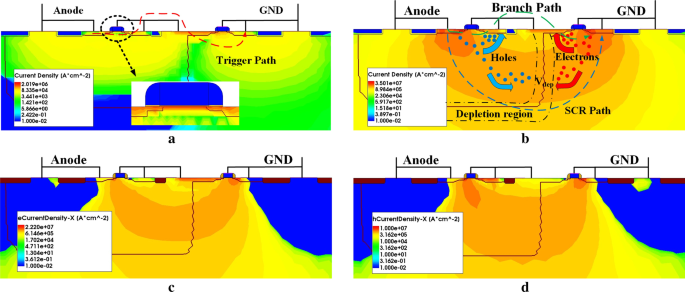

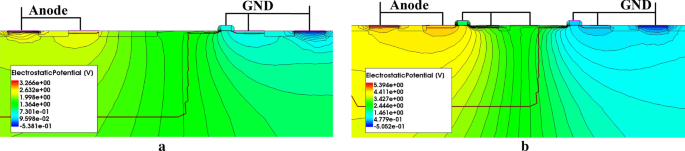

Les résultats simulés des distributions totales de densité de courant d'EP-LVTSCR à 500 ps et 5 ns sont présentés sur les figures 2a, b, respectivement. À 500 ps, la distribution de densité de courant se concentre sur les transistors T1 et Q2, ce qui indique que la série T1/Q2 s'est allumée en tant que chemin de déclenchement illustré à la Fig. 2a. Lorsque le temps atteint 5 ns, le chemin SCR et le chemin de dérivation ont tous deux conduit comme on peut le voir sur la figure 2b. À ce moment, une partie des trous/électrons générés par P+/N+ sont extraits de NWELL/PWELL pour traverser le chemin de dérivation, qui sont illustrés par les trous horizontaux et la densité de courant d'électrons de la structure proposée illustrée à la Fig. 2c, d . De plus, les distributions de potentiel électrostatique du LVTSCR conventionnel et du EP-LVTSCR à 5 ns sont comparées sur les Fig. 3a, b. De toute évidence, le pic potentiel à l'intérieur de l'EP-LVTSCR est plus élevé. Ces résultats de simulation fournissent une preuve directe de l'hypothèse ci-dessus de la tension de maintien plus élevée de l'EP-LVTSCR résultant du chemin de dérivation indiqué sur la figure 1b.

a simulé par TCAD distribution de la densité de courant totale à t = 500 ps, b distribution de la densité de courant totale à 5 ns, c distribution horizontale de densité de courant d'électrons à 5 ns et d distribution de la densité de courant des trous horizontaux à 5 ns de l'EP-LVTSCR proposé sous une contrainte de 1,2 A-TLP

Distributions de potentiel électrostatique simulées par TCAD de a le projet EP-LVTSCR et b le LVTSCR conventionnel à t = 5 ns sous une contrainte 1.2A-TLP

Résultats et discussion

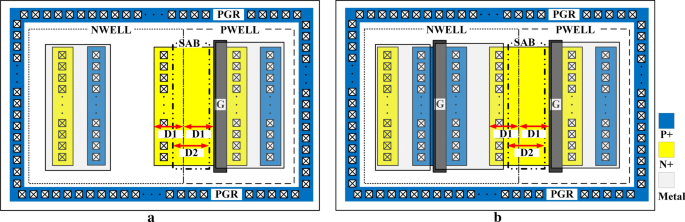

Le LVTSCR et l'EP-LVTSCR conventionnels sont mis en œuvre dans un processus CMOS logique de 28 nm 2,5 V/3,3 V avec la même largeur de 40 um, et leurs topologies de disposition sont illustrées sur les figures 4a, b, respectivement. Pour éviter les effets parasites associés au substrat, des anneaux de garde de type P (PGR) sont utilisés dans les deux structures, et chaque PGR est connecté à GND [21]. L'axe central de ND est aligné avec la jonction NWELL/PWELL, et le paramètre D1 est utilisé pour décrire la moitié de la longueur ND, tandis que D2 est la longueur de la région SAB.

Topologies de disposition de a le LVTSCR conventionnel et b le projet EP-LVTSCR

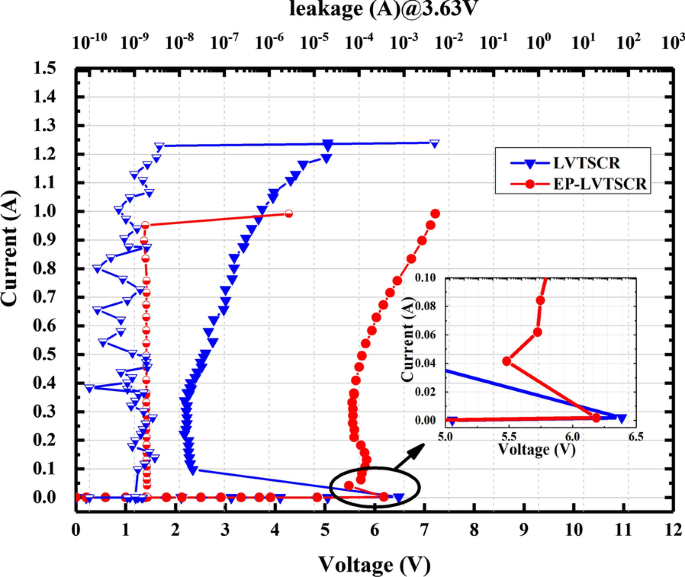

Les caractéristiques ESD des LVTSCR et EP-LVTSCR conventionnels ont été mesurées à l'aide du testeur Hanwa TED-T5000 TLP avec un temps de montée de 10 ns et une largeur d'impulsion de 100 ns, et les courants de fuite ont été mesurés sous 3,63 V (1,1 * VDD) de polarisation de tension continue après chaque TLP stress. Le TLP I–V mesuré et les caractéristiques de fuite de l'EP-LVTSCR et du LVTSCR sont illustrés à la Fig. 5. Apparemment, l'EP-LVTSCR possède un V plus élevé h de 5,49 V par rapport au LVTSCR conventionnel de 2,18 V. Bien que l'EP-LVTSCR présente une amélioration significative de la tension de maintien, son I t2 vient de diminuer d'environ 0,29 A, ce qui profite de l'assistant du chemin de courant de dérivation. Par ailleurs, EP-LVTSCR effectue également un V t1 diminuant de 6,49 à 6,18 V. Pour les broches d'E/S 2,5 V ou 3,3 V dans les processus CMOS 28 nm, la fenêtre de conception ESD variait de 3,63 à 9,4 V avec une marge de sécurité de 10 %. Par conséquent, l'EP-LVTSCR proposé peut être utilisé comme une solution de protection ESD valide pour les ports IO 2,5 V/3,3 V en surmontant le problème de verrouillage dans une structure traditionnelle de type LVTSCR.

TLP I–V mesuré et courants de fuite de l'EP-LVTSCR et du LVTSCR conventionnel avec la même surface de puce

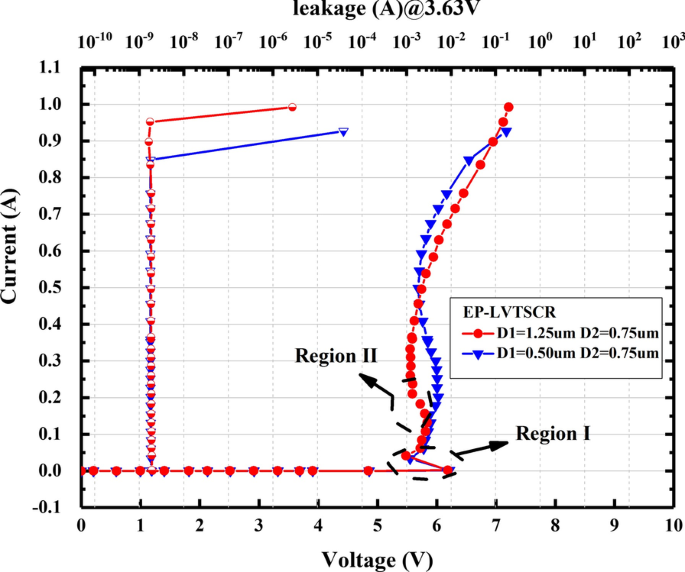

Dans cet article, les caractéristiques électriques de la protection ESD proposée ont été optimisées en modifiant les variables de conception D1 et D2. La figure 6 illustre les résultats de mesure TLP des EP-LVTSCR avec deux D1 différents. Il est à noter que les courbes I-V des EP-LVTSCR montrent deux régions de snapback en raison des effets de déclenchement multiple lors de la mise sous tension des appareils. La première région de snapback I suggère la conduction du chemin de déclenchement qui est indiqué sur la figure 2a, tandis que le deuxième snapback de la région II est induit par l'activation du chemin SCR. Lorsque D1 passe de 1,25 à 0,5 um, le I t2 diminue d'environ 0,1 A et le courant de maintien dans le deuxième snapback augmente d'environ 0,17 A. Cela est dû au fait que les résistances de puits R NW2 et R PW2 (Fig. 1) sont diminués avec la diminution de D1, ce qui nécessite plus de courant pour déclencher et maintenir la conduction du SCR.

TLP I–V mesuré et courants de fuite de EP-LVTSCR avec deux D1 différents

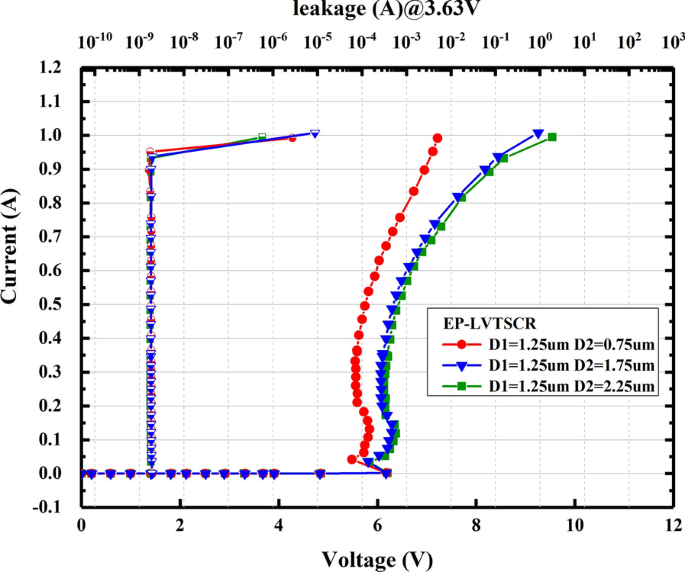

La figure 7 montre les résultats TLP I–V de l'EP-LVTSCR avec trois D2 différents. Lorsque D2 passe de 0,75 à 2,25 µm, la résistance de ballast de ND augmente progressivement, ce qui entraîne une augmentation de la résistance du chemin de dérivation et un élargissement supplémentaire de R sur , ce qui peut être observé par les variations de pente des courbes caractéristiques IV de la Fig. 7. Par conséquent, le V h s'élève de 5,5 à 5,8 V avec l'augmentation de D2 et sans changements significatifs dans It2 .

TLP I–V mesuré et courants de fuite de EP-LVTSCR avec trois D2 différents

Conclusions

Un dispositif ESD amélioré appelé EP-LVTSCR a été conçu et fabriqué dans une technologie CMOS 28 nm. Les mécanismes des dispositifs proposés ont également été démontrés avec des simulations TCAD. Par rapport au LVTSCR conventionnel, l'EP-LVTSCR proposé possède une tension de déclenchement inférieure de 6,2 V et une tension de maintien nettement plus élevée de 5,5 V en raison de son mécanisme de déclenchement amélioré et de son effet de conduction de dérivation. Avec une telle augmentation de V h , le courant de défaillance de l'EP-LVTSCR n'a diminué que d'environ 20 %. En outre, la structure proposée fonctionne avec une résistance d'activation inférieure ainsi qu'un courant de fuite fiable d'environ 2 nA à une tension de 3,63 V, elle est donc parfaitement applicable pour la protection des broches d'E/S 2,5 V/3,3 V. En outre, les EP-LVTSCR devraient également fournir une protection ESD sur les circuits d'alimentation 5 V tout en bénéficiant de leurs caractéristiques de tension de maintien réglables.

Disponibilité des données et des matériaux

Toutes les données générées ou analysées au cours de cette étude sont incluses dans cet article publié.

Abréviations

- ESD :

-

Décharge électrostatique

- SCR :

-

Redresseur au silicium

- MLSCR :

-

SCR latéral modifié

- LVTSCR :

-

SCR à déclenchement basse tension

- CMOS :

-

Semi-conducteur à oxyde métallique complémentaire

- IC :

-

Circuits intégrés

- V t1 :

-

Tension de déclenchement

- V h :

-

Tension de maintien

- BJT :

-

Transistors bipolaires à jonction

- R sur :

-

Résistance à l'allumage

- Je t2 :

-

Courant de panne

- TLP :

-

Impulsion de ligne de transmission

- TCAD :

-

Technologie conception assistée par ordinateur

- SAB :

-

Bloc de siliciure

- V ème :

-

Tension de seuil

- DC :

-

Courant continu

Nanomatériaux

- Mémoire sur la technologie des circuits intégrés pour les microcontrôleurs et les systèmes embarqués

- Maxim :double émetteur-récepteur IO-Link avec régulateur DC-DC et protection contre les surtensions

- Conception embarquée avec FPGA :processus de développement

- TRS-STAR :systèmes embarqués robustes et sans ventilateur d'avalue

- Ingénierie des procédés de revêtement par immersion et optimisation des performances pour les appareils électrochromes à trois états

- Une RRAM SRAM 4T intégrée avec charge de commutation résistive à auto-inhibition par un processus logique CMOS pur

- Une nouvelle microstructure d'amas de nanocônes avec des propriétés antireflet et superhydrophobes pour les dispositifs photovoltaïques

- Automatisation et cybersécurité :protection complète pour les clients

- Matériaux et conception de PCB pour haute tension