Nouveau thyristor à haute tension de maintien avec structure de recombinaison de porteuse intégrée pour une immunité au verrouillage et une protection ESD robuste

Résumé

Un nouveau redresseur commandé au silicium à haute tension de maintien compatible avec le processus CMOS (HHV-SCR) pour la protection contre les décharges électrostatiques (ESD) est proposé et démontré par simulation et test d'impulsion de ligne de transmission (TLP). La région de recombinaison de trous (ou d'électrons) nouvellement introduite H-RR (ou E-RR) non seulement recombine le porteur minoritaire dans la base de transistor PNP (ou NPN) parasite par la couche N+ (ou P+), mais fournit la recombinaison supplémentaire pour éliminer le porteurs d'avalanche de surface par couche P+ (ou N+) nouvellement ajoutée dans H-RR (ou E-RR), ce qui entraîne une nouvelle amélioration de la tension de maintien (V h ). Par rapport au V mesuré h de 1,8 V de redresseur commandé au silicium déclenché à basse tension (LVTSCR), le V h du HHV-SCR peut être augmenté à 8,1 V tout en maintenant un courant de défaillance suffisamment élevé (I t2> 2,6 A). Une amélioration de plus de quatre fois la figure du mérite (FOM) est obtenue.

Introduction

Avec le développement de la technologie intégrée des semi-conducteurs et la miniaturisation cohérente de la taille des fonctionnalités des dispositifs semi-conducteurs, les dommages aux dispositifs induits par les décharges électrostatiques deviennent de plus en plus graves. Au prix d'une grande surface de puce, les dispositifs conventionnels tels que les MOSFET à canal N à diode et à grille (ggNMOS) présentant une robustesse ESD normale ont été signalés [1]. Afin de réaliser une capacité ESD améliorée avec une dimension de dispositif plus petite, le redresseur commandé au silicium déclenché à basse tension (LVTSCR) a été considéré comme un dispositif attrayant en raison de sa capacité de courant élevé par unité de surface [2]. Pour les applications basse tension, grâce à la tension de déclenchement basse intégrée (V t1 ) ggNMOS, le LVTSCR avec une excellente robustesse ESD est capable de fournir une vitesse de réponse ESD plus rapide que celle obtenue avec un SCR conventionnel. Cependant, la forte rétroaction positive inhérente entraîne un V extrêmement faible h (1~2 V), qui est responsable du latch-up et des erreurs de déclenchement transitoires [3]. De tels effets négatifs peuvent être efficacement supprimés en augmentant simplement V h [3,4,5,6,7,8,9,10,11]. L'appareil sera exempt du verrouillage et des erreurs de déclenchement transitoires, tandis que le V h est supérieure à la tension d'alimentation (VDD). En conséquence, la région N+ESD et la région P+LDD ont été ajoutées au SCR avec des masques supplémentaires et des étapes d'implantation ionique pour améliorer V h [3]. Cependant, la robustesse ESD peut se détériorer en raison de la dissipation de puissance supplémentaire ainsi que de l'augmentation de V h . De plus, la technologie de pince de tension d'émetteur pour V h amélioration avec un courant de défaillance acceptable (I t2 ) a également été proposé [5]. Néanmoins, le V h dans les approches susmentionnées n'est pas réglable, ce qui présente toujours des inconvénients et des limitations dans les applications polyvalentes.

Dans cette lettre, un nouveau redresseur commandé au silicium à haute tension de maintien (HHV-SCR) est proposé et démontré par simulation TCAD et test TLP. L'appareil atteint simultanément un V élevé h , élevé I t2 , et V réglable h sans masques ni marches supplémentaires. Le test TLP a été effectué pour valider que le V h peut être efficacement amélioré tout en maintenant un I suffisamment élevé t2 . Selon les résultats testés, le HHV-SCR présente un V quatre fois supérieur h que celle du LVTSCR avec une dégradation négligeable en I t2 .

Méthode

Dans ce travail, un nouveau SCR à haute tension de maintien avec une structure de recombinaison de porteurs intégrée est étudié. Les modèles physiques IMPACT.I, BGN, CONMOB, FLDMOB, SRH et SRFMOB sont utilisés en simulation numérique. Sur la base du modèle, H-RR et E-RR sont optimisés pour atteindre un V élevé h et un P élevé M . Les HHV-SCR et LVTSCR fabriqués sont testés par le système TLP.

Structure et mécanisme

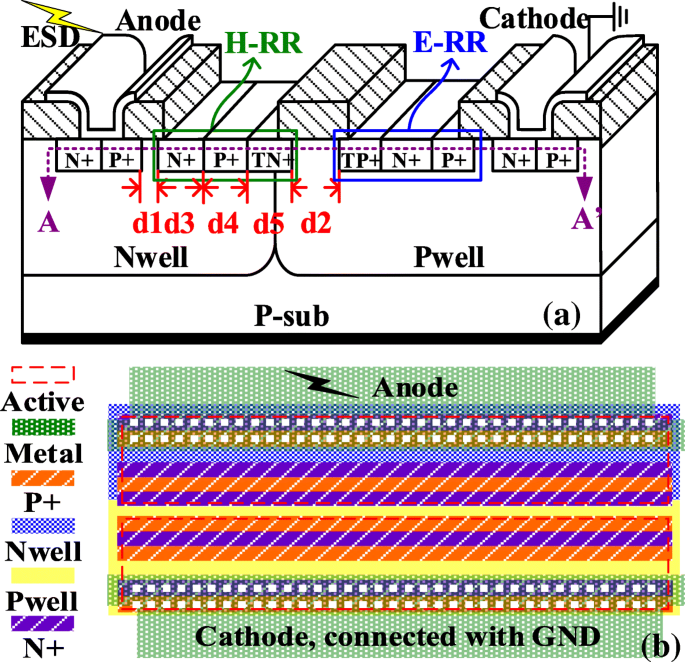

La vue en coupe schématique du HHV-SCR proposé et le schéma d'implantation sont illustrés aux Fig. 1a, b, respectivement. Les H-RR et E-RR nouvellement introduits formés par N+ et P+ flottants sont identiques aux N+ et P+ dans les zones anodique et cathodique, respectivement. Le N+ flottant dans H-RR (ou P+ flottant dans E-RR) est placé à côté de la région P+ dans l'anode (ou région N+ dans la cathode). De plus, le nouveau P+ flottant en H-RR (ou N+ flottant en E-RR) est également situé à côté du N+ flottant susmentionné en H-RR (ou P+ flottant en E-RR). Le N+ à déclenchement faible dans H-RR (TN+) et le P+ à déclenchement faible dans E-RR (TP+) sont également fabriqués par les mêmes procédés que la région N+ (ou P+) dans l'anode (ou cathode) pour assurer le V t1 dans une fourchette acceptable. En tant que tension ESD positive (V DES ) montant jusqu'à un certain niveau, la jonction TN+/P-well/TP+ à faible tension de claquage va d'abord claquer suivi du snapback des transistors parasites déclenché par le courant d'avalanche. La forte rétroaction positive des BJT parasites est responsable du V considérablement faible h du LVTSCR. Dans le HHV-SCR, le N+ dans H-RR (ou le P+ dans E-RR) va recombiner les porteurs minoritaires injectés depuis le bord de l'anode P+ (ou cathode N+), ce qui diminue le gain en courant (β ) du PNP (ou NPN) parasite et élimine l'effet bipolaire de surface. Il est important de noter que le P+ dans H-RR (ou le N+ dans E-RR) bloque le chemin de surface à faible résistance en recombinant les électrons de surface (ou trous). Par rapport au H-RR sans P+ (ou E-RR sans N+), le nouveau P+ dans H-RR (ou le N+ dans E-RR) fournit la recombinaison supplémentaire pour éliminer les électrons de surface (ou trous) injectés depuis la cathode ( ou anode) et celles induites par l'ionisation par impact (illustrées à la Fig. 3a), ce qui entraîne une augmentation supplémentaire de V h . En combinant ces modifications, une amélioration significative du FOM est vérifié. La figure de mérite (FOM) est citée dans [7] et définie comme la densité de puissance tolérable d'un seul appareil donnée par FOM=(V h ·Je t2 )/(N ·W ) pour évaluer le V h et Je t2 performances d'un seul appareil. Généralement, accompagné de l'amélioration de V h performances, cela provoque toujours la dégradation de I t2 en raison de la dissipation de puissance plus élevée. Par conséquent, le FOM le plus élevé signifie que le seul appareil peut atteindre la capacité de courant la plus élevée sur le V le plus élevé h niveau (N est le numéro du dispositif d'empilage; W est la largeur de l'appareil).

un La vue en coupe schématique du HHV-SCR proposé. b Le schéma d'implantation du HHV-SCR proposé

Résultats et discussion

Résultats simulés

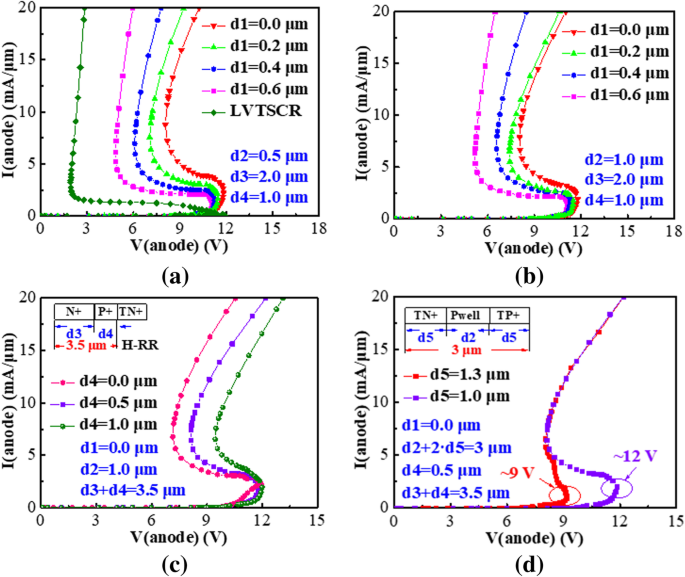

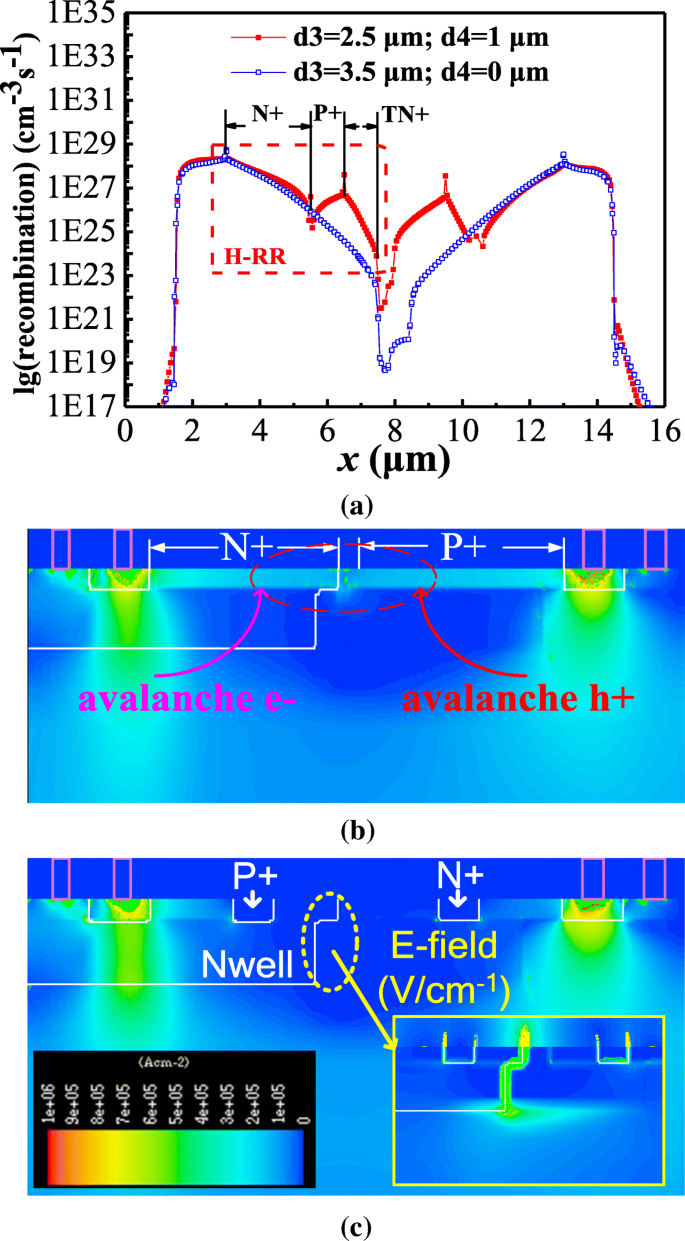

Les caractéristiques de l'appareil ont été étudiées et simulées par TCAD Medici, où les modèles correspondants tels que l'ionisation par impact et le modèle de mobilité dépendant de la concentration ont été utilisés. Les courbes I-V simulées du LVTSCR et du HHV-SCR sont illustrées à la Fig. 2. Le V h du LVTSCR est aussi faible que 1,8 V, tandis que le V h du HHV-SCR est amélioré de 4,6 V à 8,1 V avec d1 diminué de 0,6 m à 0 m pour d2 =0,5 m. En fait, le plus petit d1 est favorisé pour une meilleure capacité de recombinaison de N+ dans H-RR (ou P+ dans E-RR) pour obtenir un β inférieur , ce qui explique que le HHV-SCR atteint toujours le V le plus élevé h pour d1 =0 µm. Les résultats simulés de la figure 2b indiquent que le V h de HHV-SCR est encore améliorée avec d2 augmenté de 0,5 à 1 m en raison de l'augmentation de la longueur du dispositif. Pour démonstration, le P+ en H-RR (ou N+ en E-RR) est également un facteur clé pour augmenter le V h . Les résultats simulés sont présentés sur la figure 2c. Lorsque le H-RR (ou E-RR) avec d3 + d4 fixe est complètement formé par un dopage important N+ (ou P+) (par exemple, d3 =3,5 m, d4 =0 m), le V h est de 7,1 V. En insérant le P+ dans H-RR et N+ dans E-RR avec d3 + d4 fixes (par exemple, d3 =2,5 m, d4 =1,0 m), le V simulé h peut être augmenté jusqu'à environ 9,5 V. On peut en déduire que le nouveau P+ dans H-RR (ou N+ dans H-RR) est efficace pour recombiner les électrons d'avalanche de surface (ou trous) pour bloquer le chemin du courant de surface. Par conséquent, un V plus élevé h est nécessaire pour que le HHV-SCR maintienne le même courant de maintien (I h ). La courbe de recombinaison seule ligne AA′ montrée sur la figure 3a démontre l'augmentation du taux de recombinaison induite par le nouveau P+ dans H-RR (ou N+ dans E-RR). Les TN+ et TP+ sont adoptés pour assurer le V t1 dans une fourchette acceptable. En ajustant le d2 et le d5 au fixe d5 + d2 + d5, le V t1 de HHV-SCR peut être considérablement réduit de 12 V à 9,0 V pour répondre à la fenêtre de conception des circuits 5 V avec un impact négligeable sur V h , illustré à la figure 2d. Les diagrammes de distribution de courant des dispositifs simulés au point d'arrêt sont également représentés sur les figures 3b, c, respectivement. Par rapport à la distribution de courant dans le HHV-SCR avec d3 =3,5 m, d4 =0 m, le chemin du courant de surface dans le HHV-SCR proposé est bloqué en raison du taux de recombinaison supplémentaire dont bénéficient P+ dans H-RR et N+ dans E -RR.

Caractéristiques du snapback I-V simulé du LVTSCR conventionnel et du HHV-SCR proposé avec le d1 augmentant de 0 m à 0,6 m à a d2 =0.5μm et b d2 =1µm. c Les courbes I-V du HHV-SCR avec différents d3 et d4 pour le fixe d3 + d4 (d3 + d4 =3,5 μm). d Les courbes I-V de HHV-SCR avec divers V t1

un Les courbes de distribution de recombinaison, et les distributions actuelles de HHV-SCR avec (b ) d3 =3,5 m, d4 =0 m, et (c ) d3 =2,5 m, d4 =1 m

Résultats expérimentaux

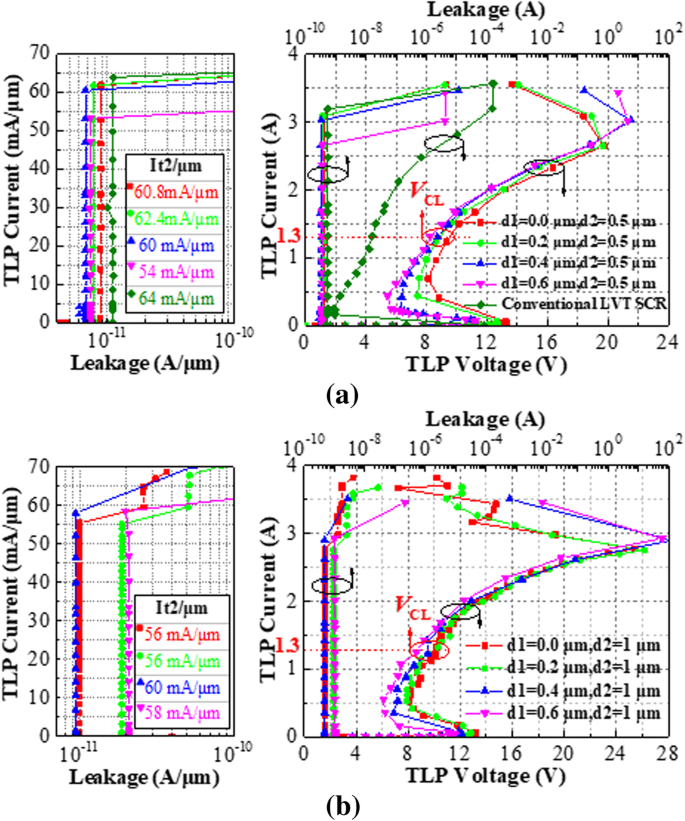

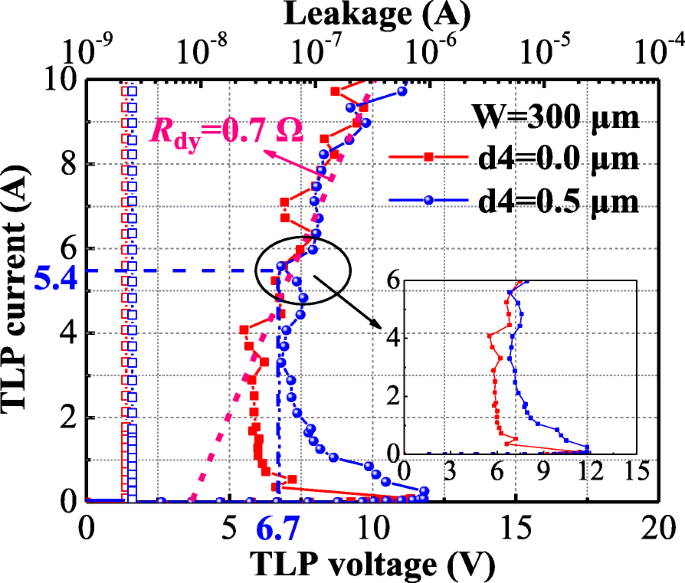

Les appareils fabriqués sont testés par le système TLP. Les largeurs totales (W) de tous les SCR testés sont de 50 m et avec un seul doigt pour la comparaison des paramètres (tableau 1). Tous les appareils testés occupent la même zone de mise en page. Les paramètres de l'appareil sont présentés dans le tableau 2. La figure 4a montre les courbes de mesure TLP des HHV-SCR avec d2 =0,5 m (appelés appareils B1) et le LVTSCR. D'après les résultats expérimentaux, le V h du HHV-SCR est augmenté de 5,5 à 8,0 V avec le d1 diminué de 0,6 m à 0,0 m, ce qui est bien supérieur à 1,8 V obtenu dans le LVTSCR conventionnel. Lorsque le d2 augmente de 0,5 à 1 m, les HHV-SCR correspondants (appelés dispositifs B2) obtiennent un V plus élevé h illustré à la figure 4b. Compte tenu de la fenêtre de conception, la tension de serrage (V CL ) sous l'indice donné est également un paramètre clé pour évaluer la capacité de serrage. D'après les résultats testés, le V CL du HHV-SCR à un doigt est également maintenu dans la plage acceptable au HBM =2 kV (I TLP =1,3 A) bien que la largeur du doigt ne soit que de 50 m. Cependant, tous les appareils ne peuvent pas fournir le V éligible CL sous la contrainte ESD plus forte en raison du V élevé h et grande résistance dynamique (R dy ) induite par la largeur de l'appareil sous-dimensionnée. Pour satisfaire l'exigence ESD plus élevée sur puce, la largeur du doigt est étendue jusqu'à 300 m acceptables pour d1 =0,6 m, d4 =0,5 m et d1 =0,6 m, d4 =0 m. Le test TLP illustré à la Fig. 5 démontre que le HHV-SCR avec d4 =0,5 m présente le R extrêmement faible dy (environ 0,7 Ω), robustesse ESD supérieure (I t2> 10 A) et V élevé h de 6,7 V. On peut observer que le V CL est aussi faible que 6,7 V au I TLP =5,4 A (HBM =8 KV). De plus, le plus élevé V h bénéficié de P+ en H-RR (ou N+ en E-RR) est également prouvée, par rapport à la courbe TLP de SCR avec d4 =0 m. Les résultats testés des dispositifs à un doigt de 50 μm sont répertoriés dans le tableau 1.

Courant de défaillance expérimental à la largeur de l'unité et caractéristiques TLP I-V correspondantes du LVTSCR conventionnel et des HHV-SCR proposés avec a d2 =0,5 m et b d2 =1 m à W =50 µm

Caractéristique expérimentale de TLP de HHV-SCR avec d4 =0,0 m et d4 =1,0 m à d1 =0,6 m, W =300 µm

Conclusion

Un nouveau HHV-SCR compatible avec les processus CMOS est étudié et mesuré par simulation TCAD et système TLP. Comparé au LVTSCR conventionnel, le HHV-SCR présente un V considérablement amélioré h (une amélioration de plus de 450% du V h est atteint) et sans sacrifier la surface de la puce. De plus, le V h du HHV-SCR peut être ajusté de 5,5 V à 8,1 V pour satisfaire les différents V h exigences avec dégradation négligeable en I t2 . En termes de P M , par rapport au LVTSCR conventionnel, une amélioration de plus de 200 % est également obtenue.

Disponibilité des données et des matériaux

Toutes les données générées ou analysées au cours de cette étude sont incluses dans cet article publié.

Nanomatériaux

- Mémoire sur la technologie des circuits intégrés pour les microcontrôleurs et les systèmes embarqués

- Maxim :double émetteur-récepteur IO-Link avec régulateur DC-DC et protection contre les surtensions

- TRS-STAR :systèmes embarqués robustes et sans ventilateur d'avalue

- Nouveaux nanoparticules Au Nanostars@PEG biocompatibles pour l'imagerie CT in vivo et les propriétés de clairance rénale

- Nanosphères de carbone monodispersées à structure poreuse hiérarchique comme matériau d'électrode pour supercondensateur

- Amélioration de la modulation et de l'absorption de fréquence du microbolomètre THz avec structure en micropont par antennes de type spirale

- Nouveau double mitochondrial et récepteur CD44 ciblant des nanoparticules pour une libération déclenchée par des stimuli redox

- Automatisation et cybersécurité :protection complète pour les clients

- Matériaux et conception de PCB pour haute tension