L'optimisation de la programmation de la DRAM 1T sans condensateur basée sur le TFET à double porte

Résumé

Le plus grand volume de condensateur et le courant de fuite plus élevé du transistor sont devenus les inconvénients inhérents à la mémoire dynamique à accès aléatoire (DRAM) traditionnelle à un transistor (1T)-un condensateur (1C). Récemment, le FET à effet tunnel (TFET) est appliqué dans la cellule DRAM en raison du faible courant à l'état bloqué et du rapport de commutation élevé. La cellule DRAM TFET à double grille (DG-TFET) avec la structure sans condensateur a des performances supérieures, un temps de rétention (RT) plus élevé et une faible dépendance à la température. Mais les performances de la cellule TFET DRAM sont sensibles aux conditions de programmation. Dans cet article, la ligne directrice de l'optimisation de la programmation est discutée en détail à l'aide de l'outil de simulation Silvaco Atlas. Les opérations d'écriture et de lecture de la DRAM DG-TFET dépendent du tunneling bande à bande (BTBT). Lors de l'opération d'écriture, les trous issus de BTBT régis par Gate2 sont stockés dans des puits de potentiel sous Gate2. Une petite tension négative est appliquée à Gate2 pour conserver les trous pendant une longue période pendant le maintien de « 1 ». Le BTBT régi par Gate1 influence principalement le courant de lecture. En utilisant la condition de programmation optimisée, la DRAM DG-TFET obtient le rapport de courant le plus élevé de la lecture "1" à la lecture "0" (10 7 ) et RT de plus de 2 s. Le RT plus élevé réduit le taux de rafraîchissement et la consommation d'énergie dynamique de la DRAM.

Contexte

La mémoire vive dynamique (DRAM) est devenue une cellule mémoire intégrale dans le système mobile et informatique [1,2,3]. Avec le rétrécissement de la géométrie du dispositif, le grand volume de condensateur est un inconvénient inhérent pour la cellule DRAM traditionnelle à un transistor (1T)-un condensateur (1C), ce qui limite son application à grande échelle. La cellule DRAM 1T sans condensateur basée sur le transistor à grille flottante a montré l'avantage potentiel par rapport à la DRAM 1T-1C conventionnelle pour l'emballage haute densité de la mémoire [4]. Dans le transistor à grille flottante, les charges dans la région du substrat sont stockées dans la région à grille flottante par l'effet tunnel de Fowler-Nordheim. Et l'opération de lecture dépend de l'émission thermoionique [5, 6], qui est la même que celle du transistor à effet de champ métal-oxyde-semiconducteur (MOSFET). En conséquence, le courant de lecture de la DRAM avec le transistor à grille flottante dépend fortement de la température. De plus, l'émission thermoionique fait que l'oscillation sous-seuil (SS) du transistor est supérieure à 60 mV/déc, ce qui fait du courant de fuite élevé et de la consommation d'énergie les principaux défis [7,8,9].

Récemment, le transistor à effet de champ tunnel (TFET) a été considéré comme un candidat prometteur pour les futurs dispositifs électriques de faible puissance [10,11,12]. Le mécanisme de conduction principal du TFET est l'effet tunnel de bande à bande (BTBT) au lieu de l'émission thermoionique, ce qui lui permet d'obtenir plusieurs avantages tels que le SS inférieur à 60 mV/dec, un faible courant de fuite à l'état bloqué et une faible dépendance à la température. [13, 14]. Jusqu'à présent, de grandes quantités de travaux de recherche sur le TFET se concentrent principalement sur l'étude des performances du dispositif d'un seul TFET et certains circuits simples sont constitués de TFET. Cependant, le niveau élevé de I sur /Je désactivé du TFET lui permet de servir à la cellule DRAM [15]. En particulier, le faible courant de fuite à l'état bloqué peut réduire le courant de lecture « 0 » et la consommation d'énergie de la cellule DRAM. Les chercheurs ont conçu une DRAM TFET à double grille (DG-TFET) avec la structure sans condensateur [16]. Dans la DRAM DG-TFET, le stockage de charge pendant l'opération d'écriture est basé sur le BTBT entre le canal et le drain, qui est principalement produit par Gate2. Dans le même temps, l'effet tunnel des électrons favorise l'accumulation de trous dans la région du canal sous Gate2. Gate1 est principalement responsable de l'opération de lecture. Le courant de lecture de la DRAM DGTFET repose principalement sur le BTBT entre la région de source et la région de canal. Certains groupes de recherche ont démontré que le courant de lecture de la DRAM DG-TFET dépend peu de la température. Et la DRAM DG-TFET peut obtenir un temps de rétention supérieur à la cible (64 ms) [17]. Mais le rapport actuel de la lecture "1" à la lecture "0" et RT n'est pas la valeur optimale en raison de la condition de programmation non optimisée.

Les performances de la DRAM TFET, en particulier le rapport actuel de la lecture "1" à la lecture "0", dépendent fortement des conditions de programmation. Gate2 influence principalement le BTBT lors de l'opération d'écriture, qui domine la région de stockage des charges et du potentiel bien sous Gate2. Gate1 régit le BTBT pendant l'opération de lecture, ce qui influence principalement le courant de lecture "1". Les polarisations appropriées de Gate1 et Gate2 peuvent permettre à la DRAM DGTFET d'obtenir le rapport de courant le plus élevé. Il existe peu de littérature étudiant l'influence de la condition de programmation sur le courant de lecture. Dans cet article, une directive détaillée d'optimisation de la programmation est proposée, y compris les opérations d'écriture, de maintien et de lecture. En appliquant la condition de programmation optimisée, la DRAM DG-TFET obtient les performances optimales :le rapport de courant de lecture jusqu'à 10 7 et le RT de plus de 2 s. Et en appliquant la tension de programmation optimisée, le courant de lecture "0" est bien inférieur à celui rapporté dans la référence [16, 18], ce qui est utile pour la réduction de la consommation électrique.

Méthodes

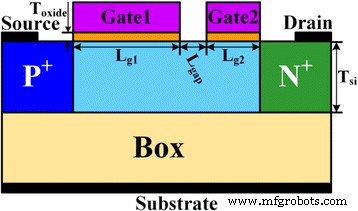

La structure du DG-TFET étudiée dans cet article est illustrée à la Fig. 1. La concentration de dopage à la fois du P + source et N + le drain est de 1 × 10 20 /cm 3 . Le canal intrinsèque est divisé en deux segments :Gate1 et Gate 2, et il existe un court écart entre Gate1 et Gate2. Gate1 et Gate2 sont N + polysilicium et P + polysilicium, respectivement. Le P + le polysilicium Gate2 peut créer et maintenir le puits physique pour le stockage de charge et remplacer la DRAM conventionnelle à base de TFET qui utilise un P + région de poche comme zone de stockage. Tandis que pour un N + polysilicium Gate1, la concentration de trous dans la région sous-jacente entre Gate1 et Gate2 est faible, ce qui est utile pour l'opération de lecture. Ainsi, un P + Le polysilicium Gate2 a été choisi pour avoir une région de stockage plus profonde qui pourrait faciliter une rétention plus longue, tandis qu'un N + Le polysilicium Gate1 est sélectionné pour contrôler le mécanisme de tunnel pendant l'opération de lecture [18].

Schéma de la cellule DRAM DG-TFET. Cette figure montre le schéma de la cellule DRAM TFET à double porte (DGTFET), y compris Gate1, Gate2, source, drain et channel. Dans cette conception, la région source et la région drain sont P + dopage et N + dopage, respectivement. Gate1 et Gate2 sont N + polysilicium et P + polysilicium, respectivement

Les paramètres détaillés de l'appareil dans les simulations sont les suivants :l'épaisseur de silicium massif (T si ) est de 20 nm ; les longueurs de Gate1 (Lg1 ) et Gate2 (Lg2 ) sont respectivement de 400 nm et 200 nm ; la longueur de l'écart (L écart ) entre Gate1 et Gate2 est de 50 nm ; l'épaisseur d'oxyde de grille (HfO2 ) (T oxyde ) est de 3 nm. Les conditions de programmation optimisées sont présentées dans le tableau 1. Les directives d'optimisation des conditions de programmation seront discutées en détail dans les sections suivantes.

Toute l'analyse est réalisée dans l'outil Silvaco-Atlas en utilisant le modèle BTBT non local [19]. Le BTBT non local prend en compte la génération non locale d'électrons et de trous, de sorte qu'il peut modéliser le processus d'effet tunnel avec plus de précision. Les paramètres du modèle tunnel sont calibrés selon les données expérimentales de la référence [20]. De plus, des modèles physiques comprenant la recombinaison Shockley-Read-Hall, les statistiques de Fermi ainsi que le dopage et la mobilité dépendante du champ électrique sont également utilisés. Selon les approches de [16, 18], les durées de vie des électrons et des trous sont fixées à 100 ns. La température par défaut est de 300 K.

Résultats et discussion

Le principe de fonctionnement de la cellule DRAM DG-TFET est différent de celui de la DRAM traditionnelle. Les opérations d'écriture et de lecture sont toutes deux basées sur le BTBT, mais chacune d'elles a une fonction différente. Le BTBT lors de l'écriture « 1 » conduit les trous à être stockés dans le puits de potentiel sous Gate2, ce qui peut élever le courant de lecture « 1 ». Pendant l'opération de lecture, le courant de drain dépend principalement du BTBT près du côté source. De plus, les deux portes jouent également des rôles différents :Gate1 et Gate2 déterminent principalement l'opération de lecture et l'opération d'écriture, respectivement.

Opération d'écriture

Lors de l'écriture "1", Gate2 avec le biais négatif va augmenter la bande d'énergie du canal sous Gate2, ce qui diminue la largeur de la barrière et produit le BTBT entre le canal et le drain. Et ce biais négatif Gate2 induit également un potentiel profond bien sous Gate2. En raison de l'effet tunnel des électrons du canal au drain, la région du canal sous Gate2 est complètement épuisée et de nombreux trous sont accumulés dans ce puits de potentiel. Lors de l'écriture "0", Gate2 avec le biais positif fait expulser les trous du puits de potentiel qui se recombine côté drain [21].

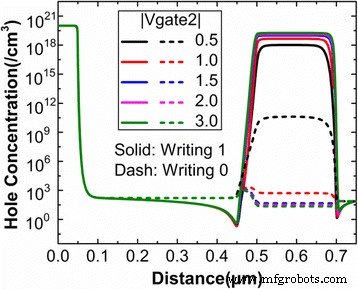

Généralement, la valeur absolue de la tension Gate2 reste inchangée pour l'écriture "1" et l'écriture "0". La figure 2 montre la variation de la concentration de trous avec la tension Gate2 après l'opération d'écriture. Lorsque la tension Gate2 est de 0,5 V, la concentration de trous après l'écriture de « 0 » est plus élevée en raison de la présence de puits de potentiel, ce qui est préjudiciable pour l'état « 0 ». Lorsque la valeur absolue de la tension Gate2 est supérieure à 1 V, la concentration de trous après avoir écrit « 0 » et « 1 » n'a pas de variation évidente. Cela suggère que BTBT est saturé pour écrire "1" et que tous les trous accumulés lors de l'écriture "1" sont expulsés du puits de potentiel après avoir écrit "0". Et la différence de concentration de trous entre l'écriture "1" et l'écriture "0" est très évidente, ce qui est bénéfique pour faire la distinction entre l'état "1" et l'état "0".

Concentrations de trous à la surface du canal après l'opération d'écriture. Cette figure montre les variations de concentration de trous avec les différentes tensions Gate2. La ligne de coupe est prise à la surface du dispositif de la région de source à la région de drain. Dans cette figure, la ligne continue et la ligne pointillée représentent la concentration de trous après avoir écrit "1" et écrit "0", respectivement

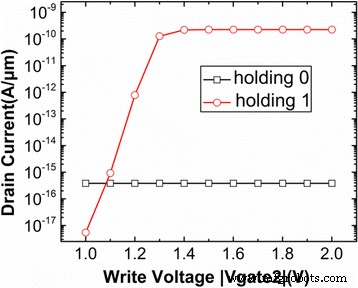

Mais le biais Gate2 lors de l'opération d'écriture ne peut pas être déterminé uniquement par la concentration de trous. La figure 3 indique que la polarisation Gate2 pendant l'opération d'écriture a un effet significatif sur le courant de drain après l'opération de maintien. L'ensemble de la tension de programmation pendant l'opération de maintien sera discuté dans la section suivante. La figure 3 révèle que le courant de drain après l'opération de maintien n'a pas de variation évidente lorsque la valeur absolue de la tension d'écriture est supérieure à 1,3 V. Par conséquent, les -1,3 et 1,3 V sont considérés comme la tension Gate2 optimale pendant l'écriture « 1 » et en écrivant « 0 », respectivement.

Courant de drain du DG-TFET après avoir maintenu « 0 » et maintenu « 1 ». Cette figure montre la variation du courant de drain après avoir maintenu « 0 » et maintenu « 1 » par rapport à la tension d'écriture

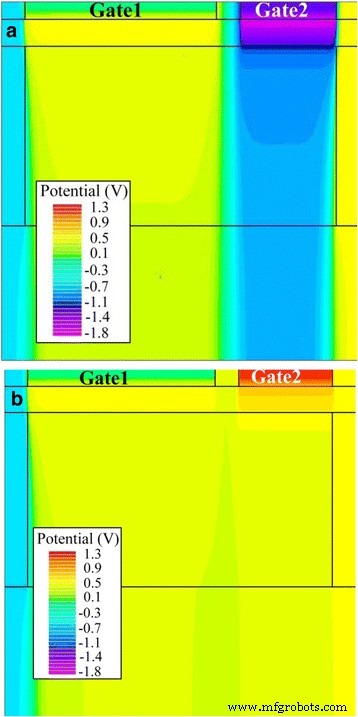

La figure 4a, b indique respectivement le contour de potentiel après l'écriture "1" et l'écriture "0" lorsque la valeur absolue de la tension d'écriture est de 1,3 V. De toute évidence, un puits de potentiel très profond est créé dans la région du canal sous Gate2 après l'écriture " 1", comme illustré à la Fig. 4 a. Les trous accumulés sont conservés dans ce puits de potentiel lors de l'écriture « 1 ». Cependant, les trous accumulés s'échappent de ce puits de potentiel lors de l'écriture "0".

Contours potentiels après a écrire « 1 » et b écrire « 0 » lorsque la valeur absolue de la tension Gate2 est de 1,3 V. a , b Les contours potentiels après avoir écrit « 1 » et « 0 », respectivement. Les contours de potentiel de cette figure sont extraits lorsque la valeur absolue de la tension Gate2 est définie sur 1,3 V

Opération de maintien

Le procédé de maintien est principalement utilisé pour modifier la rétention des charges. Habituellement, le biais zéro est utilisé pendant l'opération de maintien afin de réduire la consommation d'énergie [22]. Pendant l'opération de maintien, les trous accumulés dans le puits potentiel sont progressivement recombinés en raison de la diminution de la profondeur du puits potentiel. Par conséquent, l'objectif principal de l'optimisation de l'opération de maintien est d'éviter la recombinaison des trous pendant le maintien « 1 ». Dans cette conception, un petit biais négatif est appliqué à Gate2 pour conserver les trous dans le puits de potentiel après avoir maintenu « 1 », alors que le puits de potentiel est épuisé de trous après avoir maintenu « 0 ».

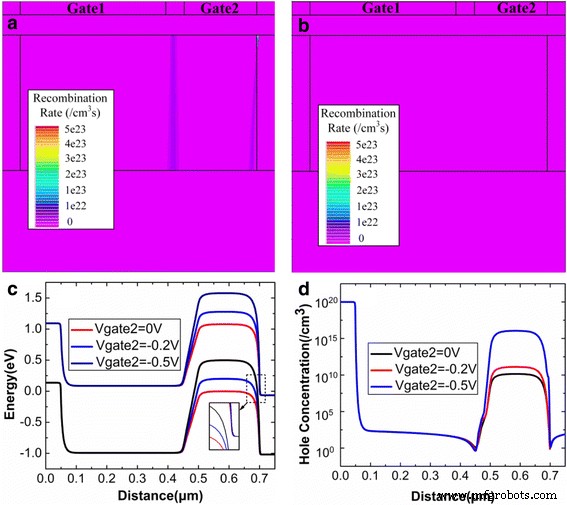

Avec la tension Gate2 plus négative (-0,5 V) pendant l'opération de maintien, la recombinaison des trous est éliminée après le maintien de « 1 », comme le montrent les figures 5a, b. L'élimination de la recombinaison des trous est bénéfique pour la rétention des trous lors du maintien « 1 ». Un petit biais négatif est appliqué à Gate2 pour améliorer la profondeur potentielle du puits et conserver les trous pendant une longue période, ce qui est bénéfique pour le temps de rétention de la DRAM DGTFET. Pendant le maintien de "0", une polarisation Gate2 négative peut augmenter la bande d'énergie de la région du canal sous Gate2, ce qui peut empêcher les électrons provenant de BTBT entre la source et le canal de s'écouler vers le côté drain. Par conséquent, Gate2 avec un négatif peut réduire le courant de lecture « 0 ». Cependant, Gate2 avec une tension plus négative (-0,5 V) diminue la distance d'effet tunnel près du côté drain, comme le montre la figure 5c. Cette distance de tunnelage réduite provoque le BTBT près du côté drain pendant le maintien « 0 », ce qui favorise l'accumulation de trous dans le puits de potentiel pendant le maintien « 0 », comme le montre la figure 5d. Ainsi, la tension Gate2 plus négative (-0,5 V) pendant le maintien « 0 » dégradera l'état « 0 ». Par conséquent, afin d'éliminer la recombinaison des trous et le BTBT pendant le maintien de "1" et le maintien de "0", respectivement, -0,2 V est considéré comme la polarisation Gate2 optimale pendant l'opération de maintien.

Taux de recombinaison dans la cellule DRAM DG-TFET après avoir maintenu « 1 » lorsque la tension Gate2 est a 0 V et b -0,5 V ; c diagramme de bande d'énergie et d concentration des trous après avoir maintenu « 0 ». un , b Le taux de recombinaison après avoir maintenu « 1 » lorsque la tension Gate2 est définie sur 0 V et -0,5 V, respectivement. c La bande d'énergie du dispositif de la région source à la région drain. d La concentration de trous de l'appareil après avoir percé « 0 ». La bande d'énergie et la concentration en trous sont extraites à 3 nm sous l'oxyde de grille

Opération de lecture

Par la suite, l'optimisation de l'opération de lecture est également étudiée. L'opération de lecture repose fortement sur le BTBT entre le P + source et canal. Lors de la lecture « 1 », Gate1 favorise principalement le BTBT côté source, tandis que Gate2 avec la haute tension abaisse la barrière énergétique qui résiste au passage des électrons du canal vers le drain. Mais lors de la lecture « 0 », il faut que Gate2 avec la petite tension puisse empêcher les électrons de s'écouler du canal vers le drain. Par conséquent, l'optimisation des tensions Gate1 et Gate2 est très importante pour l'opération de lecture.

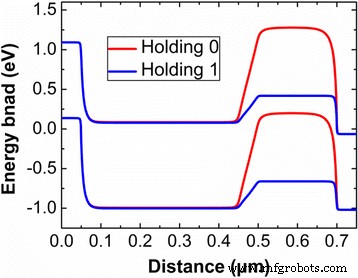

La figure 6 montre les différents diagrammes de bandes d'énergie après avoir maintenu « 1 » et « 0 ». Les mêmes tensions sont appliquées du côté de la grille lors de la lecture "1" et de la lecture "0". Étant donné que les polarisations de Gate positives seront utilisées pendant l'opération de lecture, la bande d'énergie sera supprimée à chaque lecture de « 1 » ou « 0 ». La bande d'énergie du canal sous Gate2 après avoir maintenu « 0 » est supérieure à celle après avoir maintenu « 1 », et cette bande d'énergie est également plus élevée lors de la lecture de « 0 » par rapport à celle lors de la lecture de « 1 ». L'énergie plus élevée du canal sous Gate2 créera une barrière efficace pour résister aux électrons circulant vers le côté drain, ce qui diminuera le courant de lecture "0".

Diagramme de bande d'énergie après a tenant « 1 » et b en maintenant « 0 ». un , b La bande d'énergie de l'appareil après avoir maintenu « 1 » et « 0 », respectivement. La bande d'énergie est extraite à 3 nm en dessous de l'oxyde de grille

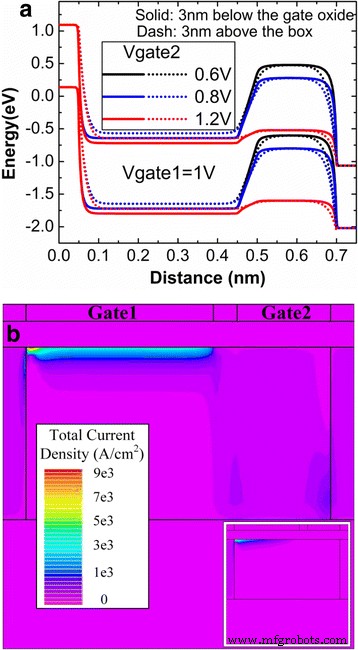

Pendant l'opération de lecture, la polarisation de drain est réglée sur 1 V afin que le courant de drain puisse être lu dans le DG-TFET. Tout d'abord, en gardant la tension Gate1 de 1 V, modifiez la polarisation de Gate2 pour choisir la tension Gate2 optimale. Parce que la tension Gate2 influence principalement le courant de lecture "0", l'optimisation de la tension Gate2 est analysée par le mécanisme de lecture "0". La figure 7a trace la variation de la bande d'énergie avec la tension Gate2 après avoir lu « 0 ». Lorsque la tension Gate2 est inférieure (0,6 ou 0,8 V), le canal sous Gate2 est complètement épuisé. Mais lorsque la tension Gate2 s'élève à 1,2 V, la bande d'énergie déroulante du canal sous Gate2 ne peut pas créer une barrière efficace pour empêcher les électrons de s'écouler vers le côté drain. La figure 7b et son encadré montrent respectivement la densité de courant totale après avoir lu « 0 » lorsque la tension Gate2 est de 1 V et 0,8 V. La densité de courant évidente peut être clairement trouvée dans la région du canal sous Gate2 lorsque la tension Gate2 est de 1 V, ce qui donner lieu au courant de lecture « 0 » plus élevé. Ainsi, le 0,8 V est considéré comme la tension Gate2 optimale pour le processus de lecture.

un Diagramme de bande d'énergie et b densité de courant totale après lecture de « 0 ». un , b La bande d'énergie et la densité de courant totale après la lecture de « 0 », respectivement. La bande d'énergie est extraite à 3 nm en dessous de l'oxyde de grille

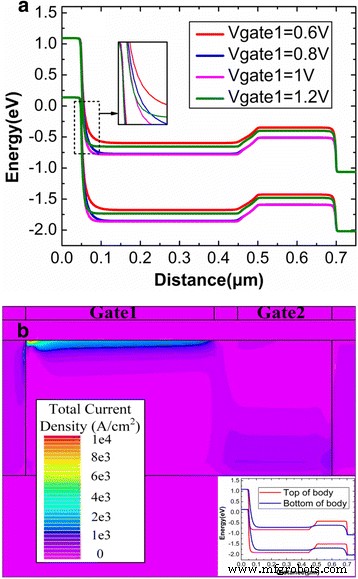

Enfin, l'optimisation du biais Gate1 est également menée. La figure 8a montre la variation de la bande d'énergie supérieure avec la tension Gate1. La largeur de la barrière BTBT du côté source diminue progressivement avec l'augmentation de la tension Gate1, mais cette tendance à la baisse commence à saturer lorsque la tension Gate1 est supérieure à 1 V. Et la tension Gate1 de 1 V ne peut pas avoir d'influence grave sur la lecture « 0 », ce qui a été démontré par la Fig. 7b. Par conséquent, 1 V est considéré comme le biais Gate1 optimal pendant l'opération de lecture.

un Diagramme de bande d'énergie et b densité de courant totale après la lecture de « 1 ». un , b La bande d'énergie et la densité de courant totale après la lecture de « 1 », respectivement. La bande d'énergie est extraite à 3 nm en dessous de l'oxyde de grille

Grâce à l'analyse ci-dessus, le puits de potentiel profond n'est formé qu'au sommet du canal sous Gate2 après avoir écrit « 1 ». Par conséquent, dans la région du canal sous Gate2, la bande d'énergie au sommet du canal est beaucoup plus élevée que celle au bas du canal. Cela démontre qu'il y aura une barrière en haut du canal sous Gate2 pendant la lecture « 1 ». L'encart de la figure 8b trace la bande d'énergie en haut et en bas du canal après avoir lu « 1 ». Il peut être clairement constaté qu'une barrière de canal plus élevée existe entre Gate1 et Gate2 au sommet du canal, mais cette barrière n'existe pas au bas du canal. Par conséquent, le chemin de conduction est au sommet du canal sous Gate1 et au bas du canal sous Gate2 pendant la lecture "1", ce qui peut être clairement démontré par la densité de courant sur la figure 8.

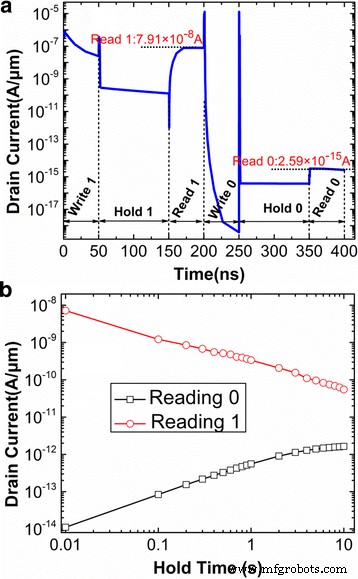

En appliquant la condition de programmation optimisée ci-dessus, la réponse transitoire de la cellule DG-TFET DRAM est illustrée à la figure 9. Les temps d'écriture et de lecture sont tous deux définis sur 50 ns, et le temps de maintien est défini sur 100 ns. Sur la figure 9a, le rapport actuel entre la lecture « 1 » et la lecture « 0 » est aussi élevé que 10 7 , ce qui est bien supérieur à 10 2 ~10 3 en référence [16, 18, 23]. De plus, lorsque le temps de maintien atteint 10 s, le rapport de courant dépasse toujours 10. Dans la référence [16], lorsque le temps de maintien est augmenté à 2 s, le rapport de courant n'est que d'environ 10. Par conséquent, le RT du DG-TFET La DRAM avec la condition de programmation optimisée est supérieure à 2 s. Ainsi, la condition de programmation optimisée permet à la cellule DG-TFET DRAM d'obtenir non seulement le rapport de courant de lecture le plus élevé, mais également le plus grand RT. De plus, le courant de lecture « 0 » avec une tension de programmation optimisée est bien inférieur à celui de la référence [16, 18, 22, 23], ce qui lui permet de répondre à l'application de plus faible puissance.

un Courants de drain transitoires dans la séquence de l'opération ; b variation du courant de lecture avec le temps de maintien. un Le courant transitoire de la cellule DGTFET DRAM pendant les opérations d'écriture, de maintien et de lecture. b Les variations du courant de lecture « 1 » et de lecture « 0 » avec les différents temps de perçage

Conclusions

La directive d'optimisation détaillée des conditions de programmation pour la DRAM DG-TFET est proposée dans cet article à l'aide de l'outil de simulation Silvaco-Atlas. Lors de l'écriture "1", Gate2 avec la tension négative (-1,3 V) crée un puits de potentiel, et le BTBT entre le canal et le drain fait accumuler les trous dans ce puits de potentiel. Pendant l'écriture "0", Gate2 avec la tension positive (1,3 V) fait s'échapper des trous du puits de potentiel. Pour l'opération de maintien, la petite tension négative (-0,2 V) est appliquée à Gate2 pour retenir les trous, ce qui peut améliorer la lecture du courant « 1 ». Après avoir maintenu "0", la barrière du canal sous Gate2 peut résister aux électrons circulant vers le côté drain pour réduire le courant de lecture "0". Pour l'optimisation de l'opération de lecture, la plus grande tension Gate1 (1 V) est principalement utilisée pour améliorer le BTBT du côté source lors de la lecture « 1 », tandis qu'une tension Gate2 appropriée (0,8 V) est utilisée pour résister aux électrons circulant vers le drain lors de la lecture. "0". La condition de programmation optimisée permet à la DRAM DG-TFET d'obtenir le rapport de courant le plus élevé (10 7 ) de la lecture « 1 » à la lecture « 0 » et un temps de rétention supérieur à 2 s. Et le courant de lecture « 0 » extrêmement faible est utile pour réduire la consommation d'énergie.

Nanomatériaux

- Les avantages de la surveillance à distance, de la programmation à distance et de la maintenance prédictive

- Maîtriser les défis de la programmation et du débogage multicœurs

- Tirer parti des technologies basées sur l'IoT sur le chantier de construction

- Système de sécurité biométrique basé sur le rythme cardiaque humain

- Commentaire :comprendre les méthodes de programmation des robots

- Le processus de conception et de mise en œuvre de l'automatisation de l'usine

- Remplir le blanc Exercice de programmation CNC Arcs multiples

- Remplissez l'exercice de fraisage de programmation CNC en blanc

- Remplissez l'exercice de programmation CNC vierge