Des articles récents détaillent l'évolutivité des nanotubes de carbone, les avancées en matière d'intégration

Les nanotubes de carbone (CNT) séduisent l'industrie des semi-conducteurs car ce sont des conducteurs électriques supérieurs par rapport au silicium avec une épaisseur de corps d'à peine 1 nanomètre. Alors pourquoi n'avons-nous pas encore de puces CNT dans tout, des mainframes aux appareils mobiles ? L'évolutivité du transistor et l'intégration à grande échelle sont toujours de grands défis. Mais deux articles que mes collègues et moi avons récemment publiés dans Science et Nature Nanotechnologie montrent des avancées prometteuses dans ces deux domaines essentiels à la réalité des puces CNT.

La réalisation de l'empreinte fait pencher la balance à l'échelle nanométrique

Premièrement :la mise à l'échelle. Nous savons que les puces de silicium 3D FinFET pourraient atteindre leur limite de puissance et de performance à 7 nanomètres. Et tandis que l'annonce récente de transistors nanofeuilles de silicium de 5 nm augmente l'échelle, la puissance et les performances au nœud suivant, nous connaissons également ses limites.

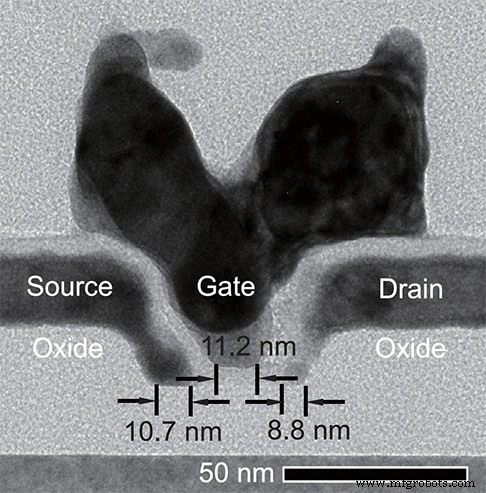

Un transistor est plus que sa porte. La source, le drain et les entretoises s'additionnent pour une empreinte totale. Sur la photo :un transistor CNT avec une empreinte de 40 nm. (Figure 1B dans "Transistors à nanotubes de carbone à l'échelle d'une empreinte de 40 nanomètres", publié dans Science.)

Dans notre Science article « Transistors à nanotubes de carbone à l'échelle d'une empreinte de 40 nanomètres », nous avons mis à l'échelle un transistor CNT entier pour atteindre l'objectif de l'International Technology Roadmap for Semiconductors (ITRS) de transistors atteignant une empreinte de 40 nm - un objectif qu'ils se sont fixé et n'a pas changé depuis 2015 Pour référence, les transistors 14 nm haut de gamme d'aujourd'hui occupent en réalité environ 90 nm d'espace de puce.

Nous pouvons potentiellement dimensionner un transistor CNT plus loin que le silicium pour la principale raison qu'ils ne font intrinsèquement que 1,2 nm d'épaisseur. Cette minceur a l'effet domino de réduire la longueur de grille à 10 nm car il offre un meilleur contrôle électrostatique de la grille et aide à minimiser les fuites de courant. De plus, les électrons se déplacent plus rapidement dans les NTC que le silicium, ce qui améliore les performances de l'appareil.

Mais nous avions besoin d'un nouveau moyen de connecter les CNT à leur source et à leur drain (photo). Nous devions trouver le mélange parfait de matériaux capables de « cuire » ces éléments de 10 nm ensemble à une température de fabrication. Nos précédents contacts fonctionnels liés entre la source et le CNT et le drain et le CNT nécessitaient des températures de traitement si élevées, à environ 850°C, que le canal ne pouvait pas être plus court que 60-100 nm. Le passage à un alliage cobalt-molybdène pour le câblage entre les éléments a effectivement abaissé la température à un niveau acceptable de 650°C - réduisant les distances à 10 nm.

Le Dr Qing Cao, l'auteur principal de l'article, et d'autres collègues de l'équipe ont démontré qu'avec cette nouvelle empreinte, le transistor CNT peut atteindre des performances comparables aux normes de transistors actuelles.

Les éléments CNT se réunissent sur un oscillateur en anneau

La démonstration d'un transistor unique aussi extrêmement dimensionné, même avec un flux de processus moins manufacturable, nous a motivés à résoudre les défis d'intégration des technologies CNT pratiques. Et au cours des cinq dernières années, mon équipe a développé des éléments individuels de la technologie CNT. Nous savons comment séparer les CNT semi-conducteurs, fabriquer des CNT « auto-assemblés » sur une plaquette et fabriquer des transistors à effet de champ CNT à canal n fiables, ou « FET » (qui se dégradent généralement rapidement en raison de l'oxydation des métaux de contact) en utilisant diverses techniques.

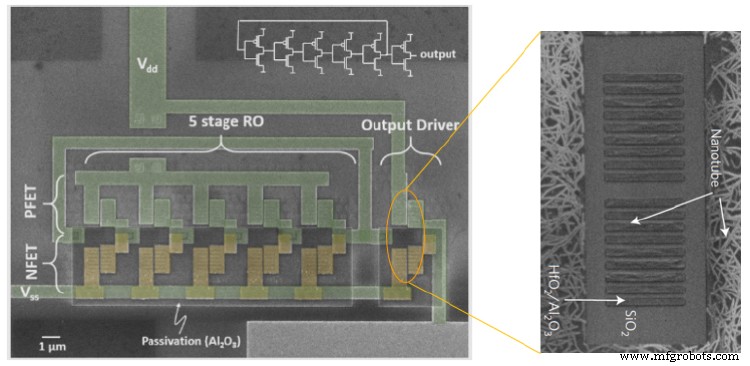

Tous les éléments doivent fonctionner simultanément dans un oscillateur en anneau fonctionnel . Sur la photo :image de microscopie électronique à balayage vue de dessus d'un oscillateur en anneau CNT à 5 étages et des tranchées placées de CNT. (Figure 1B dans « Circuits intégrés logiques à grande vitesse avec des nanotubes de carbone auto-assemblés traités en solution », publié dans Nature Nanotechnology.)

Le défi du développement d'une technologie perturbatrice à un stade précoce est que certaines techniques utilisées pour résoudre un problème peuvent finir par détruire d'autres éléments de l'appareil et du circuit. C'est la raison fondamentale pour laquelle toutes les démonstrations basées sur les nanotechnologies, comme celles utilisant les NTC, étaient limitées à un niveau d'intégration très faible. Et cela jette le doute sur la faisabilité de les utiliser de manière pratique.

Mais nous avons fait un grand pas en avant pour résoudre ce défi d'intégration dans notre Nature Nanotechnologie papier, "Circuits intégrés logiques à grande vitesse avec des nanotubes de carbone auto-assemblés traités en solution", où nous montrons comment assembler toutes les pièces pour créer un circuit de référence standard dans n'importe quelle technologie logique - un oscillateur en anneau CMOS.

Le Dr Jianshi Tang et mes autres membres de l'équipe ont combiné nos méthodes précédemment développées pour purifier et placer les NTC ensemble (individuellement, ils ressemblent à des pâtes penne flottant en solution), mais ont effectué un ajustement clé en ajoutant un oxyde de paroi latérale pour protéger le canal n-FET de se dégrader au cours du processus de fabrication (la paroi latérale a permis d'obtenir un rendement trois fois plus élevé, garantissant en outre que l'exigence de tous les éléments de l'oscillateur en anneau fonctionnant simultanément est satisfaite).

Les oscillateurs en anneau CMOS fonctionnels à 5 étages décrits dans le document (et illustrés ci-dessus) peuvent déjà fonctionner à 1 V (une norme de l'industrie). Malgré une faible densité de CNT dans le canal (vous pouvez voir les six CNT sur la même image) et des paramètres détendus, la fréquence de commutation de l'étage atteint 2,8 GHz (355 picosecondes) - le premier exemple de franchissement de la barrière du GHz pour toute démonstration basée sur les nanotechnologies. Il est prévu qu'avec une densité de plus de 100 NTC par micromètre et des dimensions de l'appareil correctement mises à l'échelle, nous pouvons atteindre un délai inférieur à la picoseconde, nettement plus rapide que les puces de silicium d'aujourd'hui.

Comme nous l'écrivons dans le journal :

Étant donné que les oscillateurs en anneau CMOS reflètent directement la maturité de la technologie, c'est la preuve tant attendue que les problèmes importants de la transition de ce matériau prometteur vers une technologie réelle sont résolus avec vigueur.

Enregistrer

Nanomatériaux

- Papier carbone

- Carbone M2

- Les nanotubes de carbone repoussent les limites de l'électronique flexible

- Fabrication et imagerie de cyclocarbone

- Ocean Carbon imagé à l'échelle atomique

- Fil de nanotubes de carbone, muscle et feuilles transparentes

- Oxynitrure de bore en tant que nouveau photocatalyseur sans métal

- Points de carbone bleu luminescent à haute efficacité indépendants de l'excitation

- Diélectrophorèse assistée par chauffage pour film de nanotubes de carbone à paroi unique alignés de très haute densité