Importance de la vérification de la fiabilité dans les processeurs AI/ML

Avec l'adoption de l'intelligence artificielle et de l'apprentissage automatique dans une grande variété d'applications, la vérification de la fiabilité des processeurs AI/ML est essentielle car les défaillances peuvent avoir des conséquences majeures pour la validité et la légitimité de la technologie AI/ML.

Au cours des dernières années, le nombre d'entreprises déployant l'intelligence artificielle (IA) et l'apprentissage automatique (ML) a augmenté rapidement dans un large éventail d'applications. En fait, des études montrent que 2019 a été une année record pour les entreprises adoptant l'IA et le ML, et que ces entreprises considèrent ces deux fonctionnalités comme les plus nécessaires pour atteindre leurs stratégies et objectifs commerciaux. Cette adoption croissante est principalement due à l'amélioration des algorithmes, aux progrès de la conception matérielle et à l'augmentation du volume de données créé par la numérisation des informations.

Cependant, pour soutenir et maintenir la croissance de l'IA/ML, les entreprises doivent continuer à prouver au marché que les résultats qu'elles obtiennent avec les technologies d'IA/ML sont dignes de confiance. Cette confiance commence par la conception et la vérification des circuits intégrés (CI) qui sous-tendent la fonctionnalité AI/ML.

Classification de l'IA et du ML

Le traitement de l'IA peut être largement classé en centre de données/cloud ou intégré, selon qu'il est effectué sur un site cloud/centre de données, ou du côté de l'utilisateur final (en intégrant une puce IA dédiée ou un moteur de coprocesseur IA avec un système sur puce (SOC) à l'intérieur des appareils ou à la périphérie). Edge dans ce contexte fait référence à un serveur local ou à une machine plus proche de l'appareil qu'un centre de données ou un cloud.

En termes d'application cible, un périphérique périphérique peut être classé en apprentissage (ML) ou en inférence. Historiquement, la partie formation était réalisée sur le site cloud, la partie inférence étant gérée soit dans le cloud, soit sur l'appareil périphérique. Avec le développement de nouvelles solutions d'informatique de pointe hautes performances, nous assistons à un changement de paradigme, car de plus en plus d'activités de formation sont transférées vers la périphérie.

Conception de puce AI/ML

Les puces AI/ML dans les solutions informatiques de pointe ou intégrées dans des appareils locaux sont conçues pour être utilisées dans des environnements spécifiques, tels que l'entreprise, l'automobile, l'industrie, la santé, l'Internet des objets (IoT), etc. Certaines de ces applications sont critiques, c'est-à-dire tout échec peut avoir des conséquences désastreuses dans le monde réel. Par exemple, considérons les systèmes avancés d'aide à la conduite (ADAS) utilisés à l'intérieur des automobiles. Si un processeur ADAS subit plus d'une latence donnée lors de la lecture des données du capteur et de l'établissement d'une inférence, cela peut provoquer une collision.

Les circuits intégrés utilisés dans les applications AI/ML sont caractérisés par de grandes unités de calcul de traitement parallèle, une dissipation de puissance élevée et des circuits complexes qui peuvent offrir des performances maximales dans un budget de puissance strict. Alors que certaines entreprises utilisent des unités centrales de traitement (CPU) traditionnelles pour les tâches liées à l'IA, certains experts du secteur soutiennent que l'utilisation de processeurs n'est pas très efficace, en raison de la nature distribuée des algorithmes d'IA de pointe. Ces algorithmes se prêtent bien aux solutions de calcul parallèle, comme celles fournies par les unités de traitement graphique (GPU). En raison de leur nature reconfigurable, les réseaux de portes programmables sur site (FPGA) ont également suscité un intérêt pour une utilisation en tant qu'accélérateurs pour les puces d'IA.

ASIC dans les applications AI/ML

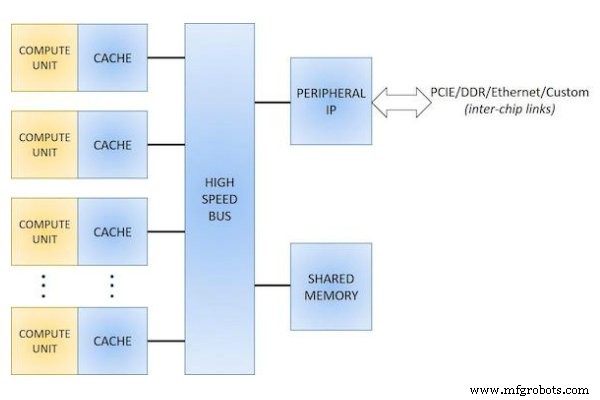

Dans l'ensemble, il existe un consensus croissant sur le fait que les problèmes délicats de l'IA et du ML ne se prêtent pas à une solution de conception unique. Pour lutter contre ce problème, de nombreuses entreprises développent leurs propres circuits intégrés spécifiques aux applications (ASIC), qu'elles optimisent en conjonction avec la pile logicielle pour offrir la meilleure valeur pour une application AI/ML donnée (Figure 1).

Figure 1. Schéma fonctionnel pour une conception de puce ASIC AI.

Ces entreprises revendiquent divers avantages à l'utilisation de ces ASIC, tels que de meilleures performances, plus d'opérations par cycle, une conception plus simple et plus déterministe par rapport à un CPU ou un GPU, des économies de surface (en raison de l'exclusion des constructions et mécanismes complexes utilisés dans un CPU), consommation d'énergie réduite et temps de développement plus rapide.

Informatique hétérogène

Il y a également eu une augmentation de l'utilisation de l'informatique hétérogène, des systèmes qui utilisent une combinaison de différents types de cœurs de calcul dans le but de combiner le meilleur des différentes capacités. Par exemple, dans un système utilisant une combinaison d'un processeur et d'un processeur graphique, le calcul hétérogène peut être bénéfique en déchargeant les tâches parallèles sur le processeur graphique, tandis que le processeur gère des tâches telles que le contrôle de processus, qui est par nature sériel.

Un aspect commun entre les différentes classes de processeurs d'IA est qu'ils sont optimisés pour des performances élevées et une faible latence, offrant souvent des multiplicateurs de performances téra opérations par seconde (TOPS). Pour prendre l'avantage sur ce marché hautement concurrentiel, l'efficacité énergétique (mesurée par la performance par watt) est devenue tout aussi importante que le débit brut. L'efficacité énergétique est souvent obtenue en utilisant une combinaison d'une ou plusieurs techniques de conception telles que la synchronisation de puissance et d'horloge, la mise à l'échelle dynamique de tension et de fréquence, les conceptions multi-Vt, etc.

Il est essentiel de garantir la conception et la vérification fiables de ces circuits intégrés complexes, car les défaillances de circuits dans ces puces peuvent avoir des conséquences majeures sur la validité de la technologie et la légitimité des résultats qu'elles fournissent.

Vérification de la fiabilité AI/ML IC

La vérification de la fiabilité est un défi majeur dans les puces AI/ML, en raison de la taille et de la complexité de ces conceptions, avec des nombres de transistors de l'ordre de millions - parfois même de plusieurs milliards. Par exemple, le GPU TESLA P100 de NVIDIA affiche un nombre impressionnant de transistors de 15,3 milliards, tandis que le Loihi IC d'Intel contient 128 cœurs neuromorphiques et 3 cœurs X-86, avec 2,07 milliards de transistors. Et, comme les exigences de fiabilité pour chaque environnement d'utilisation sont différentes, les concepteurs doivent comprendre l'ensemble d'exigences applicables et s'assurer qu'ils sont satisfaits en testant leurs conceptions par rapport à des spécifications d'exigences de fiabilité bien définies.

Méthodes de vérification de la fiabilité de la conception

Traditionnellement, les concepteurs utilisaient diverses méthodes pour garantir la fiabilité de la conception, notamment des techniques d'inspection manuelle et de simulation, en s'appuyant principalement sur l'expertise et l'expérience de leur équipe de conception. Cependant, l'inspection manuelle n'est pas une approche réalisable pour ces puces AI/ML volumineuses et complexes, car elle prend du temps et est sujette aux erreurs humaines, et pratiquement impossible de fournir une couverture suffisante. Les approches de simulation traditionnelles de type SPICE ne sont pas non plus pratiques pour ces circuits intégrés, en raison de leur manque d'évolutivité pour les conceptions volumineuses.

Pour surmonter les problèmes de capacité et d'exécution, de nombreuses équipes de conception partitionnent manuellement une conception et vérifient indépendamment différents blocs de propriété intellectuelle (IP) via la simulation ou des outils traditionnels. Cependant, il existe de nombreuses interactions entre différents blocs IP dans une conception (par exemple, entre différents cœurs de calcul et le bus ou le lien ou la mémoire à bande passante élevée), et les interactions entre les interfaces ont souvent tendance à être négligées lors d'un processus de partitionnement manuel. Les outils traditionnels de vérification des circuits intégrés ont des temps d'exécution excessivement longs pour vérifier ces conceptions complexes, ce qui prend souvent des jours pour vérifier les conceptions volumineuses et retarde potentiellement le délai de commercialisation.

Les lacunes de chacun de ces processus mettent en évidence le besoin d'une solution complète d'automatisation de la conception électronique (EDA) automatisée pouvant tirer parti de la puissance de calcul de plusieurs processeurs et périphériques simultanément. Grâce à la vérification de la fiabilité automatisée et qualifiée, les équipes de conception et de vérification des produits peuvent converger plus rapidement vers la vérification et les correctifs de fiabilité, réduisant ainsi leur délai d'exécution global (TAT) de quelques jours à quelques heures.

La plate-forme de fiabilité Calibre PERC

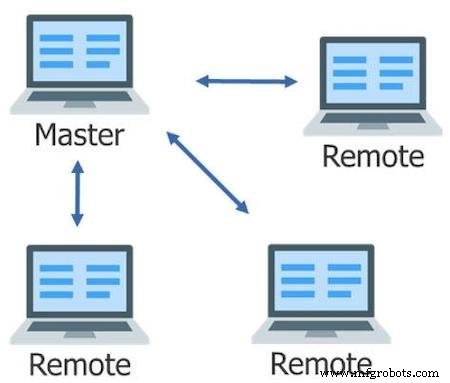

Au cours des dernières années, une nouvelle classe d'outils de vérification de la fiabilité des circuits intégrés qui résolvent ces problèmes de processus est apparue. Des outils tels que la plate-forme de fiabilité Calibre™ PERC™ exploitent un ensemble riche de fonctionnalités et de fonctionnalités pour fournir une vérification de fiabilité rapide et qualifiée par les fonderies. Par exemple, la plate-forme de fiabilité Calibre PERC tire parti de la mise à l'échelle multithread (MT) et multithread flexible (MTflex) de la plate-forme Calibre, qui répartit les tâches sur plusieurs CPU et/ou machines distantes pour fournir une exécution rapide et efficace des processus de vérification sur des puces volumineuses et complexes comme les circuits intégrés AI/ML (Figure 2).

Figure 2. La mise à l'échelle flexible et multithread répartit les tâches sur plusieurs télécommandes pour une exécution globale plus rapide.

Au-delà de ces mécanismes de base mais essentiels, la plate-forme de fiabilité Calibre PERC fournit un traitement innovant qui combine à la fois les informations de liste d'interconnexions et de mise en page d'une conception pour évaluer rapidement et avec précision un large éventail de problèmes de fiabilité potentiels. En permettant aux concepteurs de réduire efficacement et en toute confiance la vulnérabilité d'une conception aux performances et aux défaillances opérationnelles, cette approche de la vérification avancée de la fiabilité aide à soutenir la croissance continue et l'adoption d'une technologie d'IA/ML de confiance.

Fiabilité au niveau du transistor

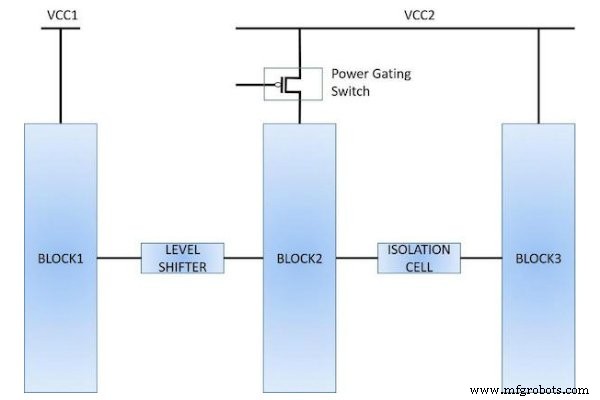

La majorité des conceptions ML/AI utilisent plusieurs domaines d'alimentation à diverses fins, telles que la fourniture d'une alimentation propre et sans bruit pour l'IP analogique, permettant de verrouiller ou de couper l'alimentation d'une certaine zone d'une puce, la mise à l'échelle les tensions augmentent ou diminuent indépendamment pour les IP sélectionnées, ou répondent à des demandes de courant élevées à l'aide de plusieurs régulateurs de tension. Par exemple, le processeur Skylake d'Intel contient neuf domaines d'alimentation principaux.

La mise en œuvre d'une conception à plusieurs domaines d'alimentation nécessite l'utilisation d'éléments de circuit spéciaux, tels que des régulateurs de tension, des commutateurs d'en-tête et de pied de page, des décaleurs de niveau, des cellules d'isolement et des cellules de rétention d'état. Ces éléments présentent un ensemble unique de défis pour la vérification de la fiabilité. Par exemple, les concepteurs doivent vérifier que les cellules de décalage de niveau ou d'isolement appropriées sont utilisées à chaque interface de domaine et qu'elles sont correctement connectées (Figure 3).

Figure 3. L'utilisation d'éléments spéciaux (tels que des décaleurs de niveau, des cellules d'isolement et des commutateurs de déclenchement de puissance) dans une conception à faible consommation nécessite des techniques de vérification spécialisées.

Ils doivent également s'assurer qu'ils utilisent les types d'appareils appropriés sur les différents domaines de puissance, tels que les appareils à oxyde épais pour l'alimentation haute tension. La vérification de ces conditions nécessite des connaissances et des processus très spécifiques.

La technique du format de puissance unifiée

Le format de puissance unifié (UPF) est une technique largement utilisée qui permet aux concepteurs d'employer une description cohérente de l'intention de puissance tout au long du flux de conception. Cependant, les flux de vérification traditionnels basés sur UPF sont utilisés pour valider les adresses IP au niveau de la logique ou de la porte, mais ils n'ont pas la capacité de valider les implémentations finales au niveau du transistor, en particulier les connexions de puits et de masse.

La plate-forme de fiabilité Calibre PERC peut lire le fichier UPF pour une conception et exploiter les informations UPF pour effectuer diverses analyses au niveau du transistor, telles que l'identification des décaleurs de niveau manquants ou mal connectés, les conditions de surcharge électrique (EOS), les puits flottants et bien plus encore . En utilisant la plate-forme de fiabilité Calibre PERC en conjonction avec les données UPF, les concepteurs peuvent évaluer les interactions des appareils par programmation pour fournir une vérification de fiabilité répétable et déterministe.

Fiabilité à vie des puces AI/ML

La sécurité opérationnelle est un aspect critique pour la plupart des puces AI/ML, qui devraient fonctionner tout au long de leur durée de vie prévue sans aucun problème ni panne. Certains problèmes de fiabilité électrique, tels que l'instabilité de la température de polarisation (BTI) et l'EOS, peuvent ne pas se manifester par des défaillances immédiates, mais peuvent entraîner une dégradation rapide et un vieillissement au fil du temps s'ils ne sont pas corrigés avant la fabrication. La vérification de la fiabilité peut aider à garantir un fonctionnement robuste sur une période prolongée en vérifiant divers problèmes tels que la résistance point à point, le BTI positif et négatif, la densité de courant et l'électromigration (EM), qui peuvent tous entraîner une dégradation des performances ou une défaillance catastrophique.

Prenons le cas où un dispositif de domaine haute tension pilote un dispositif à oxyde mince qui n'est pas conçu pour gérer la haute tension. Lors de la conception, le concepteur ne parvient pas à insérer un levier de vitesse haut-bas. Même si cette condition n'affectera pas nécessairement la fonctionnalité au début, elle mettra à l'épreuve le dispositif à oxyde mince au fil du temps, provoquant éventuellement une défaillance. Le temps de défaillance réel dépend de la valeur de la tension, du temps pendant lequel l'alimentation est ON par rapport à OFF et des paramètres du processus.

L'EM (migration d'atomes dans un conducteur due au courant électrique) est un autre problème majeur qui affecte la robustesse à long terme des interconnexions utilisées dans les circuits intégrés AI/ML. Cette migration provoque la formation de vides et de buttes sur les fils. Les vides provoquent une augmentation significative de la résistance, tandis que les bosses peuvent créer des courts-circuits, qui entraînent tous deux des pannes de circuit. L'effet EM dépend de nombreux facteurs, tels que la longueur et la largeur de la ligne métallique, le matériau d'interconnexion, la température de fonctionnement, les courants unidirectionnels et bidirectionnels, etc.

Les fonderies fournissent aux entreprises de conception des limites EM pour le courant maximal que les fils peuvent supporter, en fonction des conditions d'utilisation attendues du produit. Par exemple, les limites EM pour un circuit intégré utilisé à l'intérieur d'un téléphone mobile seraient considérablement inférieures à celles d'un circuit intégré utilisé dans un environnement industriel. Certaines entreprises disposent d'équipes dédiées qui collaborent activement avec la fonderie pour définir les spécifications appropriées, créer des structures de test et effectuer la qualification du produit pour la tolérance EM. De toute évidence, il est plus difficile de définir ces limites pour un produit pouvant être utilisé dans plusieurs environnements, de sorte que les concepteurs conçoivent généralement ces puces pour les pires conditions de fonctionnement. Dans tous les cas, il est crucial de tester la conception par rapport aux limites EM définies par la fonderie et de valider que la conception peut résister aux effets EM.

L'incapacité à détecter et à corriger les différents problèmes de fiabilité au cours de la phase de vérification pré-silicium peut entraîner un large éventail d'impacts, notamment plusieurs rotations de bande, des retards dans la mise sur le marché du produit, une perte de confiance des clients, une réaction négative importante du marché, des rappels de produits, voire des conséquences catastrophiques, telles que des blessures corporelles ou la mort. L'identification et la correction des violations de fiabilité avant le retrait du ruban minimisent les risques de dysfonctionnements ou de pannes des circuits qui peuvent s'avérer coûteux.

L'analyse et la gestion de la fiabilité de l'IA/ML sont cruciales

Le succès récent et l'expansion de la fonctionnalité AI/ML reposent en grande partie sur les progrès de la technologie des semi-conducteurs. Au fur et à mesure que ces nouvelles conceptions sont développées, la communauté de conception de matériel doit être consciente de la nécessité d'analyser et de gérer les aspects de fiabilité d'une conception, tels que l'environnement cible, les conditions de fonctionnement, les critères de fiabilité, etc. les problèmes de fiabilité et les exigences spécifiques de ces puces volumineuses et complexes peuvent aider les sociétés de conception à garantir que leurs produits fonctionnent comme prévu tout au long de leur durée de vie. À son tour, cela se traduit par la confiance dans les résultats obtenus grâce à l'utilisation d'applications d'IA/ML sur des marchés plus larges, soutenant leur utilisation et leur expansion continues.

Les articles sur l'industrie sont une forme de contenu qui permet aux partenaires de l'industrie de partager des actualités, des messages et des technologies utiles avec les lecteurs d'All About Circuits d'une manière qui ne convient pas au contenu éditorial. Tous les articles de l'industrie sont soumis à des directives éditoriales strictes dans le but d'offrir aux lecteurs des nouvelles utiles, une expertise technique ou des histoires. Les points de vue et opinions exprimés dans les articles de l'industrie sont ceux du partenaire et pas nécessairement ceux d'All About Circuits ou de ses rédacteurs.

Technologie de l'Internet des objets

- L'importance de la sécurité électrique

- Quel est le rôle de l'ingénieur fiabilité ?

- La clé n°1 du succès de la fiabilité

- L'importance des compétences de base

- Le côté non technique de la fiabilité

- L'importance des tendances en matière de fiabilité des moteurs électriques

- L'importance de l'entretien de routine sur l'équipement

- L'importance de l'usinage rapide dans la fabrication

- L'importance de l'analyse des causes profondes