Niveaux de tension des signaux logiques

Tension d'entrée pour les portes logiques

Les circuits de porte logique sont conçus pour n'entrer et sortir que deux types de signaux :« haut » (1) et « bas » (0), représentés par une tension variable :pleine tension d'alimentation pour un état « haut » et tension nulle pour un état « bas ». Dans un monde parfait, tous les signaux de circuit logique existeraient à ces limites de tension extrêmes et ne s'en écarteraient jamais (c'est-à-dire moins que la pleine tension pour un "haut" ou plus de zéro pour un "bas").

Cependant, en réalité, les niveaux de tension des signaux logiques atteignent rarement ces limites parfaites en raison des chutes de tension parasites dans les circuits du transistor, et nous devons donc comprendre les limites des niveaux de signal des circuits de porte alors qu'ils tentent d'interpréter les tensions de signal se situant quelque part entre pleine tension d'alimentation et zéro.

Tolérance de tension des entrées de porte TTL

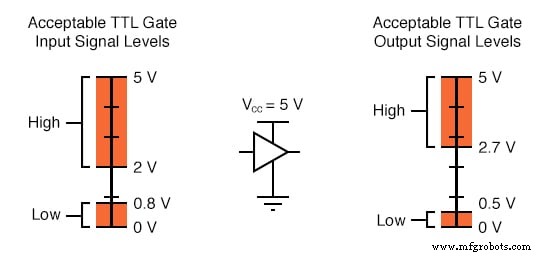

Les portes TTL fonctionnent sur une tension d'alimentation nominale de 5 volts, +/- 0,25 volts. Idéalement, un signal TTL « haut » serait de 5,00 volts exactement et un signal TTL « bas » de 0,00 volts exactement.

Cependant, les vrais circuits de porte TTL ne peuvent pas produire des niveaux de tension aussi parfaits et sont conçus pour accepter des signaux « hauts » et « bas » s'écartant considérablement de ces valeurs idéales.

Les tensions de signal d'entrée « acceptables » vont de 0 volt à 0,8 volt pour un état logique « bas » et de 2 volts à 5 volts pour un état logique « haut ».

Les tensions de signal de sortie « acceptables » (niveaux de tension garantis par le fabricant de la porte sur une plage spécifiée de conditions de charge) vont de 0 volt à 0,5 volt pour un état logique « bas » et de 2,7 volts à 5 volts pour un état logique « haut » :

Si un signal de tension compris entre 0,8 volt et 2 volts devait être envoyé à l'entrée d'une porte TTL, il n'y aurait pas de réponse certaine de la porte. Un tel signal serait considéré comme incertain , et aucun fabricant de portes logiques ne garantirait comment leur circuit de porte interpréterait un tel signal.

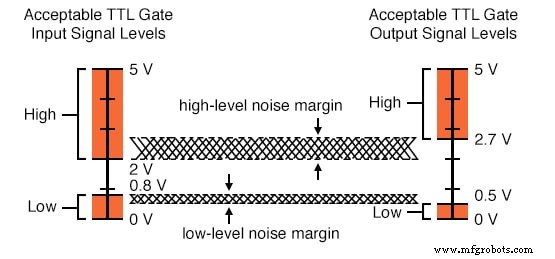

Marge de bruit TTL

Comme vous pouvez le voir, les plages tolérables pour les niveaux de signal de sortie sont plus étroites que pour les niveaux de signal d'entrée, afin de garantir que toute porte TTL émettant un signal numérique dans l'entrée d'une autre porte TTL transmettra des tensions acceptables à la porte de réception. La différence entre les plages de sortie et d'entrée tolérables est appelée la marge de bruit de la porte.

Pour les portes TTL, la marge de bruit de bas niveau est la différence entre 0,8 volt et 0,5 volt (0,3 volt), tandis que la marge de bruit de haut niveau est la différence entre 2,7 volts et 2 volts (0,7 volt). En termes simples, la marge de bruit est la quantité maximale de tension parasite ou de « bruit » qui peut être superposée à un signal de tension de sortie de porte faible avant que la porte de réception ne l'interprète à tort :

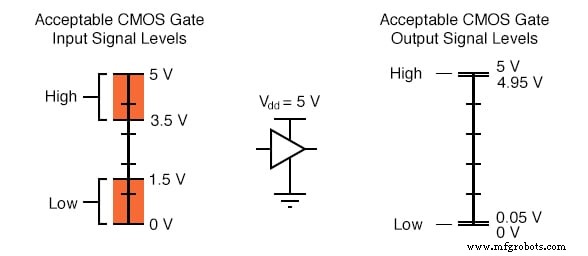

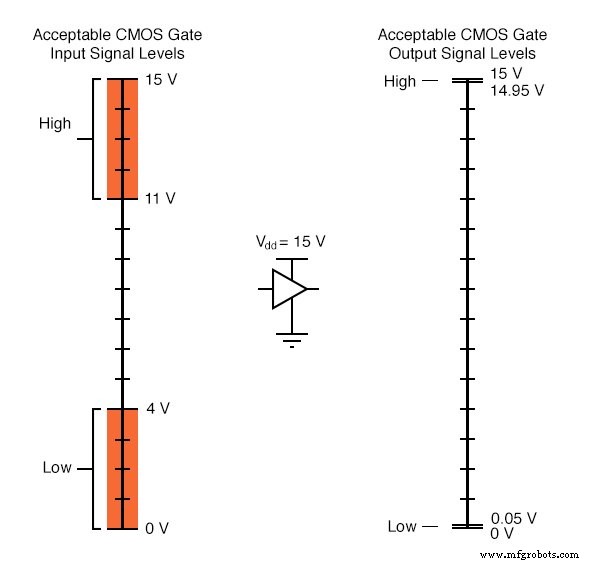

Tolérance de tension des entrées de porte CMOS

Les circuits de porte CMOS ont des spécifications de signal d'entrée et de sortie assez différentes de TTL. Pour une porte CMOS fonctionnant à une tension d'alimentation de 5 volts, les tensions de signal d'entrée acceptables vont de 0 volt à 1,5 volt pour un état logique « bas » et de 3,5 volts à 5 volts pour un état logique « haut ».

Les tensions de signal de sortie « acceptables » (niveaux de tension garantis par le fabricant de la porte sur une plage spécifiée de conditions de charge) vont de 0 volt à 0,05 volt pour un état logique « bas » et de 4,95 volts à 5 volts pour un état logique « élevé » :

Marge de bruit CMOS

Il devrait être évident à partir de ces figures que les circuits de porte CMOS ont des marges de bruit bien plus importantes que TTL :1,45 volts pour les marges de bas niveau et de haut niveau CMOS, contre un maximum de 0,7 volt pour TTL. En d'autres termes, les circuits CMOS peuvent tolérer plus de deux fois la quantité de tension de « bruit » superposée sur leurs lignes d'entrée avant que des erreurs d'interprétation du signal ne se produisent.

Marges de bruit à des tensions de fonctionnement plus élevées

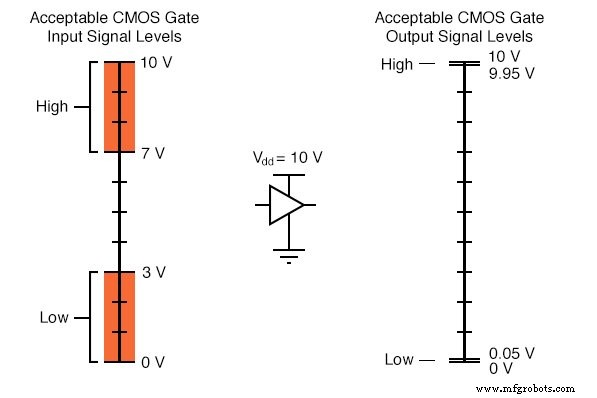

Les marges de bruit CMOS s'élargissent encore plus avec des tensions de fonctionnement plus élevées. Contrairement au TTL, qui est limité à une tension d'alimentation de 5 volts, le CMOS peut être alimenté par des tensions allant jusqu'à 15 volts (certains circuits CMOS allant jusqu'à 18 volts).

Voici les états « haut » et « bas » acceptables, à la fois pour l'entrée et la sortie, des circuits intégrés CMOS fonctionnant à 10 volts et 15 volts, respectivement :

Les marges pour les signaux « élevés » et « faibles » acceptables peuvent être supérieures à ce qui est indiqué dans les illustrations précédentes. Ce qui est affiché représente les performances du signal d'entrée dans le « pire des cas », en fonction des spécifications du fabricant. Dans la pratique, on peut constater qu'un circuit de porte tolérera des signaux « hauts » de tension considérablement moindre et des signaux « faibles » de tension considérablement plus élevée que ceux spécifiés ici.

À l'inverse, les marges de sortie extrêmement faibles indiquées—garantissant les états de sortie pour les signaux « haut » et « bas » à moins de 0,05 volt des « rails » d'alimentation électrique—sont optimistes. De tels niveaux de tension de sortie « solides » ne seront vrais que pour des conditions de charge minimale. Si la porte fournit ou absorbe un courant substantiel vers une charge, la tension de sortie ne pourra pas maintenir ces niveaux optimaux, en raison de la résistance de canal interne des MOSFET de sortie finaux de la porte.

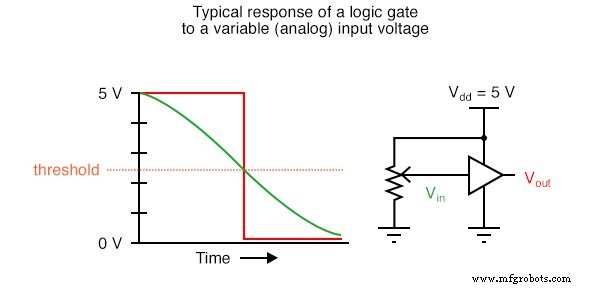

Seuils de tension

Dans la plage « incertaine » pour toute entrée de porte, il y aura un point de démarcation divisant la plage de signal d'entrée « bas » réelle de la porte de sa plage de signal d'entrée « élevée ». C'est-à-dire que quelque part entre le niveau de tension de signal « élevé » le plus bas et le niveau de tension de signal « bas » le plus élevé garanti par le fabricant de la porte, il existe une tension de seuil à laquelle la porte réellement changer son interprétation d'un signal de « bas » ou « haut » ou vice versa. Pour la plupart des circuits de porte, cette tension non spécifiée est un point unique :

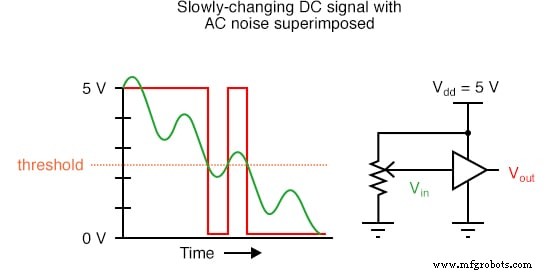

Entrées avec bruit CA

En présence d'une tension de « bruit » CA superposée au signal d'entrée CC, un seul point de seuil auquel la porte modifie son interprétation du niveau logique entraînera une sortie erratique :

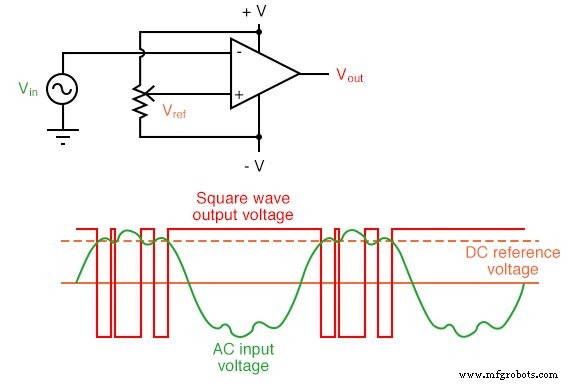

Si ce scénario vous semble familier, c'est parce que vous vous souvenez d'un problème similaire avec les circuits d'amplificateur opérationnel de comparateur de tension (analogique). Avec un seul point de seuil auquel une entrée fait basculer la sortie entre les états « haut » et « bas », la présence d'un bruit important entraînera des changements erratiques dans la sortie :

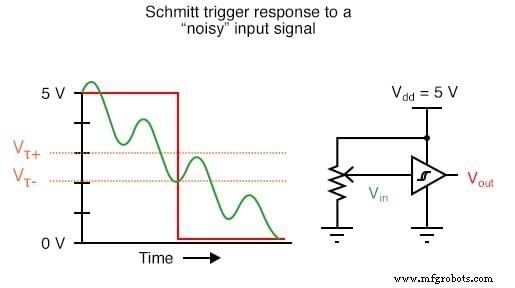

Déclencheur Schmittt

La solution à ce problème est un peu positive rétroaction introduite dans le circuit amplificateur. Avec un ampli-op, cela se fait en connectant la sortie à l'entrée non inverseuse (+) via une résistance.

Dans un circuit de porte, cela implique de reconcevoir les circuits de porte internes, en établissant le retour à l'intérieur du boîtier de porte plutôt que via des connexions externes. Une porte ainsi conçue s'appelle un déclencheur de Schmitt . Les déclencheurs de Schmitt interprètent des tensions d'entrée variables selon deux tensions de seuil :un passant positif seuil (VT+), et un négatif seuil (VT-) :

Hystérésis dans les portes de déclenchement de Schmitt

Les portes de déclenchement de Schmitt se distinguent dans les diagrammes schématiques par le petit symbole "d'hystérésis" dessiné à l'intérieur, rappelant la courbe B-H pour un matériau ferromagnétique. L'hystérésis engendrée par la rétroaction positive dans le circuit de la porte ajoute un niveau supplémentaire d'immunité au bruit aux performances de la porte.

Les portes de déclenchement de Schmitt sont fréquemment utilisées dans les applications où du bruit est attendu sur la ou les lignes de signal d'entrée et/ou où une sortie erratique serait très préjudiciable aux performances du système.

Utilisation des technologies TTL et CMOS dans le même système

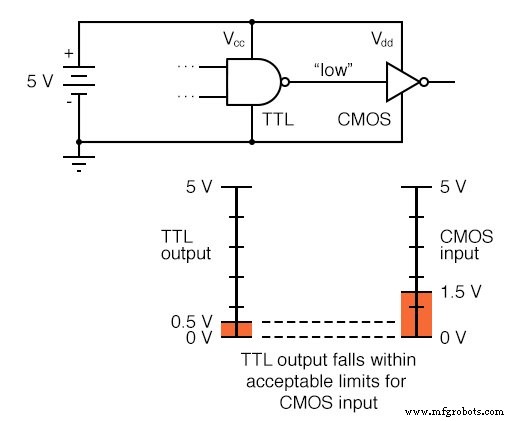

Les exigences de niveau de tension différentes des technologies TTL et CMOS posent des problèmes lorsque les deux types de portes sont utilisés dans le même système. Bien que le fonctionnement des portes CMOS sur la même tension d'alimentation de 5,00 volts requise par les portes TTL ne pose aucun problème, les niveaux de tension de sortie TTL ne seront pas compatibles avec les exigences de tension d'entrée CMOS.

Exemple de circuit combiné TTL et CMOS

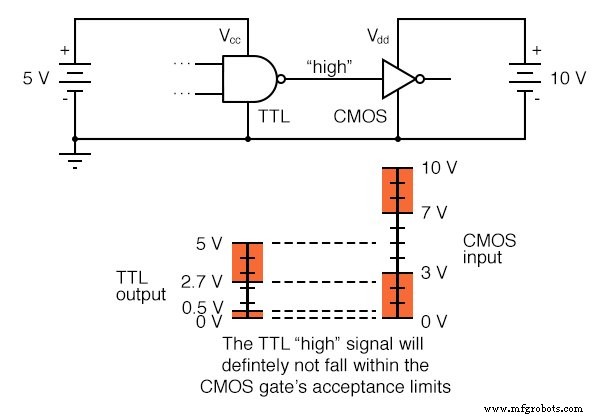

Prenons par exemple une porte TTL NAND délivrant un signal à l'entrée d'une porte inverseuse CMOS. Les deux portes sont alimentées par la même alimentation 5,00 volts (Vcc ). Si la porte TTL émet un signal « bas » (garanti entre 0 volt et 0,5 volt), il sera correctement interprété par l'entrée de la porte CMOS comme un « bas » (en attendant une tension entre 0 volt et 1,5 volt) :

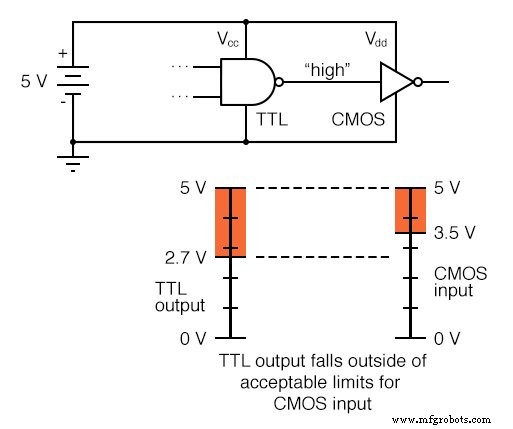

Cependant, si la porte TTL émet un signal « élevé » (garanti entre 5 volts et 2,7 volts), cela pourrait ne pas être correctement interprété par l'entrée de la porte CMOS comme un « haut » (en attendant une tension comprise entre 5 volts et 3,5 volts) :

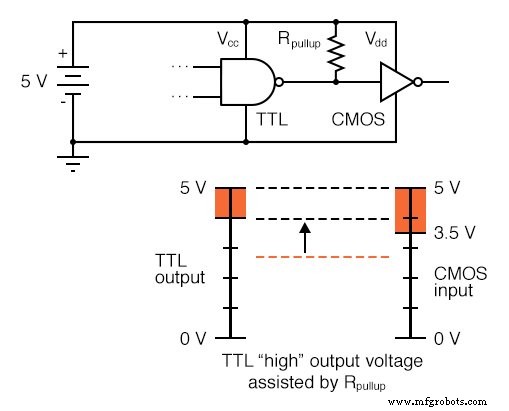

Compte tenu de cette discordance, il est tout à fait possible pour la porte TTL de produire un signal « élevé » valide (valide, c'est-à-dire selon les normes pour TTL) qui se situe dans la plage « incertaine » pour l'entrée CMOS, et peut être ( faussement) interprété comme un « bas » par la porte de réception. Une « solution » simple à ce problème consiste à augmenter le niveau de tension de signal « élevé » de la porte TTL au moyen d'une résistance de rappel :

Quelque chose de plus que cela, cependant, est nécessaire pour interfacer une sortie TTL avec une entrée CMOS, si la porte CMOS de réception est alimentée par une tension d'alimentation plus élevée :

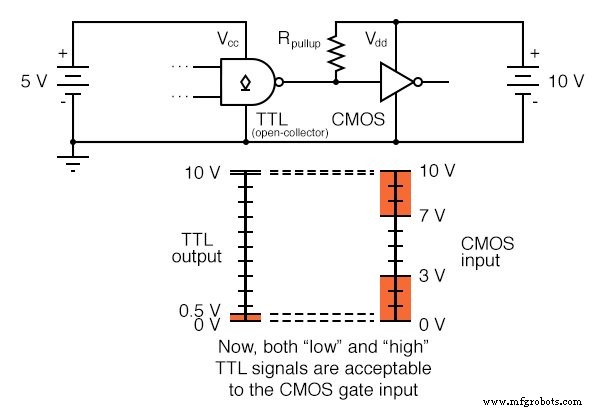

Utilisation d'une porte TTL à collecteur ouvert avec une porte CMOS

Il n'y aura aucun problème avec la porte CMOS pour interpréter la sortie "faible" de la porte TTL, bien sûr, mais un signal "haut" de la porte TTL est une tout autre affaire. La plage de tension de sortie garantie de 2,7 volts à 5 volts à partir de la sortie de la porte TTL est loin de la plage acceptable de la porte CMOS de 7 volts à 10 volts pour un signal « élevé ».

Si nous utilisons un open-collector Porte TTL au lieu d'une porte de sortie totem-pôle, cependant, une résistance de rappel au 10 volts Vdd le rail d'alimentation augmentera la tension de sortie « élevée » de la porte TTL jusqu'à la pleine tension d'alimentation alimentant la porte CMOS. Étant donné qu'une porte à collecteur ouvert ne peut absorber que du courant, pas un courant de source, le niveau de tension d'état « élevé » est entièrement déterminé par l'alimentation à laquelle la résistance de rappel est attachée, résolvant ainsi parfaitement le problème de non-concordance :

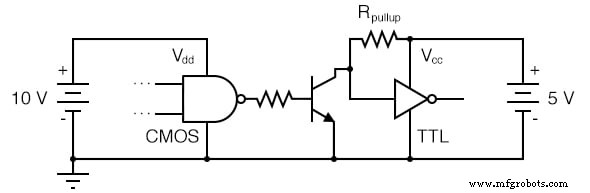

Problèmes d'utilisation de la sortie CMOS vers une entrée TTL

En raison des excellentes caractéristiques de tension de sortie des portes CMOS, il n'y a généralement aucun problème pour connecter une sortie CMOS à une entrée TTL. Le seul problème important est la charge de courant présentée par les entrées TTL, car la sortie CMOS doit absorber du courant pour chacune des entrées TTL lorsqu'elle est à l'état « bas ».

Lorsque la porte CMOS en question est alimentée par une source de tension supérieure à 5 volts (Vcc ), cependant, un problème en résultera. L'état de sortie "haut" de la porte CMOS, étant supérieur à 5 volts, dépassera les limites d'entrée acceptables de la porte TTL pour un signal "haut".

Utilisation d'un circuit onduleur à collecteur ouvert

Une solution à ce problème consiste à créer un circuit inverseur à "collecteur ouvert" à l'aide d'un transistor NPN discret et à l'utiliser pour interfacer les deux portes ensemble :

Le « Rpullup "La résistance est facultative, car les entrées TTL prennent automatiquement un état "élevé" lorsqu'elles sont laissées flottantes, ce qui se produira lorsque la sortie de la porte CMOS est "faible" et que le transistor se coupe. Bien entendu, une conséquence très importante de la mise en œuvre de cette solution est l'inversion logique créée par le transistor :lorsque la porte CMOS sort un signal « bas », la porte TTL voit une entrée « haut »; et lorsque la porte CMOS délivre un signal « haut », le transistor sature et la porte TTL voit une entrée « bas ». Tant que cette inversion est prise en compte dans le schéma logique du système, tout ira bien.

FEUILLE DE TRAVAIL CONNEXE :

-

Feuille de travail sur les signaux logiques numériques

Technologie industrielle