L'optimisation de l'ingénierie des espaceurs pour la DRAM sans condensateur basée sur le transistor à effet tunnel à double porte

Résumé

La DRAM basée sur le FET à effet tunnel à double grille (DGTFET) présente les avantages d'une structure sans condensateur et d'un temps de rétention élevé. Dans cet article, l'optimisation de l'ingénierie des espaceurs pour la DRAM DGTFET est systématiquement étudiée par l'outil Silvaco-Atlas pour améliorer encore ses performances, y compris la réduction du courant de lecture « 0 » et l'extension du temps de rétention. Les résultats de la simulation montrent que les espaceurs côté source et côté drain doivent appliquer respectivement les diélectriques low-k et high-k, ce qui peut améliorer le courant de lecture "1" et réduire le courant de lecture "0". En appliquant cette ingénierie d'entretoise optimisée, la DRAM DGTFET obtient les performances optimales - un courant de lecture « 0 » extrêmement faible (10 −14 A/μm) et un temps de rétention important (10 s), ce qui diminue sa consommation d'énergie statique et son taux de rafraîchissement dynamique. Et la faible lecture du courant « 0 » améliore également son rapport de courant (10 7 ) de la lecture "1" à la lecture "0". De plus, l'analyse de l'évolutivité révèle ses lacunes inhérentes, ce qui offre une direction d'investigation plus approfondie pour la DRAM DGTFET.

Contexte

Avec le rétrécissement de la géométrie de l'appareil, la mémoire vive dynamique (DRAM) à 1 transistor (1T)-1 condensateur (1C) a rencontré des difficultés pour réduire sa taille, car il est difficile pour le condensateur de réduire sa taille [1,2,3] . L'industrie de la mémoire a proposé des méthodes efficaces pour le conditionnement de mémoires à plus haute densité, telles que de nouveaux matériaux et de nouvelles structures de dispositifs [4, 5]. La DRAM 1T avec la structure sans condensateur a été signalée pour la première fois au début des années 90 [6, 7], et elle attire de plus en plus l'attention. Dans la DRAM 1T, l'état 1 (stockage de la porteuse) est obtenu de quatre manières :l'ionisation par impact [8], le transistor à jonction bipolaire [9], l'effet tunnel de bande à bande (BTBT) [10] et l'effet tunnel de porte [11].

Le transistor à effet de champ tunnel (TFET) basé sur le BTBT a été considéré comme une alternative potentielle pour le MOSFET en raison du rapport de commutation plus élevé et du courant à l'état bloqué extrêmement faible [12,13,14]. Les avantages du TFET - faible courant à l'état bloqué et faible dépendance à la température - sont extraordinairement bénéfiques pour la DRAM. En particulier, le faible courant à l'état désactivé peut réduire la lecture du courant « 0 » et la consommation d'énergie statique. À l'heure actuelle, certains groupes travaillent sur l'étude de la DRAM TFET [15,16,17,18,19,20]. Il est rapporté que la DRAM TFET a un courant de lecture « 0 » faible et un temps de rétention (RT) élevé. Parmi ces DRAM TFET, la DRAM TFET à double grille (DGTFET) est la plus importante [19, 20]. Dans la DRAM DGTFET, les opérations d'écriture et de lecture sont basées sur le BTBT. La recherche montre que la lecture du courant « 0 » de la DRAM DGTFET peut atteindre 1 nA/μm, ce qui est bien inférieur à celui de la DRAM 1T1C traditionnelle. Et le RT de 2 s est de loin supérieur à la valeur cible de 64 ms qui est généralement définie sur le temps de rafraîchissement dynamique dans le système informatique [21]. Le RT de la DRAM DGTFET est toujours supérieur à 300 ms lorsque la température est augmentée à 85 °C, ce qui autorise sa praticabilité dans les conditions difficiles. De plus, dans la DRAM DGTFET, l'élimination des condensateurs de plus grande taille montre également sa compétitivité dans les boîtiers haute densité. Ces avantages indiquent pleinement qu'il est nécessaire d'étudier la DRAM DGTFET. Bien que ces recherches aient démontré que le DGTFET a des performances supérieures à celles de la DRAM 1T1C conventionnelle, les résultats (RT et lecture du courant « 0 ») ne sont pas optimaux en raison du fait que la configuration de l'appareil du DGTFET n'est pas optimisée.

Dans cet article, l'ingénierie de l'espaceur du DGTFET est optimisée pour que le DGTFET obtienne des performances optimales. Dans les TFET, les diélectriques espaceurs ont de fortes influences sur le BTBT [22, 23]. Dans le DGTFET, les espaceurs côté source et côté drain sont fermés aux jonctions tunnel, de sorte qu'ils affectent grandement les performances du DGTFET DRAM. Cet article analyse systématiquement les influences du diélectrique d'espacement (diélectriques à faible k ou à k élevé) dans chaque espaceur sur DGTFET DRAM et propose une ingénierie d'espaceur optimisée. Par l'optimisation de l'ingénierie des espaceurs, le courant de lecture « 0 » est abaissé à 10 −14 A/μm, et RT peut atteindre 10 s. Enfin, l'évolutivité de la DRAM DGTFET avec l'ingénierie optimisée des espaceurs est également abordée dans ce travail.

Structure de l'appareil et méthode de simulation

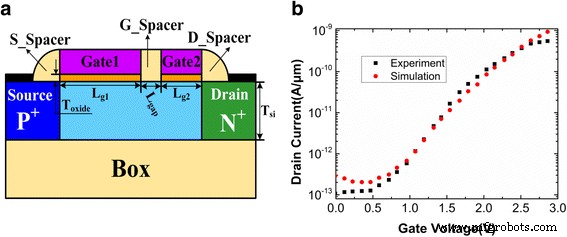

Le DGTFET avec une configuration P-I-N est illustré à la Fig. 1a. Les régions source et drain sont P + dopage (10 20 /cm 3 ) et N + dopage (10 20 /cm 3 ), respectivement. La région de canal intrinsèque est divisée en deux parties :la région Gate1 avec le N + polysilicium et région Gate2 avec le P + polysilicium. Il y a un court espace entre le Gate1 et le Gate2. Le P + le polysilicium Gate2 peut créer et maintenir le puits physique pour le stockage de charge et remplacer la DRAM conventionnelle basée sur TFET qui utilise un P + région de poche comme zone de stockage. Tandis que pour un N + polysilicium Gate1, la concentration de trous dans la région sous-jacente entre Gate1 et Gate2 est faible, ce qui est utile pour l'opération de lecture. Ainsi, un P + polysilicon Gate2 a été choisi pour créer une région de stockage plus profonde qui pourrait faciliter un temps de rétention plus long, tandis qu'un N + le polysilicium Gate1 est sélectionné pour contrôler le mécanisme d'effet tunnel pendant l'opération de lecture [20]. Sur la figure 1a, le S_Spacer et le D_Spacer se réfèrent aux espaceurs des côtés source et drain, respectivement. Le G_spacer fait référence à l'entretoise entre Gate1 et Gate2. Le matériau par défaut des entretoises est SiO2 . Les paramètres par défaut de l'appareil sont les suivants :épaisseur du film de silicium (Tsi ) est de 20 nm, la longueur du Gate1 (Lg1 ) est de 400 nm, la longueur du Gate2 (Lg2 ) est de 200 nm, la longueur de l'intervalle de grille (Lgap ) est de 50 nm, et l'épaisseur de l'oxyde de grille HfO2 (Toxyde ) est de 3 nm.

un Schéma d'une cellule DRAM TFET à double grille (DGTFET). b Comparaison entre la caractéristique de transfert simulée et les résultats expérimentaux pour SOI TFET [25]

Les simulations de la DRAM DGTFET sont réalisées dans Silvaco Atlas en utilisant un modèle BTBT non local. Le modèle d'effet tunnel BTBT non local prend en compte la variation spatiale des bandes d'énergie et la génération/recombinaison du type de porteur opposé [24]. Les paramètres du modèle tunnel sont calibrés selon les résultats expérimentaux du SOI TFET [25]. La masse du tunnel d'électrons et de trous est ajustée à 0,22 m0 et 0,52m0 , respectivement, où m0 est la masse au repos de l'électron. La caractéristique de transfert simulé du SOI TFET est cohérente avec les résultats expérimentaux, comme le montre la figure 1b, qui autorise les modèles appliqués dans cet article. En raison du dopage important dans les régions de source et de drain, le modèle de rétrécissement de la bande interdite et les statistiques de Fermi-Dirac sont également pris en compte. En outre, la recombinaison Shockley-Read-Hall ainsi que les modèles de mobilité dépendant du dopage et du champ électrique sont également appliqués. Tous les paramètres du modèle sont cohérents avec ceux de [19, 20]. Étant donné que la durée de vie de la porteuse régit la génération/la recombinaison de la porteuse pendant l'opération de maintien, elle influence le RT de la DRAM DGTFTET. Selon les différentes durées de vie des porteurs variant entre 1 μs et 10 ns dans [26,27,28], les durées de vie des électrons et des trous sont fixées à 100 ns. La relation de Scharfetter et les modèles de Schenk sont utilisés pour inclure respectivement le dopage et la dépendance à la température de la durée de vie.

Résultats et discussion

Mécanisme d'exploitation

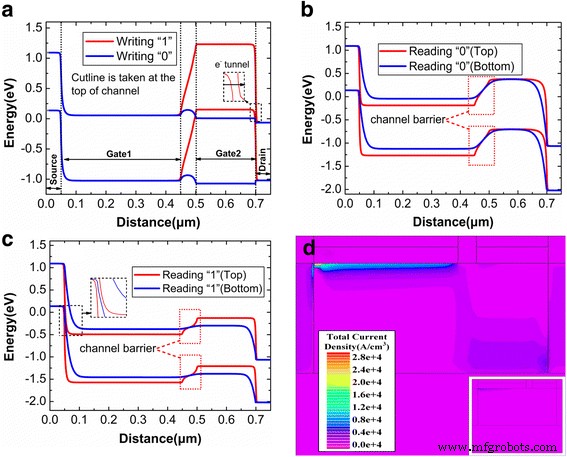

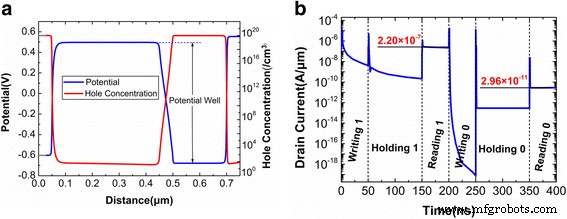

Dans la DRAM DGTFET, les opérations d'écriture et de lecture sont contrôlées par BTBT au niveau des jonctions tunnel de drain et de source, respectivement. La figure 2 montre les bandes d'énergie au cours des différentes opérations. Comme le montre la figure 2a, lors de l'écriture "1", la Gate2 avec une polarisation négative augmente considérablement la bande d'énergie du canal sous Gate2 de sorte qu'une barrière tunnel extrêmement petite est créée du côté drain. Ainsi, les électrons tunnel vers le côté drain et les trous sont accumulés dans le puits de potentiel profond (1,2 V), comme le montre la figure 3a. Lors de l'écriture « 0 », la Gate2 avec un biais positif fait expulser les trous de ce puits de potentiel et se recombiner côté drain [29]. La figure 2b, c montre les bandes d'énergie après avoir lu respectivement « 1 » et « 0 ». La figure 2b illustre qu'il existe une barrière de canal entre Gate1 et Gate2, mais celle-ci n'existe pas au bas du canal. En outre, la distance d'effet tunnel du côté source est plus petite en haut du canal. Cela démontre qu'un chemin de conduction incliné (de l'interface avant pour Gate1 à l'interface arrière pour Gate2) est formé pendant la lecture "1", ce qui peut également être démontré par la densité de courant de la figure 2d. Pendant la lecture « 0 », la barrière de canal évidente peut être trouvée sur la figure 2c, qui retient le courant de lecture « 0 ». L'encart de la figure 2d montre que les électrons tunnelés à partir de la région source ne peuvent pas traverser cette barrière de canal pour former le courant de lecture « 0 » le plus élevé.

Bandes d'énergie de la source au drain. un Bandes d'énergie après avoir écrit "1" avec un biais Gate2 négatif et après avoir écrit "0" avec un biais Gate2 positif. b Bandes d'énergie en haut et en bas du canal après avoir lu « 1 ». c Bandes d'énergie en haut et en bas du canal après la lecture de « 0 ». d Densité de courant totale après lecture de "1"

un Concentration de potentiel et de trous à la surface du canal après avoir écrit « 1 ». b Réponse transitoire du courant de drain pour la DRAM DGTFET exploitée dans le tableau 1

Une condition de programmation correcte est importante pour la DRAM DGTFET. Un biais négatif plus important doit être appliqué à Gate2 afin que le BTBT saturé soit induit lors de l'écriture "1". Pendant le maintien de « 1 », un petit biais négatif est appliqué à Gate2 pour conserver les trous dans le puits de potentiel pendant une longue période. Pour les opérations de lecture, le biais Gate1 plus élevé renforce le BTBT lors de la lecture « 1 », mais ce qui est préjudiciable à la lecture du courant « 0 ». Le Gate2 avec la polarisation appropriée peut non seulement améliorer le courant de lecture « 1 », mais peut également affaiblir le courant de lecture « 0 ». En appliquant la condition de programmation optimisée du tableau 1, la réponse transitoire de la DRAM DGTFET avec les paramètres par défaut est illustrée à la figure 3b. Les temps d'écriture et de lecture ainsi que les temps de maintien sont respectivement définis sur 50 ns et 100 ns. Le rapport actuel obtenu de la lecture "1" à la lecture "0" est d'environ 10 4 , qui est le même que celui de [17, 19, 20].

Impact des diélectriques d'espacement

Dans la DRAM DGTFET, l'utilisation de diélectriques à faible k ou à k élevé dans trois espaceurs (S_Spacer, G_Spacer et D_Spacer) influencera ses performances. Dans cette conception, les diélectriques low-k et high-k choisissent le SiO2 et HfO2 , respectivement. Si chaque espaceur utilise SiO2 ou HfO2 , il y aura huit combinaisons d'ingénierie d'entretoise. Pour une analyse plus complète, les propriétés de performance de la DRAM DGTFET avec chaque combinaison, y compris la lecture « 1 » (I 1 ) et « 0 » (I 0 ) courants ainsi que rapport de courant (I 1 / Je 0 ), sont extraits des réponses transitoires, comme indiqué dans le tableau 2. Afin d'évaluer le RT, ces paramètres sont également extraits lorsque le temps de maintien est augmenté à 2 s, ce qui sera discuté dans les sections suivantes. Dans le tableau 2, les lettres « S » et « H » représentent SiO2 et HfO2 , respectivement, et trois lettres de chaque abréviation représentent respectivement S_Spacer, G_Spacer et D_Spacer.

À partir du tableau 2, l'ingénierie optimale de l'entretoise peut être sélectionnée. Le Je 1 sont environ 10 -7 A/μm et 10 −9 A/μm lorsque le SiO2 et HfO2 sont utilisés dans S_Spacer, respectivement. Lorsque le D_Spacer applique le HfO2 , le Je 0 est faible à environ 10 −14 A/μm. Par conséquent, la configuration d'espacement optimale de la DRAM DGTFET est que des diélectriques à faible k et à k élevé doivent être utilisés du côté source et drain. Les raisons spécifiques seront analysées systématiquement dans les sections suivantes.

Impacts du diélectrique S_Spacer

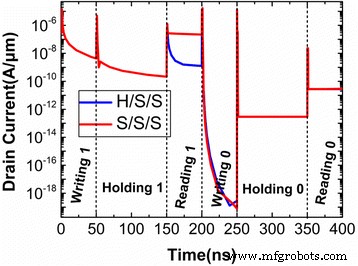

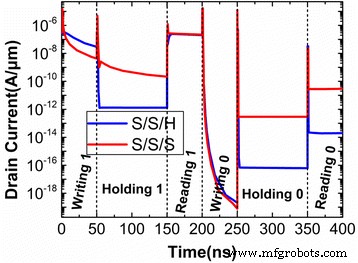

Afin d'analyser les influences de S_Spacer, les réponses transitoires des courants de drain pour H/S/S et S/S/S sont comparées sur la Fig. 4. On peut observer que la lecture du courant « 1 » est améliorée d'environ deux ordres de grandeur lorsque le SiO2 est choisi comme diélectrique S_Spacer.

Réponses transitoires des courants de drain pour H/S/S et S/S/S exploités dans le tableau 1

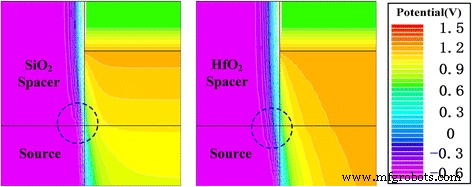

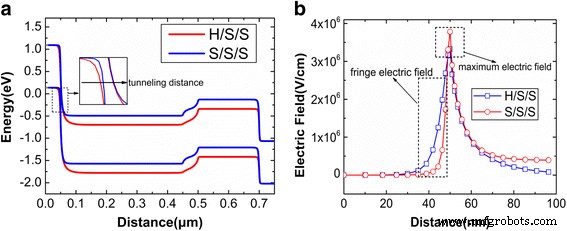

La figure 5 montre les contours potentiels de S/S/S et H/S/S. Au niveau de la jonction tunnel source, la région d'appauvrissement de surface de H/S/S est évidemment étendue par rapport à celle de S/S/S, comme le montre le cercle de la figure 5. La région d'appauvrissement de surface étendue augmente la largeur de la barrière tunnel. La figure 6a montre les bandes d'énergie après la lecture de « 1 ». Comme le montre la région agrandie locale de cette figure, la distance de tunnel (voir les flèches) du H/S/S est évidemment plus grande que celle du S/S/S, ce qui est causé par la région d'épuisement de la surface étendue. En outre, après avoir lu « 1 », le champ électrique au sommet de la jonction à effet tunnel de la source est représenté sur la figure 6b. On peut trouver que le champ électrique de frange de H/S/S est plus grand que celui de S/S/S, ce qui est la principale raison de l'extension de la région d'appauvrissement en surface. En un mot, S_Spacer avec high-k (HfO2 ) le diélectrique génère le plus grand champ électrique de frange de sorte que la région d'appauvrissement de surface au niveau de la jonction tunnel source est étendue, ce qui augmente la distance tunnel des électrons et diminue le courant de lecture « 1 ». En outre, on peut également trouver à partir de la figure 6b que le champ électrique maximum de S/S/S est plus grand que celui de H/S/S. La relation exponentielle entre le taux BTBT et le champ électrique rend le courant tunnel de S/S/S beaucoup plus grand que celui de H/S/S [30]. Par conséquent, le S_Spacer avec le diélectrique à faible k (SiO2 ) est bénéfique à la lecture du courant « 1 ».

Contours potentiels du S/S/S (à gauche) et H/S/S (à droite) après lecture du « 1 »

un Bande d'énergie de la source au drain et b champ électrique au sommet de la jonction tunnel source

Sur la figure 6a, le diélectrique S_Spacer a également un impact sur la bande d'énergie de la région du canal. Sur la figure 6b, le champ électrique de S/S/S est plus grand dans la région du canal, de sorte que son potentiel de canal est inférieur à celui de H/S/S. En conséquence, le niveau d'énergie le plus élevé peut être trouvé dans S/S/S. Mais cela ne peut pas avoir d'effets sur la barrière tunnel et la lecture du courant "1".

Impacts du diélectrique D_Spacer

Par la suite, le D_Spacer est également étudié dans cet article. Garder le S_Spacer et le G_Spacer constants (SiO2 est utilisé dans ces deux espaceurs), les différents courants de drain transitoires provoqués par les différents diélectriques D_Spacer sont illustrés sur la Fig. 7. Hormis la lecture « 1 » et l'écriture « 0 », les autres opérations dépendent manifestement du diélectrique D_Spacer. C'est parce que D_Spacer est loin du chemin de conduction de lecture "1" (bas de canal sous la Gate2). On peut apprendre du mécanisme de fonctionnement précédent que les opérations d'écriture et de maintien sont régies par Gate2, donc le diélectrique D_Spacer peut apporter les influences sur ces deux opérations.

Réponses transitoires des courants de drain pour S/S/H et S/S/S exploités dans le tableau 1

Lors de l'opération de maintien, les trous accumulés lors de l'écriture « 1 » sont retirés du puits de potentiel et recombinés côté drain. Ainsi, le courant de maintien « 1 » provient principalement du courant de recombinaison SRH. En raison de la plus grande contrôlabilité de Gate2 sur le canal en S/S/S, S/S/S a le taux de recombinaison le plus élevé et le courant de maintien « 1 ». Mais il est bien inférieur au courant BTBT lors de la lecture de "1", donc le courant de maintien "1" plus élevé ne peut pas être reflété dans la lecture du courant "1".

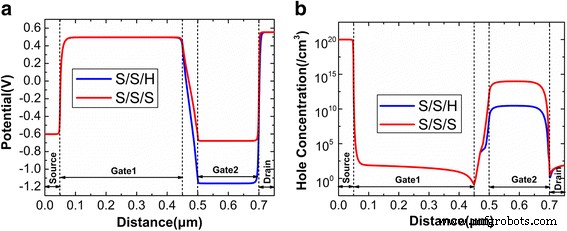

Lors de l'écriture « 1 », le diélectrique D_Spacer influence significativement la profondeur de potentiel du puits. Le contour potentiel de la figure 8a montre que D_Spacer avec HfO2 diélectrique crée un puits de potentiel plus profond. Cela implique que le BTBT effectif entre le drain et le canal s'étend dans la région plus profonde du canal. Par conséquent, le courant d'écriture « 1 » de S/S/H est supérieur à celui de S/S/S. Pendant le maintien à "0", bien qu'un petit biais négatif (− 0,2 V) soit appliqué à Gate2, il peut également monter la bande d'énergie du canal sous Gate2, ce qui induit le BTBT côté drain. Grâce à l'analyse précédente, on peut apprendre que D_Spacer avec SiO2 Le diélectrique améliore le BTBT à la jonction tunnel du drain pendant le maintien de « 0 », ce qui peut être démontré par la concentration de trous plus élevée pour S/S/S, comme le montre la figure 8b. Par conséquent, le D_Spacer avec SiO2 les résultats diélectriques dans le courant de maintien « 0 » plus élevé.

un Contour potentiel après avoir écrit « 1 ». b Concentration du trou après avoir maintenu « 0 »

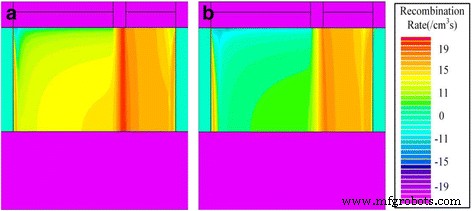

Lors de la lecture de « 0 », parce que la barrière de canal entre Gate1 et Gate2 empêche les électrons de s'écouler vers le côté drain, la différence de lecture du courant « 0 » pour S/S/H et S/S/S est principalement causée par le courant de recombinaison . Plus il y a de trous accumulés pendant le maintien de « 0 » pour S/S/S, de sorte que la bande d'énergie de chute rend le taux de recombinaison de S/S/S plus grand que celui de S/H/S pendant la lecture de « 0 », comme indiqué dans la Fig. 9. Par conséquent, lorsque le D_Spacer utilisant SiO2 , le courant de lecture « 0 » plus élevé doit être attribué au courant de recombinaison plus élevé, qui est causé par le plus grand nombre de trous accumulés pendant le maintien de « 0 ».

Taux de recombinaison de a S/S/S et b S/S/H après avoir lu "0"

En résumé, l'ingénierie d'espacement optimale pour la DRAM DGTFET est que les espaceurs des côtés source et drain doivent appliquer les diélectriques à faible k et à k élevé, respectivement. On peut voir dans le tableau 2 que G_Spacer n'a aucune influence sur la DRAM DGTFET lorsque les autres espaceurs restent inchangés. En effet, les BTBT dominant les opérations d'écriture et de lecture sont exempts de l'influence de G_Spacer.

Durée de rétention

Comme expliqué précédemment, la recombinaison et la génération de trous lors du maintien « 1 » et « 0 » dégradent respectivement l'état « 1 » et « 0 ». En conséquence, il est nécessaire d'étudier la dégradation des performances de la DRAM DGTFET au plus long temps de maintien. Dans le tableau 2, le I 1 et Je 0 se dégradent fortement avec l'augmentation du temps de maintien. Dans tous les appareils, I 1 /Je 0 est toujours supérieur à 10 4 pour appareil avec ingénierie d'entretoise optimale (S/S/H et S/H/H) lorsque le temps de maintien atteint 2 s.

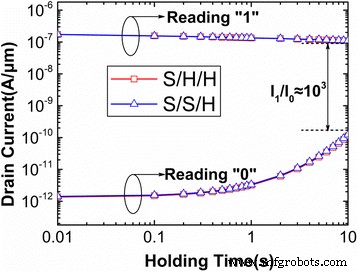

Généralement, le temps de maintien nécessaire pour réduire la marge de détection maximale (différence entre I 1 et Je 0 ) de 50 % est évalué comme RT. Dans cette conception, un RT plus strict est défini comme le temps de maintien maximum lorsque le I 1 /Je 0 est supérieur à 10 3 . La figure 10 montre la variation du courant de lecture avec le temps de maintien pour S/S/H et S/H/H. On peut constater que le rapport actuel de S/H/S et S/H/H est aussi élevé que 10 3 lorsque le temps de maintien atteint 10 s. En conséquence, la RT de la DRAM DGTFET avec une ingénierie d'espacement optimale peut atteindre 10 s. Ceci est bien supérieur à la valeur cible de 64 ms. Le tableau 3 compare les propriétés de performance de ce travail avec celles de [17,18,19,20]. En [19, 20], le ratio actuel n'est que de 10 2 , et le RT est bien inférieur à 10 s. De plus, le courant de lecture « 0 » dans ce travail est inférieur de deux ordres de grandeur à celui de [19, 20]. Les résultats de l'expérience sur les DRAM TFET FD-SOI montrent également que leur courant de lecture « 0 » et RT sont inférieurs à ceux de ce travail. Cette performance supérieure montre que le DGTFET est un substitut à la DRAM à faible consommation. L'optimisation de l'ingénierie des espaceurs permet à la DRAM DGTFET d'obtenir un faible courant de lecture « 0 » et un RT élevé, ce qui est utile pour la réduction de la consommation d'énergie statique et dynamique.

Variation du courant de lecture avec le temps de maintien pour S/S/H et S/H/H

Scalabilité de la DRAM DGTFET

Bien que la DRAM DGTFET résolve le problème de la densité des cellules mémoire en raison de l'élimination du condensateur de grande taille, il est nécessaire d'étudier son évolutivité. L'objectif de l'évolutivité est de maintenir un RT supérieur à 2 s. Le tableau 4 extrait les propriétés de performance de S/S/H avec la diminution de L g1 , L g2 , et L écart . Dans le tableau 4, les trois nombres de chaque abréviation représentent L g1 , L écart , et L g2 .

D'après le tableau 4, on peut observer que I 1 diminue extrêmement lorsque le Lg1 réduit à 100 nm au lieu de 200 nm. La mise à l'échelle de Lg1 au-delà de 100 nm, la barrière induite par le type n rétrécit, ce qui entraîne une contrôlabilité réduite de la porte et une I dégradée 1 . Le Je 0 augmente significativement avec la diminution de L g1 et L g2 . La réduction de L g2 diminue la largeur de la barrière de canal entre Gate1 et Gate2, ce qui encourage une partie des électrons à traverser la barrière pour former le I supérieur 0 . De plus, la réduction continue de L g1 affaiblit la capacité de Gate1 à restreindre l'effet tunnel des électrons à la surface du canal lors de la lecture de « 0 ». Dans le tableau 4, le L écart n'a pas d'influence évidente sur le I 1 , mais le Je 0 augmente légèrement avec la diminution du L écart . Réduire L écart en dessous de 20 nm permet un tunnelage plus important vers Gate2, dégradant ainsi l'état « 0 », réduisant ainsi le temps de rétention.

Afin de garantir que le I 1 /Je 0 et le temps de rétention sont supérieurs à 10 2 et 2 s, respectivement, le L minimum g1 , L g2 , et L écart sont considérés comme 200, 150 et 20 nm, respectivement. Cette taille minimale de périphérique est légèrement inférieure à celle de [17,18,19,20], comme indiqué dans le tableau 3. Cependant, la taille minimale de la DRAM DGTFET est toujours supérieure à celle de la DRAM 1T1C du nœud 20 nm/18 nm [31 ], qui est le défaut inhérent à la DRAM DGTFET. Mais ses avantages sans condensateur, faible puissance et RT élevé ne peuvent être ignorés à l'aide de l'optimisation de l'ingénierie des espaceurs. La réduction de la taille de la DRAM DGTFET au-delà de 100 nm sera au cœur de nos travaux à l'avenir.

Conclusions

Dans cet article, l'optimisation de l'ingénierie des espaceurs pour DGTFET DRAM est étudiée par l'outil Silvaco-Atlas. Les espaceurs côté source et côté drain ont les principales influences sur les performances de la DRAM DGTFET. Le champ électrique de frange élargi par l'espaceur de source avec HfO2 rend la région d'appauvrissement de surface étendue au niveau de la jonction tunnel source, ce qui diminue le courant de lecture « 1 ». Lorsque le SiO2 le diélectrique est utilisé dans l'espaceur de drain, le BTBT plus fort induit plus de trous pendant le maintien de "0", ce qui améliore le courant de recombinaison pendant la lecture de "0". Par conséquent, l'ingénierie optimale des espaceurs consiste à utiliser des diélectriques à faible k et à k élevé dans les espaceurs de drain et de source, respectivement. Grâce à l'optimisation de l'ingénierie des espaceurs, la DRAM DGTFET obtient des avantages importants :un courant de lecture « 0 » extrêmement faible et un temps de rétention plus élevé (10 s) par rapport à d'autres travaux connexes. De plus, l'analyse de l'évolutivité révèle que la taille minimale de son appareil est toujours plus grande que celle de la dernière DRAM 1T1C de nœud 20 nm/18 nm. Cette lacune inhérente indique que la réduction de la taille de la DRAM DGTFET au-delà de 100 nm sera au centre de nos travaux pour la DRAM DGTFET à l'avenir.

Abréviations

- DGTFET :

-

Transistor à effet de champ à effet tunnel à double grille

- DRAM :

-

Mémoire vive dynamique

Nanomatériaux

- Le transistor unijonction (UJT)

- Idées de projets basés sur des capteurs pour les étudiants en dernière année d'ingénierie

- Principes d'ingénierie de la fiabilité pour l'ingénieur d'usine

- Les scientifiques d'IBM inventent un thermomètre pour l'échelle nanométrique

- La valeur du découpage en nuage et de la gestion de fichiers pour l'impression 3D

- Le meilleur niveau d'optimisation et d'organisation dans l'usine intelligente

- Comment trouver les solutions d'ingénierie personnalisées que vous recherchez

- Un manque de diversité peut être à l'origine du manque croissant de compétences dans l'industrie

- Merci pour les souvenirs!