Conception embarquée avec FPGA :implémentation

La disponibilité de FPGA plus puissants et d'environnements de programmation plus efficaces a rendu l'implémentation FPGA largement accessible, mais l'utilisation de FPGA peut sembler intimidante.

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

Note de l'éditeur :alors que des algorithmes avancés continuent d'émerger pour la conception de produits intelligents, les développeurs ont souvent du mal à mettre en œuvre des systèmes embarqués capables de répondre aux demandes de traitement associées de ces algorithmes. Les FPGA peuvent fournir les performances requises, mais la conception avec des FPGA a longtemps été considérée comme limitée aux experts en programmation FPGA. Aujourd'hui, cependant, la disponibilité de FPGA plus puissants et d'environnements de développement plus efficaces a rendu le développement de FPGA largement accessible. Dans cet extrait, chapitre 4 du livre Architecting High-Performance Embedded Systems, l'auteur propose une revue complète des périphériques FPGA, des langages d'implémentation et du processus de développement FPGA, ainsi qu'une procédure détaillée sur la façon de commencer à implémenter des FPGA dans votre propre conception. L'extrait complet est présenté dans la série de fascicules suivante :

1 :ressources matérielles

2 :Langages d'implémentation

3 :Processus de développement

4 : Créer un projet

5 :Implémentation (cet article)

Adapté de Architecting High-Performance Embedded Systems, par Jim Ledin.

Test du comportement logique

Il est important de tester le comportement de la logique en utilisant la simulation avant d'essayer de l'exécuter dans le FPGA. En effet, il est beaucoup plus facile de détecter et de résoudre les problèmes dans l'environnement de simulation qu'avec la logique s'exécutant à l'intérieur du FPGA. Les outils de simulation Vivado font un très bon travail de représentation du comportement du circuit :

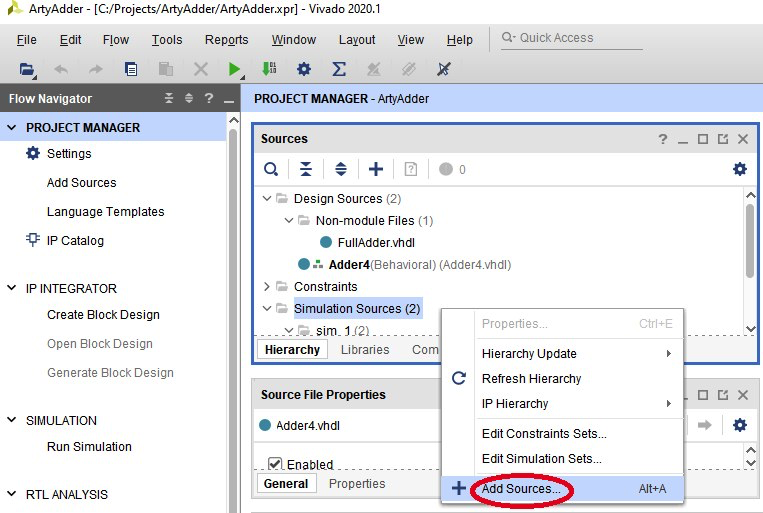

- Dans les Sources sous-fenêtre, faites un clic droit sur Sources de simulation et sélectionnez Ajouter des sources… :

Figure 4.18 – Sélection du menu Ajouter des sources… pour les sources de simulation

- Dans Ajouter des sources dialogue, assurez-vous d'Ajouter ou créer des sources de simulation est sélectionné, puis cliquez sur Suivant .

- Dans Ajouter ou créer des sources de simulation boîte de dialogue, cliquez sur Créer un fichier .

- Entrez le nom du fichier vhdl et cliquez sur OK .

- Cliquez sur Terminer pour ignorer le Ajouter ou créer des sources de simulation boîte de dialogue, puis cliquez sur OK dans le Définir le module dialogue et cliquez sur Oui lorsqu'on vous demande si vous êtes sûr de vouloir les utiliser

- Double-cliquez sur Adder4 TestBench (Comportemental) (Adder4TestBench.vhdl) sous Sources de simulation . Supprimez le contenu automatiquement renseigné du vhdl fenêtre de l'éditeur et entrez le code suivant dans Adder4TestBench.vhdl éditeur :

Ce code exerce la fonctionnalité d'additionneur 4 bits en présentant toutes les combinaisons de nombres 4 bits à chacun des A4 et B4 entrées vers Adder4 composant. Il compare le SUM4 et C_OUT4 sorties du Adder4 composante aux valeurs calculées indépendamment pour les mêmes entrées. Après chaque opération d'ajout, l'erreur le signal est mis à 0 si Adder4 les sorties correspondent aux valeurs attendues ou sont définies sur 1 s'il y a une discordance.

Le code dans Adder4TestBench.vhdl ressemble au code logiciel traditionnel dans la façon dont il utilise des boucles for imbriquées pour appliquer toutes les combinaisons d'entrée de test à l'Adder4 composant à tester. Le code qui exécute des tests en mode simulation n'est pas synthétisable, ce qui signifie qu'il ne représente pas purement un circuit logique matériel et est capable d'opérations logicielles traditionnelles, telles que l'exécution itérative de pour boucles.

Cependant, comme dans les circuits physiques, les signaux auxquels sont attribuées des valeurs dans le code du banc d'essai à l'aide de l'opérateur <=ne peuvent pas être utilisés au même instant dans les expressions suivantes. En effet, l'environnement de simulation représente les effets réels du délai de propagation, qui est important même au sein de minuscules dispositifs FPGA. Les trois attendent 1 ns; instructions dans les opérations du circuit de pause du code du banc d'essai pour tenir compte du délai de propagation. Ces délais de 1 ns donnent du temps aux valeurs de signal calculées juste avant l'attente à se propager afin qu'ils puissent être utilisés dans l'instruction suivante. La dernière attendre 7 ns; L'instruction dans la boucle interne est une pause qui nous permet de voir clairement les résultats de chaque itération des boucles de simulation dans l'affichage de la trace du signal.

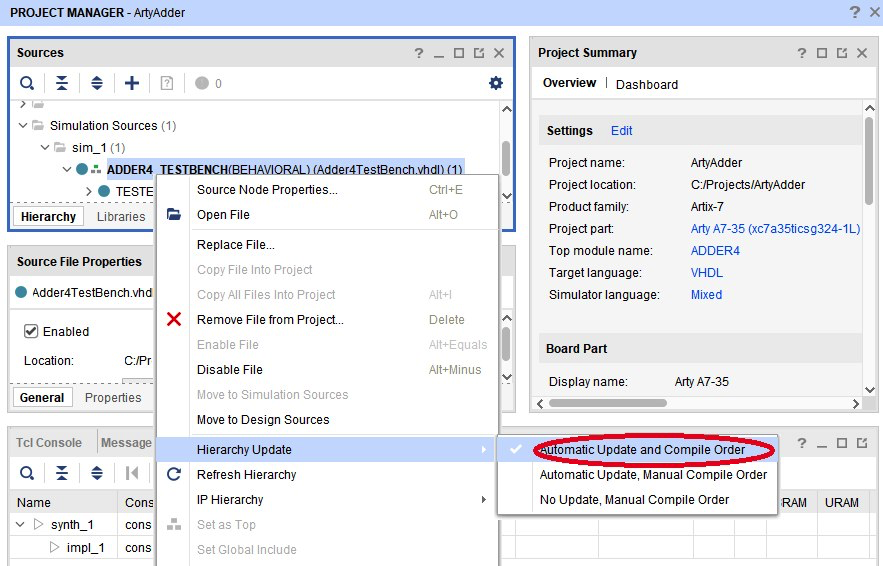

- Clic droit sur Adder4 TestBench (Comportemental) (Adder4TestBench.vhdl) sous Sources de simulation et sélectionnez Mise à jour automatique et ordre de compilation . Cela définit ADDER4_TESTBENCH comme objet de niveau supérieur pour l'exécution de la simulation :

Figure 4.19 – Sélection du menu pour définir la mise à jour automatique et l'ordre de compilation

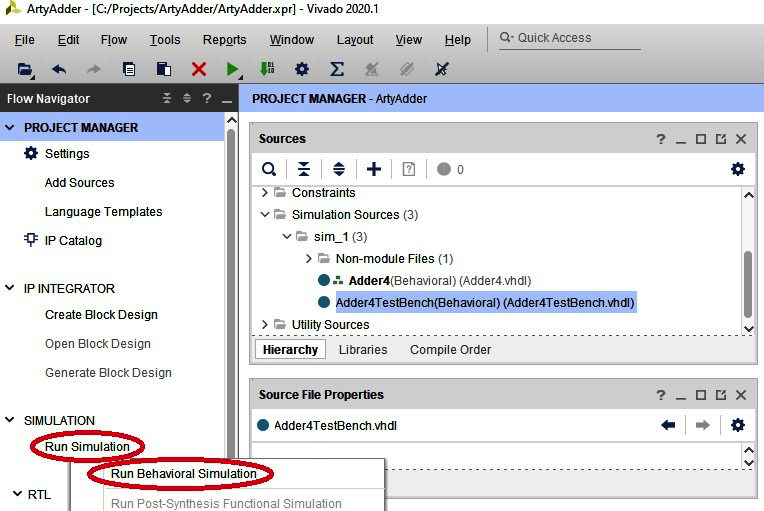

- Cliquez sur Exécuter la simulation , puis Exécuter une simulation comportementale dans le Navigateur de flux fenêtre pour entrer en mode simulation. Si vous n'avez pas encore enregistré les fichiers de l'éditeur, vous serez invité à le faire. Cliquez sur Enregistrer . La simulation s'exécutera alors :

Figure 4.20 – Sélection du menu Exécuter la simulation comportementale

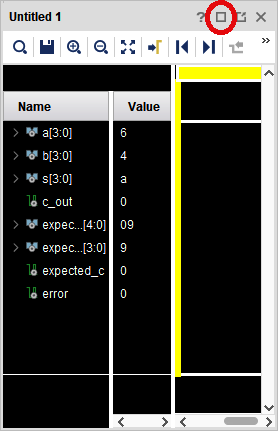

- Lorsque la SIMULATION fenêtre s'ouvre, cliquez sur le bouton Agrandir dans la fenêtre de sortie de la simulation avec le titre Sans titre 1 :

Figure 4.21 – Fenêtre des résultats de simulation

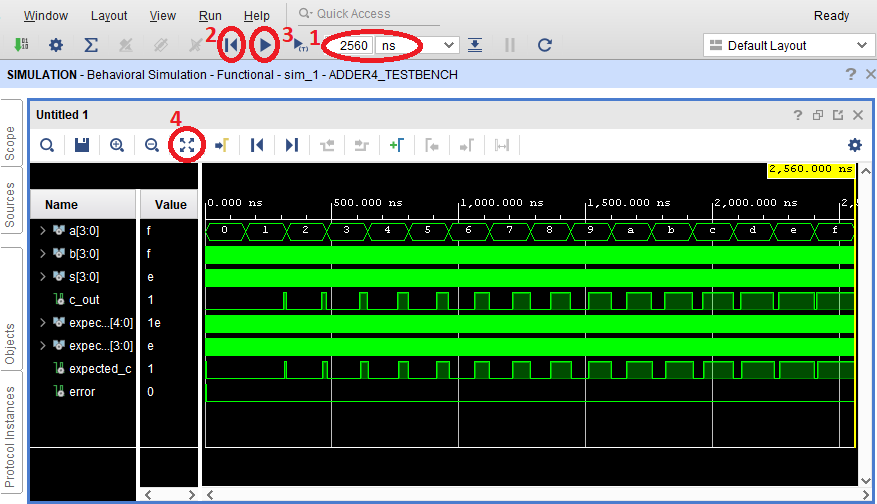

Le temps total simulé de chaque passage dans la boucle interne est de 10 ns. Parce qu'il y a 256 passages dans la boucle dans Adder4TestBench.vhdl , le temps d'exécution de la simulation est de 2560 ns.

- Définir le temps d'exécution de la simulation sur 2560 ns dans la barre d'outils supérieure (étape 1 dans la figure suivante), appuyez sur le bouton de redémarrage pointant vers la gauche (étape 2 ), puis appuyez sur le bouton orienté vers la droite pour exécuter la simulation pendant 2560 ns (étape 3 ), et enfin, appuyez sur Zoom Fit bouton (étape 4 ) pour mettre à l'échelle la plage de données de sortie de simulation pour qu'elle s'adapte à la fenêtre :

Figure 4.22 – Résultats de la simulation du début à la fin de l'analyse

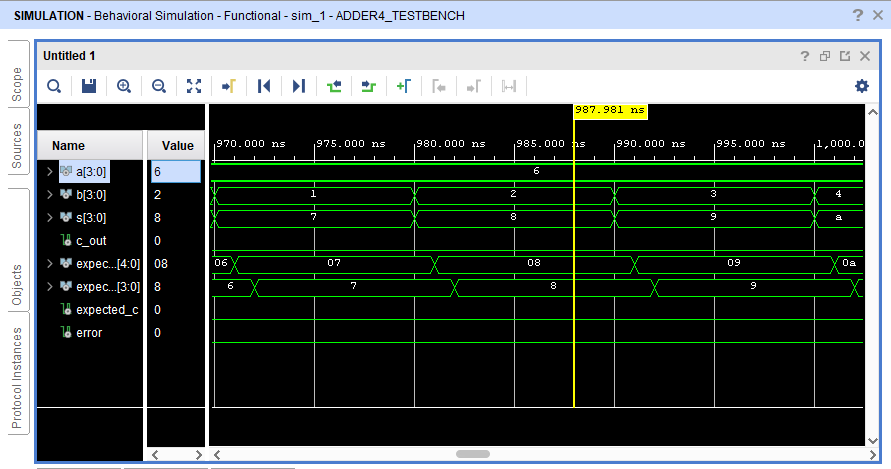

Vous pouvez utiliser les icônes de loupe pour zoomer sur n'importe quel point de la trace et observer les résultats de chaque opération d'ajout effectuée pendant le test. Par exemple, la figure suivante montre que les valeurs décimales 6 et 2 ont été ajoutées pour produire le résultat 8 avec un report de 0. Ces valeurs correspondent aux valeurs attendues, ce qui a provoqué une erreur à mettre à 0. L'erreur le signal est 0 pour les 256 cas de test, indiquant que notre circuit logique a réussi tous les tests :

Figure 4.23 – Vue agrandie des résultats de la simulation

- Fermez le mode simulation en cliquant sur le X dans le bleu SIMULATION barre au-dessus de la trace des données Cliquez sur OK lorsqu'il vous est demandé si vous souhaitez fermer la simulation.

Après avoir réussi les tests comportementaux, nous définirons les signaux d'E/S utilisés dans la conception.

Définition des signaux d'E/S

Notre prochaine étape consiste à connecter les entrées et les sorties de notre circuit aux périphériques matériels de la carte Arty. Les entrées seront les commutateurs et les boutons-poussoirs de la carte, et les sorties seront des LED.

Les étapes suivantes créeront un fichier de contraintes qui décrit les broches d'E/S que nous utiliserons sur le périphérique FPGA et les fonctions connectées à ces broches sur la carte Arty. Les fichiers de contraintes ont l'extension xdc :

- Dans les Sources sous-fenêtre, cliquez avec le bouton droit sur Contraintes et sélectionnez Ajouter des sources… .

- Dans Ajouter des sources dialogue, assurez-vous d'Ajouter ou créer des contraintes est sélectionné, puis cliquez sur Suivant .

- Dans Ajouter ou créer des contraintes boîte de dialogue, cliquez sur Créer un fichier .

- Entrez le nom du fichier Arty-A7-100.xdc (ou Arty-A7-35.xdc si approprié pour votre appareil) et cliquez sur OK .

- Cliquez sur Terminer pour ignorer l'Ajouter ou créer des contraintes

- Développez les Contraintes arborescence des sources et double-cliquez sur Arty-A7-35.xdc .

- Digilent fournit des fichiers de contraintes pré-remplis pour les cartes Arty A7 Visitez https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc et copiez l'intégralité du contenu de la fenêtre du navigateur dans la fenêtre de l'éditeur Arty-A7-35.xdc de Vivado. Si cela est approprié pour votre appareil, utilisez le fichier sur https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc à la place.

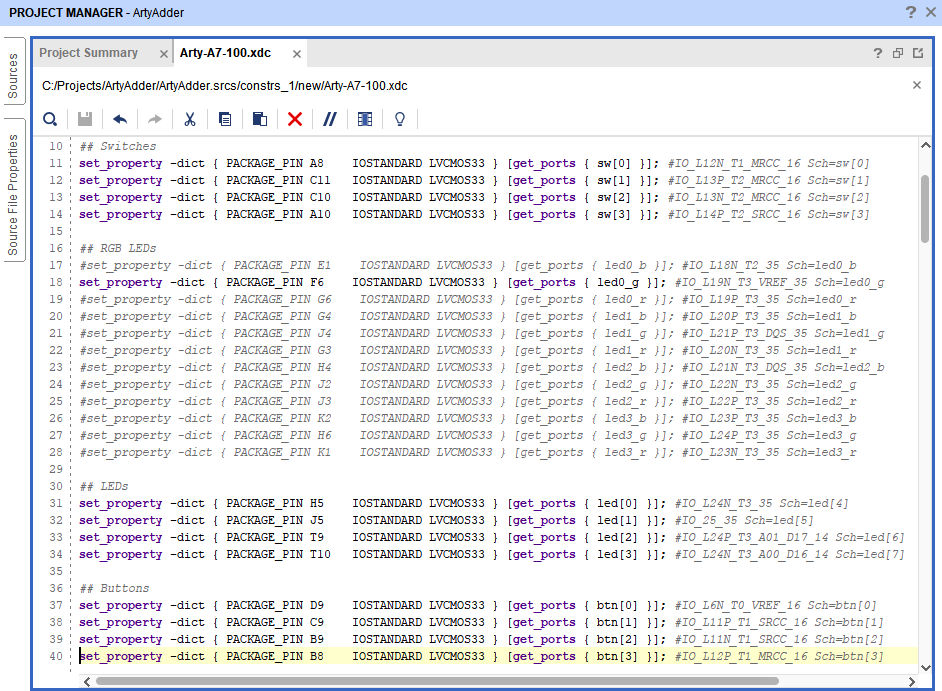

- Toutes les broches d'E/S sont commentées dans le fichier de contraintes en décommentant les lignes appropriées du fichier en supprimant le caractère # au début de chaque ligne. Nous utiliserons les épingles répertoriées dans les sections suivantes dans le Arty- A7-100.xdc fichier :Commutateurs , RVB LED (mais seulement led0_g , la première LED verte), LED , et Boutons . La figure suivante montre ces lignes après qu'elles aient été décommentées :

Figure 4.24 – Fenêtre de l'éditeur de contraintes

Dans la section suivante, nous allons créer un fichier VHDL de niveau supérieur qui interface le code de l'additionneur avec les périphériques d'E/S.

Création d'un fichier VHDL de niveau supérieur

Nous allons ensuite créer un fichier VHDL de niveau supérieur qui connecte notre composant additionneur 4 bits aux signaux d'E/S de la carte correspondante :

- Dans les Sources sous-fenêtre, faites un clic droit sur Sources de conception et sélectionnez Ajouter des sources… .

- Dans Ajouter des sources dialogue, assurez-vous d'Ajouter ou créer des sources de conception est sélectionné, puis cliquez sur Suivant .

- Dans Ajouter ou créer des sources de conception boîte de dialogue, cliquez sur Créer un fichier .

- Entrez le nom du fichier vhdl et cliquez sur OK .

- Cliquez sur Terminer pour ignorer le Ajouter ou créer des sources de conception boîte de dialogue, puis cliquez sur OK dans le Définir le module dialogue et cliquez sur Oui lorsqu'on vous demande si vous êtes sûr de vouloir les utiliser

- Double-cliquez sur vhdl sous Sources de conception . Supprimez le contenu automatiquement renseigné de ArtyAdder.vhdl fenêtre de l'éditeur et entrez le code suivant dans ArtyAdder.vhdl éditeur :

-- Charge la bibliothèque de bibliothèques standard IEEE ; utiliser IEEE.STD_LOGIC_1164.ALL;l'entité ARTY_ADDER est le port ( sw :dans STD_LOGIC_VECTOR (3 jusqu'à 0); btn :dans STD_LOGIC_VECTOR (3 jusqu'à 0); led :out STD_LOGIC_VECTOR (3 jusqu'à 0); led0_g :out STD_LOGIC );end entité ARTY_ADDER;architecture BEHAVIORAL d'ARTY_ADDER est -- La définition précédente du composant additionneur 4 bits ADDER4 est le port ( A4 :in std_logic_vector(3 downto 0); B4 :in std_logic_vector(3 downto 0); SUM4 :out std_logic_vector(3 jusqu'à 0); C_OUT4 :out std_logic ); composant de fin ; début ADDER :carte des ports ADDER4 ( A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g ); fin architecture BEHAVIORAL ;

Ce code mappe les noms de signaux pour les périphériques d'E/S nommés dans Arty-A7-100.xdc en tant que sw (4 interrupteurs), btn (4 boutons poussoirs), led (4 LED monochromes) et led0_g (le canal vert de la première LED multicolore) à l'ADDER4 entrées et sorties.

Bien que VHDL ne soit pas sensible à la casse, le traitement de xdc les fichiers de contraintes dans Vivado sont sensibles à la casse. La casse utilisée dans les noms de périphériques d'E/S définis dans le xdc doit être identique lorsqu'il est référencé dans un fichier VHDL. Plus précisément, les noms de signaux d'E/S en VHDL doivent être en minuscules dans ce fichier car ils sont en minuscules dans le fichier de contraintes.

Nous sommes maintenant prêts à synthétiser, implémenter et programmer notre conception pour la carte Arty.

Synthèse et implémentation du flux binaire FPGA

Alternativement, vous pouvez sélectionner Générer Bitstream et Vivado effectuera toutes les étapes requises, y compris la synthèse, la mise en œuvre et la génération de flux binaires sans autre intervention de l'utilisateur. Si une erreur fatale se produit, le processus s'arrêtera et des messages d'erreur s'afficheront. Effectuez les étapes suivantes pour générer le flux binaire :

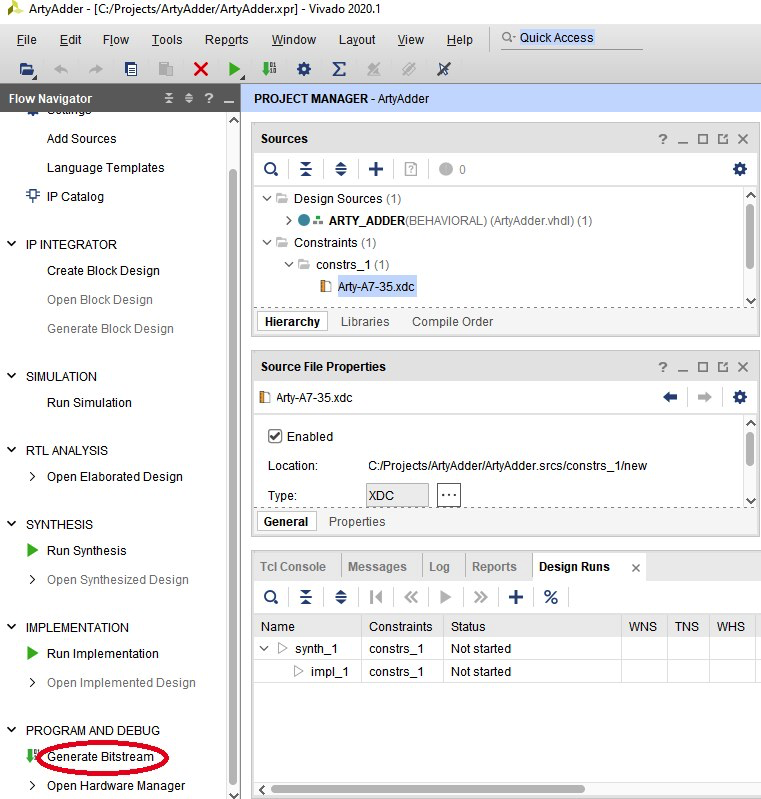

- Cliquez sur Générer Bitstream pour démarrer la construction Il peut vous être demandé si vous souhaitez enregistrer les éditeurs de texte. Cliquez sur Enregistrer . Il se peut qu'on vous informe qu'il n'y a pas de résultats de mise en œuvre disponibles et qu'on vous demande s'il est acceptable de lancer la synthèse et la mise en œuvre. Cliquez sur Oui :

Figure 4.25 – Générer la sélection du menu Bitstream

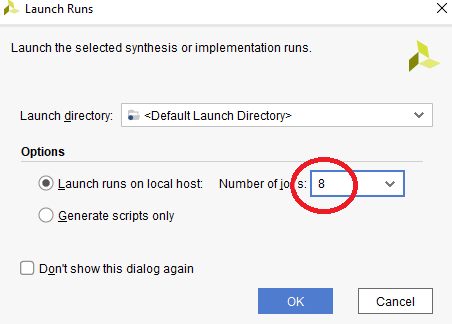

- Les courses de lancement dialogue sera alors Vous pouvez sélectionner une valeur pour Nombre de travaux jusqu'au nombre de cœurs de processeur de votre ordinateur. L'utilisation de plus de cœurs accélère le processus, mais cela peut ralentir votre machine si vous souhaitez continuer à l'utiliser pendant un long processus de construction. Cliquez sur OK pour démarrer la compilation :

Figure 4.26 – Boîte de dialogue Lancer les exécutions

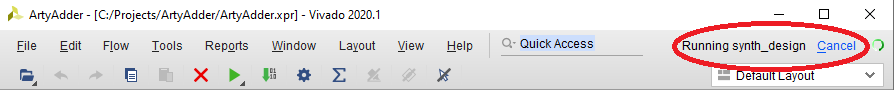

- Pendant le processus de construction, Vivado affichera l'état dans le coin supérieur droit de la fenêtre principale. Si nécessaire, vous pouvez annuler le processus de construction en cliquant sur Annuler à côté de l'affichage d'état :

Figure 4.27 – Affichage de l'état de la compilation

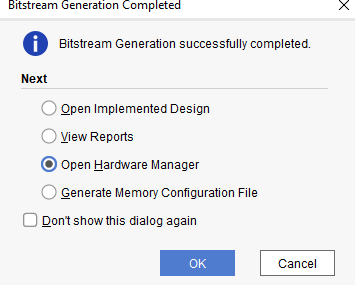

- Une fois le processus de génération terminé, en supposant qu'il n'y ait pas eu d'erreurs fatales, une Génération de flux de données terminée dialog will Bien que d'autres options soient proposées, nous procéderons directement au téléchargement du bitstream sur la carte Arty. Sélectionnez Ouvrir le gestionnaire de matériel et cliquez sur OK :

Figure 4.28 – Boîte de dialogue Génération de flux binaire terminée

Ensuite, nous allons télécharger le bitstream dans le FPGA.

Téléchargement du flux binaire sur le tableau

Effectuez les étapes suivantes pour télécharger le bitstream sur une carte Arty A7 :

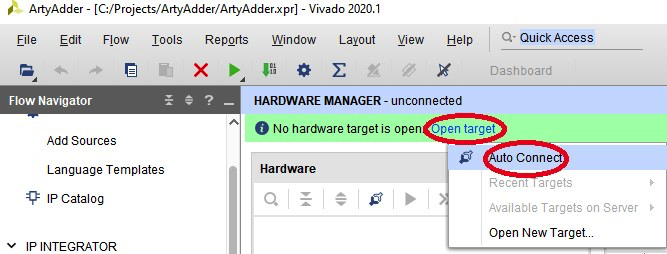

- Le GESTIONNAIRE MATÉRIEL La boîte de dialogue apparaîtra et indiquera Aucune cible matérielle n'est ouverte .

- Connectez votre carte Arty A7-35 ou A7-100 à l'ordinateur avec une clé USB Attendez quelques secondes que la carte soit reconnue, puis cliquez sur Ouvrir la cible , puis Connexion automatique :

Figure 4.29 – Sélections de cible ouverte et de connexion automatique

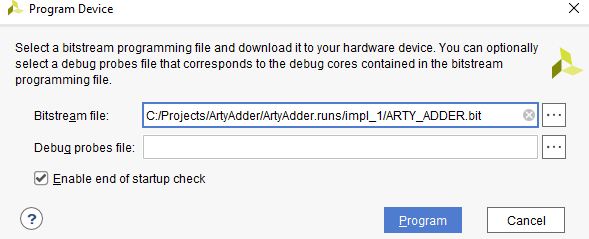

- Après quelques secondes, Vivado devrait indiquer que la carte est connectée. Cliquez sur Programmer l'appareil pour télécharger le flux de bits FPGA sur l'Arty Vous serez invité à sélectionner un fichier de flux de bits. Si vous avez utilisé la même structure de répertoire que cet exemple, le fichier sera situé dans C:/Projects/ArtyAdder/ ArtyAdder.runs/impl_1/ARTY_ADDER.bit :

Figure 4.30 – Boîte de dialogue Programmer l'appareil

- Cliquez sur Programmer pour télécharger le programme sur le périphérique FPGA et le démarrer

- Vous pouvez maintenant tester le fonctionnement du programme avec l'Arty I/O Placez tous les quatre interrupteurs dans le off position (déplacez les interrupteurs vers le bord adjacent de la carte) et n'appuyez sur aucun des quatre boutons-poussoirs. Les quatre voyants verts doivent être éteints.

- Si vous activez un interrupteur individuel ou appuyez sur un bouton-poussoir, la LED verte correspondante doit s'allumer. Allumer n'importe quelle combinaison de commutateurs tout en appuyant sur n'importe quel nombre de boutons-poussoirs ajoutera les nombres de 4 bits correspondants et allumera les LED avec le S'il y a un report (par exemple, allumez SW3 et appuyez sur BTN3 simultanément), la LED verte de report s'allumera.

Le processus de programmation effectué ici a stocké le programme dans la RAM FPGA. Si vous redémarrez la carte FPGA, vous devrez répéter le processus de programmation pour recharger le programme. Alternativement, vous pouvez stocker le fichier de configuration FPGA dans la mémoire flash embarquée comme décrit dans la section suivante.

Programmation du flux binaire sur la mémoire flash intégrée

Pour configurer le FPGA à chaque mise sous tension de la carte Arty, le fichier de configuration du FPGA doit être stocké dans la mémoire flash de la carte. Si le cavalier MODE est installé, le FPGA tentera de télécharger un fichier de configuration à partir de la mémoire flash intégrée à la mise sous tension. Cette mémoire est située dans une puce séparée adjacente au FPGA Artix-7. Suivez ces étapes pour programmer le fichier de configuration dans la mémoire flash :

- Installez le MODE cavalier sur la carte Arty s'il n'y est pas déjà

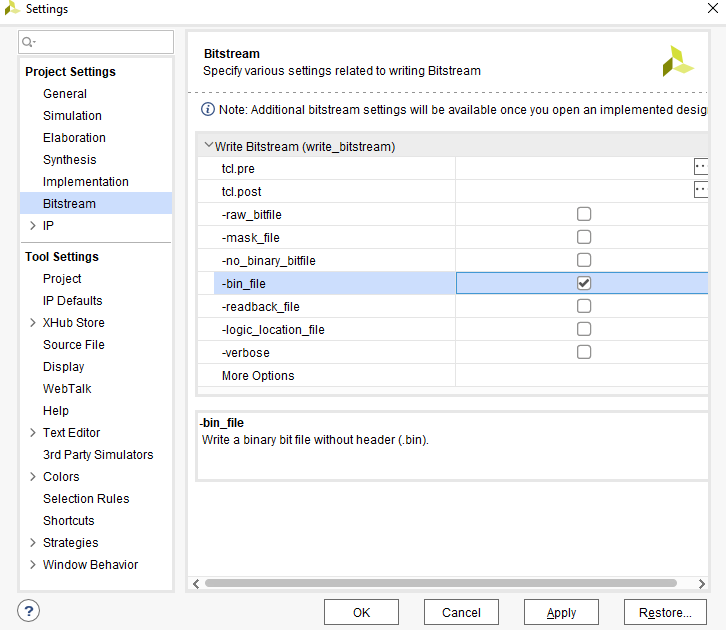

- Clic droit sur Générer Bitstream et sélectionnez Paramètres du flux binaire… .

- Dans les Paramètres dialogue, cochez la case à côté de -bin_file et cliquez sur OK :

Figure 4.31 – Boîte de dialogue des paramètres Bitstream

- Dans la boîte de dialogue principale de Vivado, cliquez sur Générer Bitstream et répétez le processus de génération de flux binaire. Cliquez sur Annuler lorsque la Génération Bitstream est terminée dialogue

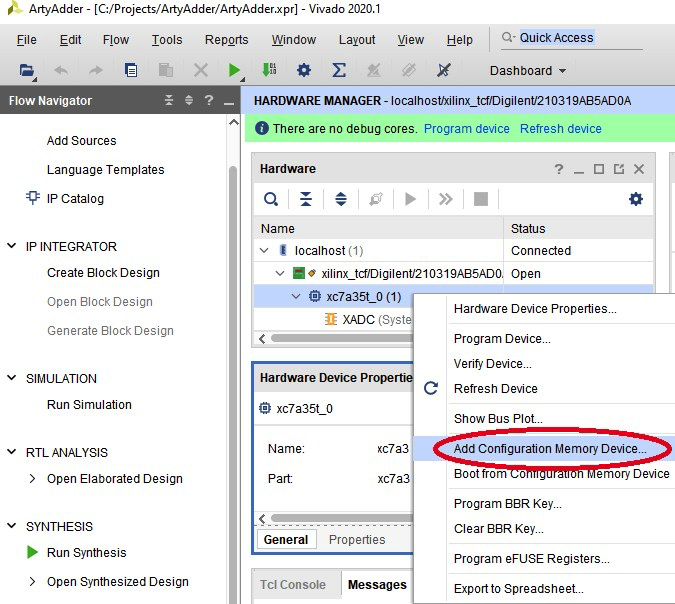

- Dans le Matériel boîte de dialogue, cliquez avec le bouton droit sur le numéro de pièce FPGA (xc7a100t_0 ) et sélectionnez Ajouter un périphérique de mémoire de configuration… :

Figure 4.32 – Sélection du menu Ajouter un périphérique de mémoire de configuration…

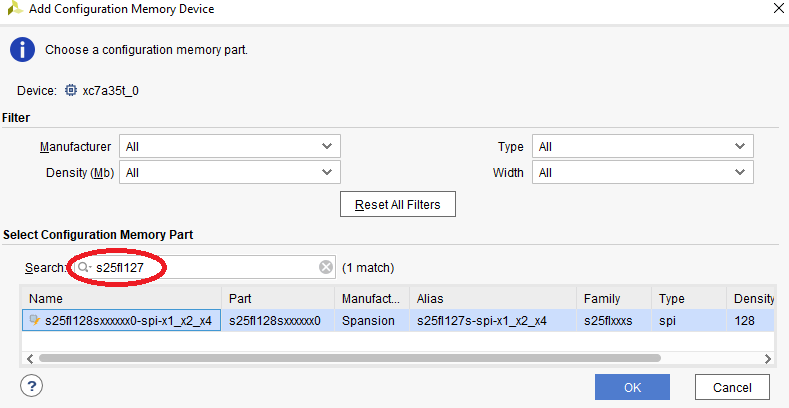

- Tapez s25fl127 dans la Recherche Cela devrait faire apparaître un numéro de pièce correspondant. Sélectionnez la pièce et cliquez sur OK :

Figure 4.33 – Boîte de dialogue Ajouter un périphérique de mémoire de configuration

- Une boîte de dialogue s'affichera vous demandant Voulez-vous programmer le périphérique de mémoire de configuration maintenant ? Cliquez sur OK .

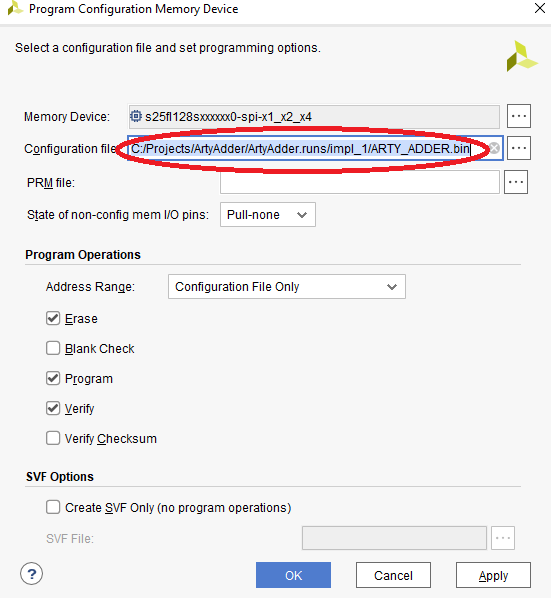

- Cela fera apparaître un Périphérique de mémoire de configuration de programme boîte de dialogue demandant le nom du fichier de configuration. Cliquez sur le … bouton à droite du Fichier de configuration et sélectionnez C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Cliquez sur OK :

Figure 4.34 – Boîte de dialogue Périphérique mémoire de configuration du programme

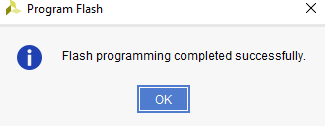

- Le processus de programmation prendra plusieurs secondes. Vous devriez recevoir un message indiquant la réussite une fois que le fichier a été programmé dans la mémoire flash de la carte :

Figure 4.35 – Boîte de dialogue Fin du programme Flash

Après cela, chaque fois que vous mettez la carte sous tension, le programme de l'additionneur 4 bits se charge et s'exécute. Il faudra beaucoup de temps pour que le programme se charge avec les paramètres que nous avons utilisés pour le chargement du fichier de configuration. Pour éviter d'attendre que le FPGA charge le programme, vous pouvez améliorer la vitesse de chargement du fichier de configuration en procédant comme suit :

- Sélectionnez Ouvrir la conception synthétisée dans le Navigateur de flux .

- Dans le menu principal de Vivado, sélectionnez Outils/Modifier les propriétés de l'appareil… .

- Dans le Général onglet, définissez Activer la compression Bitstream à VRAI .

- Dans la Configuration onglet, définissez le Débit de configuration (MHz) à 33, puis cliquez sur OK .

- Générez à nouveau le flux binaire et programmez la mémoire flash comme décrit. Vous devrez retirer le périphérique de mémoire de configuration et le rajouter pour afficher l'option de reprogrammation.

- Fermer Matériel Gestionnaire .

- Débranchez le câble USB de la carte Arty et branchez-le. Le programme devrait commencer à s'exécuter pratiquement instantanément à la mise sous tension.

Cette section a présenté un exemple de logique combinatoire simple interagissant avec des signaux sur les broches d'E/S du FPGA. L'intention ici était de vous familiariser avec le Vivado

suite d'outils et de démontrer comment les outils sont utilisés pour effectuer un cycle de développement FPGA complet.

Résumé

Ce chapitre a commencé par une discussion sur l'utilisation efficace des FPGA dans les architectures de systèmes embarqués en temps réel et s'est poursuivi par une description des dispositifs FPGA standard et des composants de bas niveau qu'ils contiennent. La gamme de langages de conception FPGA, y compris les HDL, les méthodes de diagramme de blocs et les langages de programmation de logiciels populaires tels que C/C++, a été introduite. Un aperçu du processus de développement du FPGA a été présenté. Le chapitre s'est terminé par un exemple complet de cycle de développement FPGA, commençant par un énoncé des exigences et se terminant par un système fonctionnel implémenté sur une carte de développement FPGA à faible coût.

Après avoir terminé ce chapitre, vous devez savoir comment les FPGA peuvent être appliqués efficacement dans les architectures de systèmes embarqués en temps réel et comprendre les composants à l'intérieur d'un circuit intégré FPGA. Vous avez appris les langages de programmation utilisés dans la conception d'algorithmes FPGA, les étapes du cycle de développement FPGA et comprenez la séquence d'étapes du processus de développement FPGA.

Le prochain chapitre développera le processus de développement de FPGA pour fournir une approche complète de l'architecture des systèmes embarqués temps réel contenant des FPGA. Il entamera également le développement d'un prototype de système embarqué hautes performances, un oscilloscope numérique, qui servira d'exemple pour les chapitres suivants.

Réimprimé avec la permission de Packt Publishing. Copyright © 2021 Édition Packt

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT).

Jim Ledin est le PDG de Ledin Engineering, Inc. Jim est un expert en conception, développement et test de logiciels et de matériel embarqués. Il est également accompli dans l'évaluation de la cybersécurité des systèmes embarqués et les tests d'intrusion. Il a un B.S. diplôme en génie aérospatial de l'Iowa State University et un M.S. diplôme en génie électrique et informatique du Georgia Institute of Technology. Jim est un ingénieur électricien professionnel enregistré en Californie, un professionnel certifié de la sécurité des systèmes d'information (CISSP), un hacker éthique certifié (CEH) et un testeur de pénétration certifié (CPT). Contenus associés :

- Conception embarquée avec FPGA :ressources matérielles

- Conception embarquée avec FPGA :langages d'implémentation

- Conception embarquée avec FPGA :processus de développement

- Les outils open source aident à simplifier la programmation FPGA

- Implémentation d'algorithmes à virgule flottante dans les FPGA ou les ASIC

- Tirer parti des FPGA pour l'apprentissage en profondeur

- Les outils logiciels migrent le code GPU vers les FPGA pour les applications d'IA

Pour plus d'informations sur Embedded, abonnez-vous à la newsletter hebdomadaire d'Embedded.

Embarqué

- Qu'est-ce que la conception de systèmes embarqués :étapes du processus de conception

- Finir des pièces imprimées en 3D avec… des crayons ?

- Entretien d'experts :Technologue en chef d'ANSYS sur la réussite de l'impression 3D en métal avec la simulation

- Transformer le Big Data en Smart Data avec l'IA intégrée

- Défis de mise en œuvre du port USB Type-C et solutions de conception

- Les tendances clés du secteur façonnent la conception intégrée

- Clienttron :TPV multifonction avec imprimante intégrée

- Kit de conception mesure la tension artérielle avec capteur optique

- Tout compris avec additif