La puce du processeur en mémoire accélère les calculs de l'IA

Imec et GlobalFoundries ont démontré une puce de processeur en mémoire qui peut atteindre une efficacité énergétique jusqu'à 2900 TOPS/W, environ deux ordres de grandeur au-dessus des puces de processeur en mémoire commerciales d'aujourd'hui. La puce utilise une idée établie, l'informatique analogique, mise en œuvre dans la SRAM dans la technologie de processus de silicium sur isolant entièrement appauvri (FD-SOI) 22 nm de GlobalFoundries. Le calcul analogique en mémoire (AiMC) d'Imec sera disponible pour les clients de GlobalFoundries en tant que fonctionnalité pouvant être implémentée sur la plate-forme 22FDX de l'entreprise.

La puce de test AnIA d'Imec, que l'on voit ici montée sur le PCB utilisé pour la mesure et la caractérisation, peut atteindre jusqu'à 2900 TOPS/W (Image :Imec)

Calcul analogique

Le calcul analogique, ou processeur en mémoire, est une technique établie qui est déjà utilisée dans les puces d'accélérateur d'IA commerciales des startups Mythic, Syntiant, Gyrfalcon et autres.

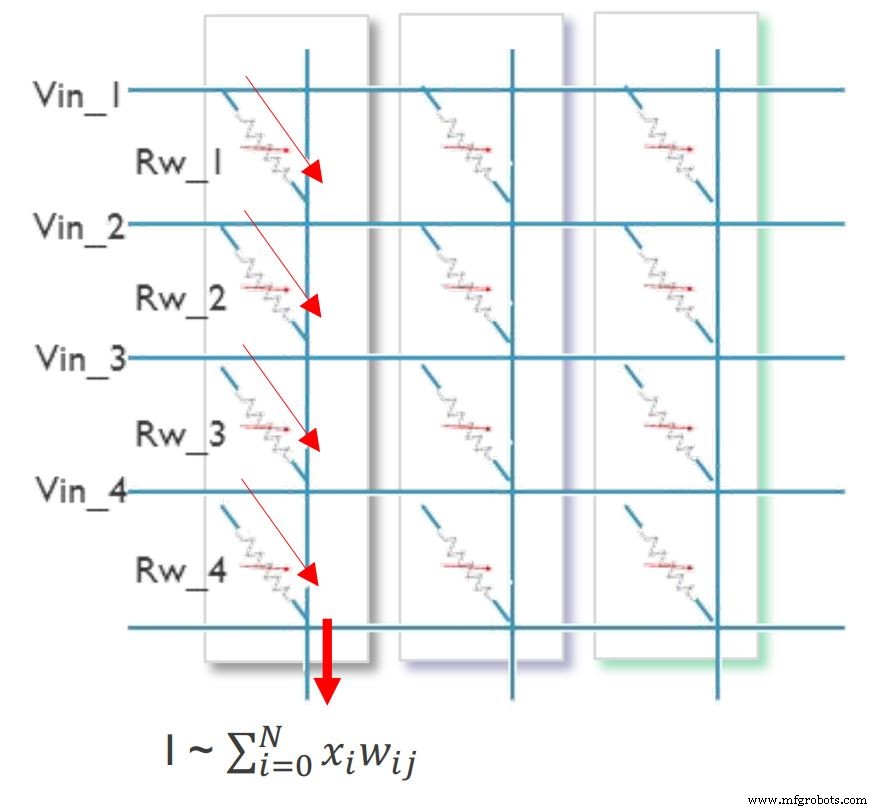

Étant donné qu'un modèle de réseau neuronal peut avoir des dizaines ou des centaines de millions de poids, l'échange de données entre la mémoire et le processeur est inefficace. L'informatique analogique utilise une matrice mémoire pour stocker les poids et effectuer également des opérations de multiplication-accumulation (MAC), de sorte qu'aucun transfert mémoire-processeur n'est nécessaire. Chaque élément memristor (peut-être une cellule ReRAM) a sa conductance programmée à un niveau analogique qui est proportionnel au poids requis.

L'application d'une tension proportionnelle à l'activation de l'entrée (via la conversion numérique-analogique - à gauche du diagramme ci-dessous) signifie que le courant traversant chaque élément est proportionnel au produit de l'activation et du poids. Le courant traversant chaque ligne de bit verticale (lignes verticales dans le diagramme ci-dessous) est la somme de ces produits de poids d'activation, qui peuvent être alimentés par un convertisseur analogique-numérique. Cette somme des produits de poids d'activation est critique pour le calcul des algorithmes de réseau neuronal.

L'informatique analogique utilise un tableau de cellules memristor pour calculer la multiplication vectorielle matricielle sans avoir à envoyer de données entre la mémoire et le processeur (Image :Imec)

"En pratique, de nombreuses options sont possibles en plus de ReRAM - nous pouvons utiliser MRAM, Flash, DRAM... l'objectif de ce programme est de comprendre laquelle est la meilleure pour l'application et d'optimiser les options pour chaque domaine d'application", a expliqué Diederik Verkest, programme directeur du machine learning chez Imec.

Puce de test

Imec a construit une puce de test, appelée accélérateur d'inférence analogique (AnIA), basée sur le processus FD-SOI 22 nm de GlobalFoundries. La gamme de cellules SRAM de 512 k d'AnIA ainsi que l'infrastructure numérique comprenant 1 024 DAC et 512 ADC occupent 4 mm 2 . Il peut effectuer environ un demi-million

Ioannis Papistas (Image :Imec)

calculs par cycle d'opération basés sur des activations d'entrée 6 bits (bit de signe plus), des poids ternaires (-1, 0, +1) et des sorties 6 bits.

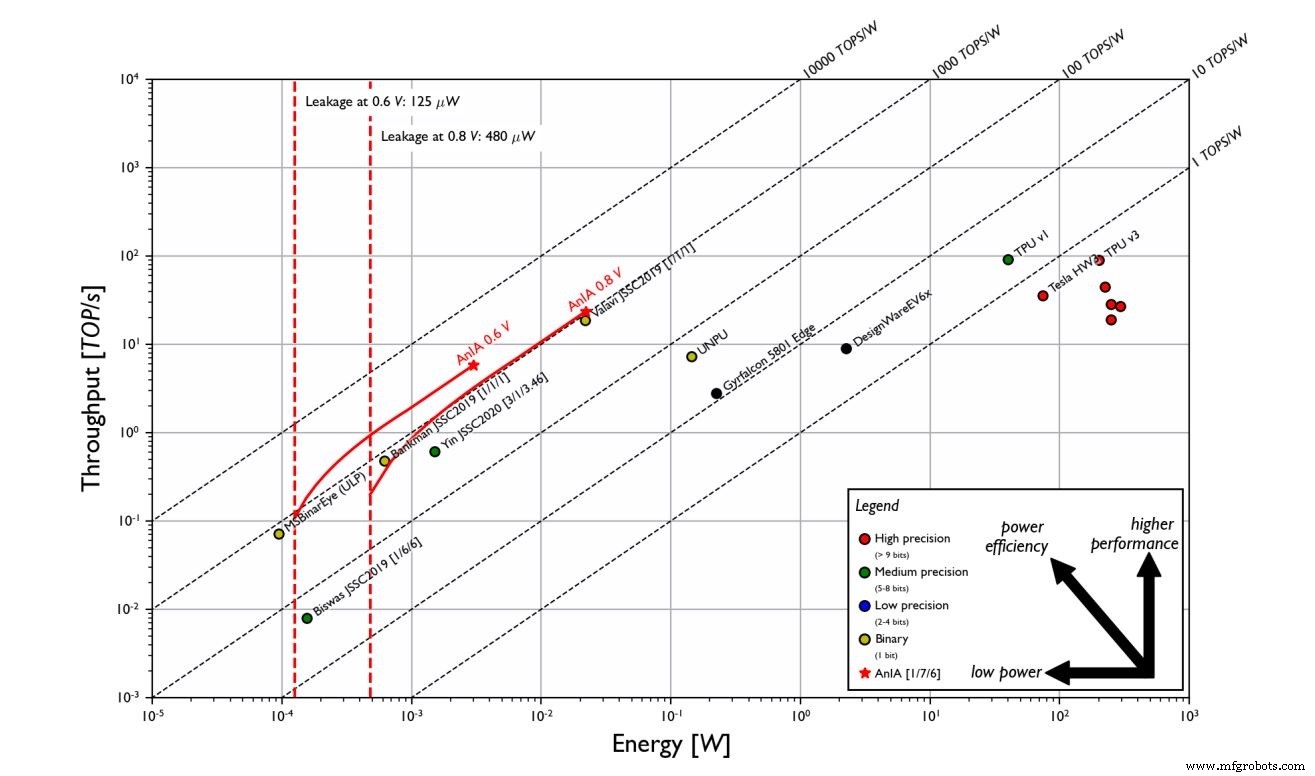

"Nous sommes en mesure de produire la sortie de multiplication vectorielle matricielle à différentes tensions d'alimentation, 0,8 et 0,6 V", a déclaré Ioannis Papistas du groupe d'apprentissage automatique d'Imec. « Le fonctionnement à des tensions d'alimentation inférieures sans affecter la précision de l'opération peut réduire considérablement la consommation d'énergie de l'opération, ce qui est particulièrement important pour l'inférence dans les systèmes à contraintes énergétiques. Il s'agit d'une caractéristique importante de notre conception, rendue possible par le processus 22FDX, qui permet une inférence concurrentielle à la périphérie. »

Imec a montré des résultats de précision pour l'inférence de reconnaissance d'objets sur l'ensemble de données CIFAR 10, qui n'ont baissé que d'un point de pourcentage par rapport à une base de référence quantifiée de manière similaire. Avec une tension d'alimentation de 0,8 V, l'efficacité énergétique d'AnIA se situe entre 1050 et 1500 TOPS/W à 23,5 TOPS. Pour une tension d'alimentation de 0,6 V, AnIA a atteint 5,8 TOPS à environ 1800-2900 TOPS/W.

Efficacité énergétique pour divers accélérateurs d'IA par rapport à la puce de test AnIA d'Imec (Cliquez pour agrandir) (Image :Imec)

Innovation grand public

"L'innovation [présentée par Imec] va se généraliser", a déclaré Hiren Majmudar, vice-président et directeur général de l'unité commerciale informatique de GlobalFoundries. « Nous voyons des partenaires, des clients de GlobalFoundries qui sont en phase de post-production avec du silicium validé… nous prévoyons que le silicium basé sur le calcul analogique entrera en production vers la fin de cette année ou au début de l'année prochaine. En termes de déploiement sur le marché de masse, nous prévoyons que le calcul analogique commencera à entrer sur le marché de masse certainement au plus tard en 2022. Mais cela pourrait potentiellement arriver plus tôt que cela. »

Diederik Verkest (Image :Imec)

GlobalFoundries s'efforce d'inclure la technologie AiMC d'Imec en tant que fonctionnalité pouvant être implémentée sur la plate-forme 22 FDX pour permettre des accélérateurs d'IA économes en énergie. Le processus FD-SOI est conçu pour une faible consommation d'énergie, avec la possibilité de fonctionner jusqu'à 0,5 V avec 1 pico-amp par micron pour une fuite en veille ultra-faible. 22FDX avec la nouvelle fonctionnalité AiMC est en cours de développement sur la ligne de production 300 mm de GlobalFoundries à Fab 1 à Dresde, en Allemagne.

Quant à Imec, le programme de machine learning va se poursuivre. L'ambition du groupe est d'atteindre 10 000 TOPS/W (10 TOPS en dessous de 100 mW) pour des capteurs intelligents et des wearables grand public toujours actifs, a déclaré Verkest.

"Dans notre programme ML, nos prochaines étapes consistent à réduire la taille de ces cellules de calcul et à commencer à considérer les dispositifs de mémoire émergents comme une implémentation de nouvelle génération pour ce principe", a-t-il déclaré.

>> Cet article a été initialement publié le notre site partenaire, EE Times.

Embarqué

- Introduction aux circuits intégrés analogiques

- Concevoir avec Bluetooth Mesh :puce ou module ?

- L'architecture de la puce IA cible le traitement des graphes

- Petit module Bluetooth 5.0 intégrant une antenne à puce

- Les chercheurs créent une petite étiquette d'identification d'authentification

- Débuts du processeur radar d'imagerie automobile à 30 ips

- La puce radar de faible puissance utilise des réseaux de neurones à pointes

- La carte de capteur intelligent accélère le développement de l'IA de pointe

- Vitesse des drones durables jusqu'à la production