RRAM Atomic Layer-Deposited HfAlOx avec basse tension de fonctionnement pour le calcul d'applications en mémoire

Résumé

La loi de Moore atteignant sa limite physique, l'architecture traditionnelle de von Neumann est confrontée à un défi. On s'attend à ce que la mémoire à accès aléatoire résistive (RRAM) basée sur l'architecture en mémoire informatique puisse être un candidat potentiel pour surmonter le problème de goulot d'étranglement de von Neumann des ordinateurs traditionnels [Backus, J, Can programming beliberated from the von Neumann style?, 1977]. Dans ce travail, une RRAM à base de HfAlOx qui est compatible avec la technologie CMOS a été fabriquée par un procédé de dépôt de couche atomique (ALD). Metal Ag et TaN sont choisis comme électrodes supérieures (TE). Les expériences montrent que le dispositif Ag/HfAlOx/Pt présente des avantages en tant que dispositif de calcul à mémoire en raison de la faible tension de consigne (0,33 ~ 0,6 V), ce qui signifie une faible consommation d'énergie et une bonne uniformité. Basée sur une structure Ag/HfAlOx/Pt, la logique IMP a été implémentée à grande vitesse en appliquant une impulsion basse tension haute fréquence de 100 ns (0,3 µV et 0,6 µV). Après deux étapes de mise en œuvre de l'IMP, la NAND peut également être obtenue.

Contexte

Pour les frontières entre stockage et calcul, les chercheurs ont proposé une série de programmes de recherche :mémoire à large bande passante, calcul en quasi-mémoire et réseaux de compression neuronale. Ces méthodes peuvent réduire le temps d'accès à la mémoire, mais elles ne pourraient pas résoudre fondamentalement ce problème. Afin de résoudre fondamentalement ce problème, le concept de calcul en mémoire a attiré l'attention dans le monde entier. Il convient de noter qu'un dispositif de mémoire à accès aléatoire résistif (RRAM) a attiré une large attention en tant que candidat compétitif pour le dispositif informatique non von Neumann en raison de sa capacité de calcul en mémoire [1,2,3,4,5, 6]. Les dispositifs informatiques en mémoire agissent à la fois comme des unités de calcul et de stockage dans le même circuit [7]. Il a été proposé pour la première fois en 1971 par Chua [8]. Près de 40 ans plus tard, le fonctionnement logique basé sur RRAM a été proposé pour la première fois en 2010 [9]. Depuis lors, les dispositifs informatiques en mémoire basés sur RRAM ont été largement étudiés et de nombreuses méthodes de mise en œuvre ont été proposées [10,11,12,13,14]. Mais en tant que périphérique informatique en mémoire, la caractéristique la plus cruciale est la stabilité et la faible consommation d'énergie. Il y a encore beaucoup de problèmes dans ce domaine qui doivent être explorés. Dans cette lettre, deux types de dispositifs RRAM ont été construits et les propriétés électriques ont été testées. Dans le processus de mise en œuvre des opérations logiques, des tensions de réglage et de réinitialisation stables et une bonne uniformité entre les appareils sont des indicateurs très importants.

Jusqu'à présent, une grande variété de matériaux ont montré des comportements RRAM, mais peu d'entre eux étaient compatibles avec le processus CMOS. Le film binaire d'oxydes à k élevé HfAlOx a été déposé à l'aide d'un dépôt par couche atomique (ALD). L'ALD est bien adapté au dépôt de films d'oxyde et de couches superposées pour divers dispositifs et applications [15] car il est basé sur la saturation de surface et un dosage précis du précurseur n'est pas nécessaire. HfAlOx pourrait être bien compatible avec le processus CMOS traditionnel et utilisé comme couche diélectrique du dispositif informatique en mémoire. Les dispositifs RRAM Ag/HfAlOx/Pt ont été utilisés pour mettre en œuvre des opérations logiques avec état. La logique IMP était considérée comme l'une des quatre opérations logiques fondamentales (OU, ET, NON et IMP) par Whitehead et Russell en 1910 [16]. De plus, la logique NAND peut être obtenue par deux étapes de logique IMP. La logique NAND est connue sous le nom de logique universelle, ce qui signifie que toute logique booléenne peut être construite via la logique NAND. Ce dispositif informatique en mémoire compatible CMOS, à haute vitesse et à faible tension de fonctionnement montre un moyen efficace de résoudre les difficultés de structure traditionnelles de von Neumann à l'avenir.

Méthodes

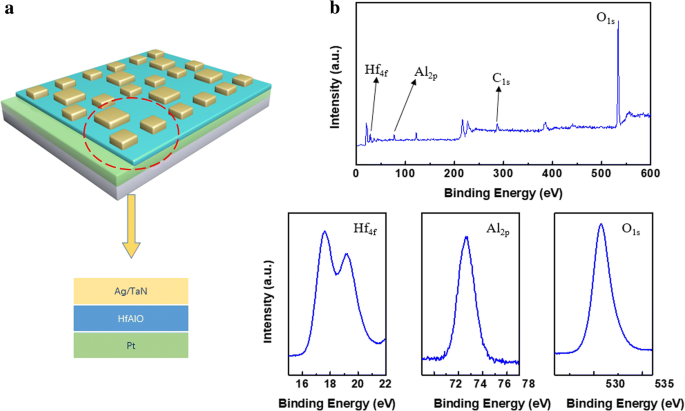

Dans ce travail, des dispositifs Ag/HfAlOx/Pt et TaN/HfAlOx/Pt ont été fabriqués, respectivement. Le schéma est illustré à la Fig. 1a. Tout d'abord, une électrode inférieure en Pt à couche mince de 70 nm a été déposée par dépôt physique en phase vapeur (PVD) sur le SiO2 nettoyé. /Si substrat. Ensuite, un film binaire d'oxyde HfAlOx à haute teneur en k d'une épaisseur de 16 nm a été déposé à l'aide d'ALD dérivé de tétrakiséthylméthylamino hafnium (TEMAH), de triméthyl aluminium (TMA) et de H2 O précurseurs à 240°C. Enfin, un film d'électrode supérieure en Ag ou TaN de 50 nm a été fabriqué par photolithographie et fabriqué par PVD. Avec une polarisation sur l'électrode supérieure et la masse sur l'électrode inférieure, les mesures de courant continu des dispositifs ont été effectuées par un semi-conducteur Agilent B1500A à température ambiante. De plus, des mesures logiques ont été effectuées à l'aide d'un analyseur de paramètres de dispositif à semi-conducteur Agilent B1500A et de deux unités de générateur d'impulsions à semi-conducteur (SPGU).

un Le schéma des appareils Ag/HfAlOx/Pt et TaN/HfAlOx/Pt. b Spectres XPS du HfAlO 16 nm

Résultat et discussion

La mémoire et le processeur sont séparés dans une architecture informatique traditionnelle de von Neumann [17]. Le temps de transfert des données stockées en mémoire et calculées sur l'unité de calcul limite fortement les performances de l'ordinateur. Il est possible de casser la limitation en exploitant les données directement sur la mémoire. La recherche sur l'informatique en mémoire a le potentiel de dépasser cette limite.

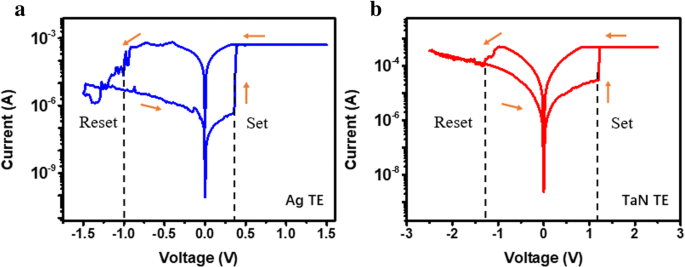

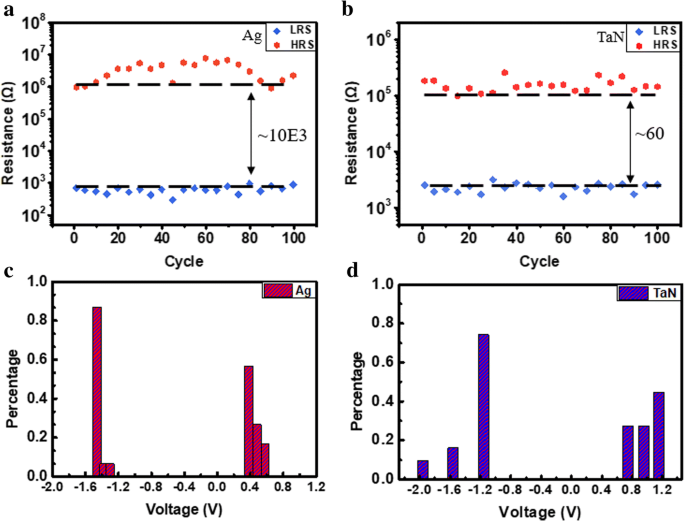

Pour démontrer les fonctions logiques, la RRAM a été préparée avec Ag/HfAlOx/Pt et TaN/HfAlOx/Pt. Le schéma est illustré à la Fig. 1a ; deux petits appareils avec un grand appareil forment une unité logique RRAM minimale IMP. Une logique différente peut être mise en œuvre en utilisant plusieurs cellules IMP. Les films HfAlOx 16 nm cultivés par ALD ont été caractérisés par spectroscopie de photoémission aux rayons X (XPS). Comme le montre la figure 1b, les spectres XPS complets et Hf4f, Al2p, C1s et O1s sont exposés. A partir des résultats XPS, on peut conclure que les films ALD HfAlO ont été obtenus avec succès. Les figures 2a et b présentent le I –V caractéristiques de commutation bipolaire des Ag/HfAlOx/Pt et TaN/HfAlOx/Pt mesurées par un analyseur de paramètres de dispositif à semi-conducteur Agilent B1500A. La tension de balayage a été appliquée de - 1,5 à 1,5 V (pour Ag) et - 3 à 3 V (pour TaN) et une tension de lecture de 0,1 V à température ambiante. Le rapport de résistance des structures Ag/HfAlOx/Pt et TaN/HfAlOx/Pt est illustré aux Fig. 3a et b. Un dispositif avec Ag comme électrode supérieure peut avoir un rapport de résistance de 103 et TaN car l'électrode supérieure peut atteindre 60. Les électrodes supérieures Ag et TaN présentent des caractéristiques de commutation bipolaire supérieures. La distribution de la tension de fonctionnement de réglage et de réinitialisation est présentée sous forme d'histogrammes sur les figures 3c et d, respectivement. Les dispositifs Ag/HfAlOx/Pt présentent une tension SET beaucoup plus faible. Les performances des deux structures sont comparées. La plage de tension SET et RESET des dispositifs Ag/HfAlOx/Pt était de 0,33 à 0,62 V et de - 1,3 à - 1,5 V et les dispositifs TaN/HfAlOx/Pt étaient de 0,8 à 1,8 V et de - 1,3 à - 2 V Après comparaison, il a été constaté que le dispositif utilisant Ag comme électrode supérieure est plus approprié comme dispositif de mise en œuvre de la logique en raison d'une meilleure stabilité et d'une tension de fonctionnement inférieure.

Caractéristiques courant-tension typiques de Ag/HfAlOx/Pt (a ) et appareils TaN/HfAlOx/Pt (b )

Caractéristiques d'endurance et distribution de réglage/réinitialisation de Ag/HfAlOx/Pt (a , c ) et appareil TaN/HfAlOx/Pt (b , d ) sous 100 cycles de balayage CC consécutifs

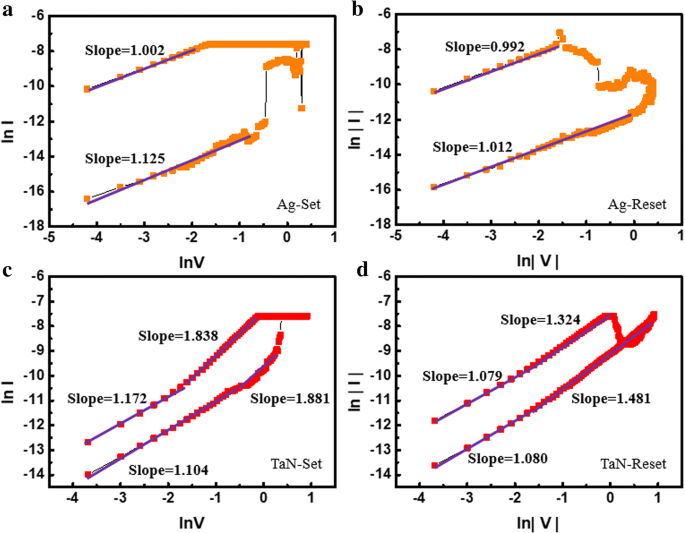

De plus, le mécanisme de commutation des deux types de structure est expliqué plus en détail. Le I–V les courbes sont analysées dans la Fig. 4a–d. Les courbes sont prises en coordonnées logarithmiques pour analyser l'état actuel dans les états de faible résistance (LRS) et de haute résistance (HRS), respectivement. Il est montré sur les Fig. 4a et b que le transport de courant des dispositifs Ag/HfAlOx/Pt présente un courant ohmique pendant le balayage de tension. Qu'il s'agisse d'appliquer une tension directe ou d'appliquer une tension négative pour les dispositifs TaN/HfAlOx/Pt illustrés aux Fig. 4c et d, le courant quasi-ohmique (la pente est approximativement égale à 1) est présenté dans le LRS, tandis que le courant ohmique, quasi-ohmique, et le courant de charge d'espace limité est présenté en HRS à champ électrique positif.

Le montage actuel des appareils Ag/HfAlOx/Pt sous a positif et b les champs électriques négatifs et le montage actuel des appareils TaN/HfAlOx/Pt sous c positif et d champs électriques négatifs

La raison de ce phénomène est que le mécanisme de changement de résistance des dispositifs TaN/HfAlOx/Pt est dû à la génération d'avalanches et à la recombinaison de l'ion oxygène et de la couche diélectrique de lacunes d'oxygène. Dans les dispositifs Ag/HfAlOx/Pt, la formation et la rupture des filaments conducteurs, grâce aux réactions redox de l'Ag métallique, peuvent être entraînées par un champ électrique beaucoup plus faible.

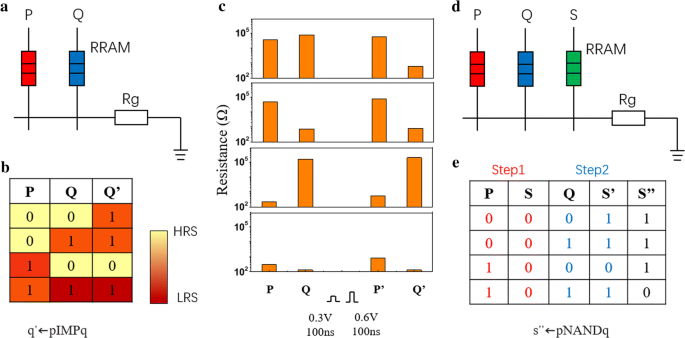

Dans cette expérience, l'état à faible résistance (LRS) a été défini comme la logique 1 et l'état à haute résistance (HRS) comme la logique 0. Le schéma de test de la logique IMP est illustré à la Fig. 5a. Il est implémenté par deux dispositifs RRAM P et Q et une résistance de charge fixe. Les états de P et Q sont représentés par p et q, respectivement. L'IMP est réalisé par deux impulsions de tension simultanées :Va et Vb (nous avons défini Va > Vset > Vb et Va – Vb < Vset afin que Va puisse programmer la logique 0 à 1 et Va − Vb ne puisse pas programmer la logique). Le principe du changement logique p est dû à q. Si q est égal à 1, alors p reste inchangé car la chute de tension aux bornes de p est proche de Va − Vb, et si q est égal à 0, le p est toujours égal à 1. La table de vérité pour l'opération q ← pIMPq est illustrée à la Fig. 5b et les changements d'état de P et Q avec l'impulsion sont représentés sur la figure 5c. La logique NAND peut être obtenue via la logique IMP en deux étapes. La mise en œuvre de la logique NAND peut être effectuée par une logique IMP en deux étapes, en raison de la bonne uniformité. La NAND est considérée comme une logique universelle, ce qui signifie qu'elle peut construire n'importe quelle logique booléenne via des portes NAND connectées topologiquement. Comme illustré sur la Fig. 5d, l'opération a été mise en œuvre dans un circuit avec trois dispositifs RRAM :P, Q et S. Les entrées étaient les valeurs p et q qui ont été stockées dans les dispositifs P et Q. Dans la première étape de l'exécution logique, S est initialisé à un état 0. Ensuite, deux étapes d'IMP ont été exécutées :

Le schéma de test d'IMP (a ) et NAND (d ) logique. b La table de vérité de l'opération q ← pIMPq (c ) et q ← pNANDq (e ). Les changements d'état de P et Q avec le pouls (c )

s′ ← pIMPs (1).

s′′ ← qIMPs′ (2).

Les tables de vérité montrant l'équivalence de la séquence d'opérations avec NAND sont présentées sur la figure 5e.

Conclusion

En résumé, deux types de dispositifs (Ag/HfAlOx/Pt et TaN/HfAlOx/Pt) ont été fabriqués dans cette étude. Les deux appareils présentent des caractéristiques de commutation supérieures. Le dispositif Ag/HfAlOx/Pt a démontré des avantages en tant que dispositif informatique en mémoire tels que la compatibilité CMOS, une bonne uniformité, une faible tension de fonctionnement et une faible consommation d'énergie. La logique a été implémentée via des dispositifs RRAM Ag/HfAlOx/Pt. La réalisation de dispositifs de calcul en mémoire à basse tension de fonctionnement fournit un moyen efficace de résoudre les difficultés de structure traditionnelles de von Neumann à l'avenir.

Abréviations

- ALD :

-

Dépôt de couche atomique

- HRS :

-

État de haute résistance

- LRS :

-

État de faible résistance

Nanomatériaux

- Repenser la modernisation des applications pour les DSI avec Google Cloud Platform

- Meilleures pratiques de sécurité pour le Fog Computing

- ST :kit d'évaluation d'éléments sécurisés avec logiciel prêt à l'emploi pour les applications informatiques et IoT

- Infineon :nouveau capteur de courant pour applications industrielles couvre une plage de ±25 A à ±120 A

- Renesas :MCU RX72M avec prise en charge EtherCAT pour les applications industrielles

- American Control Electronics :variateur CC basse tension avec option de carte programmable encliquetable

- Distribution de médicaments à base de cellules pour les applications contre le cancer

- GE contribue au besoin de nouvelles applications industrielles avec la gamme Hornet

- Quelles sont les applications les plus courantes pour le courant alternatif ?