Amélioration des performances du périphérique TFT a-IGZO à l'aide d'un processus d'interface propre via des nano-couches Etch-Stopper

Résumé

Pour surmonter les obstacles technologiques et économiques du fond de panier d'affichage amorphe à base d'oxyde d'indium-gallium-zinc (a-IGZO) pour la production industrielle, un procédé CL-ES (clean etch-stopper) est développé pour fabriquer transistor à film (TFT) avec une uniformité et une reproductibilité améliorées sur des substrats de verre de 8,5e génération (2200 mm × 2500 mm). Par rapport au TFT à base d'a-IGZO avec une structure gravée par canal arrière (BCE), une nano-couche ES nouvellement formée (~ 100 nm) et une gravure simultanée de la nano-couche a-IGZO (30 nm) et source-drain La couche d'électrode est d'abord introduite dans un dispositif TFT basé sur un IGZO avec une structure CL-ES pour améliorer l'uniformité et la stabilité du dispositif pour un affichage sur grande surface. La mobilité des électrons à saturation de 8,05 cm 2 /V s et le V ème une uniformité de 0,72 V est réalisée sur le dispositif TFT basé sur a-IGZO avec la structure CL-ES. Dans les tests de fiabilité de contrainte d'éclairage de température de polarisation négative et de contrainte thermique de polarisation positive sous un biais de ± 30 V pendant 3 600 s, le V mesuré ème le décalage du dispositif structuré CL-ES a diminué de manière significative à - 0,51 et + 1,94 V, ce qui est bien inférieur à celui du dispositif structuré BCE (- 3,88 V, + 5,58 V). Les performances électriques du dispositif TFT à base d'a-IGZO avec structure CL-ES impliquent que le transfert économique d'un processus TFT à base de silicium vers le processus à base de semi-conducteur à oxyde métallique pour la fabrication d'écrans LCD est hautement réalisable.

Contexte

Un fond de panier à transistor à couche mince (TFT) avec une résolution plus élevée et une plus grande taille de panneau est fortement souhaité dans l'industrie des écrans plats. Un matériau semi-conducteur à haute mobilité électronique est crucial pour améliorer les performances du fond de panier TFT. En particulier, un fond de panier TFT à base de semi-conducteur oxyde métallique est considéré comme un candidat prometteur pour surmonter la limitation du fond de panier TFT à base de silicium en termes de flexibilité mécanique et de mobilité des électrons [1,2,3,4]. Bien qu'un fond de panier TFT à base de semi-conducteur à base d'oxyde métallique présente des propriétés prometteuses, la méthode de traitement avec un processus à faible coût pour le dépôt à grande échelle pour une application industrielle est toujours nécessaire [5].

L'oxyde d'indium-gallium-zinc amorphe (a-IGZO) est un excellent semi-conducteur d'oxyde métallique avec une mobilité électronique de saturation élevée (~ 5–10 cm 2 /V s) et un faible courant de coupure (< 10 pA) [6,7,8,9,10]. La méthode de production industrielle courante pour le fond de panier TFT basé sur a-Si:H est le processus de gravure à cinq masques (BCE). Cependant, le nano-film a-IGZO a une très faible résistance chimique aux agents de gravure typiques actuellement utilisés dans le processus BCE. En particulier, les nano-films a-IGZO seraient complètement gravés en quelques secondes lorsqu'ils sont exposés à un agent de gravure d'Al composé d'acide phosphorique, d'acide nitrique et d'acide acétique [11,12,13]. Cette gravure rapide et incontrôlable entrave l'adoption du processus BCE pour le fond de panier TFT basé sur un IGZO. Pour utiliser a-IGZO dans le fond de panier à structure BCE, la technologie de câblage Cu a été développée, en tant qu'agent de gravure utilisé dans le processus de câblage Cu, qui est basé sur H2 O2 , est beaucoup plus doux pour le nano-film a-IGZO que ceux utilisés dans le câblage Al [11, 13]. Malheureusement, le nano-film a-IGZO est toujours endommagé pendant le processus de câblage en Cu, même lorsqu'un agent de gravure plus doux est utilisé. Des agents de gravure encore plus doux causent des dommages à la surface du nano-film a-IGZO qui forme le canal arrière des dispositifs TFT. Ces dommages provoquent un effondrement du rapport de composition moléculaire stoechiométrique près de la surface du nano-film a-IGZO, entraînant une aggravation de l'uniformité de l'affichage sur grande surface et de la fiabilité du dispositif TFT. À ce jour, un processus conventionnel à six masques-gravure-bouchon (CV-ES) est développé pour fabriquer un fond de panier TFT basé sur un IGZO avec une structure de couche de fin de gravure (ESL) [14, 15]. Cependant, ce processus SE à six masques peut conduire à une faisabilité économique négative. De plus, ce nombre accru de couches de film mince augmenterait la zone de chevauchement intercouche et entraînerait une augmentation de la capacité parasite et une diminution du rapport d'ouverture [16,17,18]. Bien qu'un processus ES à cinq masques produisant un fond de panier TFT utilisant la technologie des demi-teintes et du décollement ait été signalé récemment, ce processus n'est pas accessible pour la production d'un fond de panier TFT à base d'IGZO, car la surface de leur couche active est toujours exposée à traiter des produits chimiques tels que le décapant et la résine photosensible dans la dernière étape, ce qui peut provoquer une contamination considérable de l'a-IGZO, réduisant ainsi la qualité du dispositif et le rendement de production [19,20,21]. Par conséquent, la méthode de production industrielle pour un fond de panier TFT basé sur un IGZO avec une uniformité et une stabilité élevées reste un défi.

Dans cet article, nous proposons un processus ES propre à cinq masques (CL-ES) via l'introduction de l'ESL pour la fabrication d'un fond de panier TFT basé sur un IGZO. Ce processus CL-ES nouvellement développé est hautement compatible avec le processus existant pour le dispositif BCE. Ce processus CL-ES est conçu pour avoir les mêmes masques que celui du processus BCE, ce qui garantit une perte de productivité négligeable du fond de panier AM-LCD TFT existant FAB. Un fond de panier basé sur un IGZO produit à l'aide du processus CL-ES dépose l'isolant de grille, la nano-couche IGZO et la nano-couche ES séquentiellement, puis forme un nouveau masque ESL par la méthode de gravure à sec. Cela pourrait empêcher la contamination de la nano-couche a-IGZO et de leur interface par l'agent de gravure, le décapant et le solvant. Ce nano-masque nouvellement formé contribue à améliorer l'uniformité et la stabilité du dispositif TFT. Comparé au dispositif conventionnel à structure BCE, le dispositif à base d'a-IGZO avec structure CL-ES présente des performances électriques améliorées, à savoir une mobilité des électrons à saturation plus élevée, un rapport d'ouverture élevé et une faible consommation d'énergie.

Méthodes/Expérimental

Fabrication d'un fond de panier TFT basé sur un IGZO

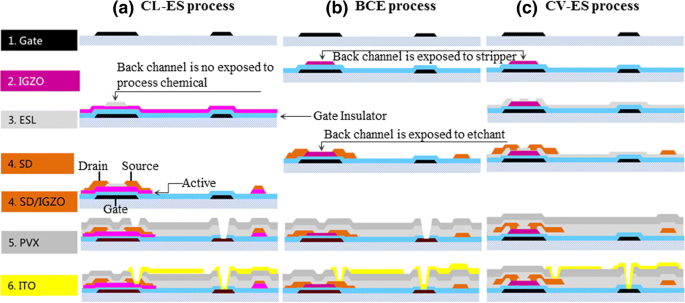

Le fond de panier TFT basé sur a-IGZO avec structure ES fabriqué via le processus CL-ES était le suivant (Fig. 1).

(Couleur en ligne) Schémas de a CL-ES, b BCE, et c Processus CV-ES

Premièrement, une double couche (Mo/Cu : 30 nm/250 nm) a été utilisée pour l'électrode de grille car elle a une résistivité raisonnablement faible. Ensuite, un isolant de grille, du nitrure de silicium (SiNx)/oxyde de silicium (SiOx) (300 nm/100 nm), a été déposé par la méthode de dépôt chimique en phase vapeur assisté par plasma (PECVD). Ce film SiNx est conçu pour empêcher l'oxydation de la métallisation Cu et la diffusion de l'ion Cu dans l'isolant de grille. Par la suite, un film mince de SiOx a été déposé. Les conditions de dépôt du film PECVD SiOx étaient une puissance RF de 17 KW, une pression de 1 000 mTorr, 1:55 SiH4 /N2 Rapport de gaz O et température de 350 °C. Ensuite, un nano-film a-IGZO a été déposé à 30 nm à l'aide d'une pulvérisation cathodique à magnétron rotatif à courant continu. La cible avait un diamètre de 171 mm alors que la composition était en In2 O3 :Ga2 O3 :ZnO = 1:1:1 % mol. Les paramètres de pulvérisation pour le nano-film a-IGZO étaient une pression de base du système de 5~ 9 × 10 -7 Torr, puissance de pulvérisation RF de 10 KW, pression de pulvérisation de 5 mTorr Ar/O2 mélange gazeux (85% Ar-15% O2 ). La température de dépôt est aux conditions ambiantes. Le film a-IGZO produit est recuit à 330 °C pendant 1 h dans un environnement d'air sec et propre.

Deuxièmement, une nano-couche d'arrêt de gravure (ES) (SiOx) a été déposée par la méthode PECVD. La nano-couche ES est déposée simultanément pour empêcher la contamination dans la couche a-IGZO. Comme dans le processus BCE, il n'y a pas de couche protectrice pour le nano-film a-IGZO avant le processus de structuration des électrodes S/D, la contamination de surface et les dommages sur le nano-film a-IGZO par gravure S/D lors de la formation du canal TFT sont inévitables. La nano-couche ES dans le processus CL-ES peut protéger efficacement le canal TFT contre la contamination et les dommages externes. La nano-couche ES a été déposée sur une épaisseur de 100 nm. Les conditions de dépôt du film mince de SiOx étaient une puissance RF de 17 KW, une pression de 1 000 mTorr, 1:66 SiH4 /N2 Ratio de gaz O et température de 240 °C. Le nano-masque ES produit a été gravé par gravure sèche et modelage. Pendant le processus de gravure, CF4 et O2 le gaz a été fourni à raison de 2000 scccm/800 scccm.

Troisièmement, Mo/Cu/Mo a également été utilisé pour l'électrode S/D. Pour sélectionner l'électrode S/D de l'a-IGZO TFT, la différence de travail d'extraction entre le métal et l'a-IGZO a été considérée pour former un contact ohmique et les matériaux à faible résistivité. Comme décrit dans le processus d'arrêt de gravure, lors de la structuration du nano-masque ES, les nano-films a-IGZO, qui ne sont pas protégés par la couche d'arrêt de gravure, sont déjà réalisés en étant bombardés de CF4 plasma. Par conséquent, le contact ohmique se forme naturellement avec Mo/Cu/Mo [22]. Les couches S/D ont été déposées dans l'épaisseur de 30 nm/300 nm/30 nm avec les mêmes conditions de pulvérisation cathodique que l'électrode de grille. De plus, des couches de film multi-mince de Mo/Cu/Mo et d'a-IGZO ont été gravées par lots à l'aide de « H2 O2 décapant à base de Cu contenant un additif fluoré » pour compléter l'électrode S/D. Les 30 nm de Mo ajoutés au-dessus de Cu ont été formés pour empêcher l'oxydation de la surface de Cu par un film de passivation (SiOx) dans le processus suivant et pour éviter d'endommager la surface de Cu par le plasma, lors de la gravure à sec pour la formation de trous de passivation.

Quatrièmement, un film de passivation, divisé en deux types de film mince, a été déposé en utilisant la méthode PECVD. La première passivation a été réalisée en couche mince de SiOx. Le film mince avait une épaisseur de 250 nm. La seconde passivation est constituée d'un film mince de SiNx. L'épaisseur du film mince était de 200 nm.

Cinquièmement, comme électrode de pixel, un film d'oxyde d'indium et d'étain (ITO), qui est le plus couramment utilisé dans l'industrie de l'affichage, a été utilisé. Le film d'ITO avait une épaisseur de 40 nm et une pulvérisation cathodique en courant continu a été utilisée pour le dépôt. Ensuite, le recuit final a été effectué dans un environnement d'air propre et sec à 230 °C pendant 1 h à l'aide d'un four à air chaud. Les caractéristiques électriques des TFT a-IGZO fabriqués ont été mesurées à l'aide du système de test paramétrique Keysight 4082A. Ce procédé permettra d'obtenir le même nombre de masques (norme produit TN :cinq masques) que le procédé BCE, largement utilisé dans la fabrication de masse.

À titre de comparaison, un fond de panier TFT basé sur un IGZO avec une structure BCE a été fabriqué via le processus BCE.

Caractérisation

La mesure I-V de TFT a été réalisée à température ambiante à l'aide d'un analyseur de caractéristiques à semi-conducteur. La condition d'analyse pour évaluer la stabilité du TFT sous une contrainte d'éclairage de température de polarisation de grille négative (NBTIS) était la suivante. V gs et V ds ont été respectivement fixés à - 30 et 15 V, et la température du substrat a été maintenue à 60 °C. La luminance pour NBITS a été fixée à 5000 cd/m 2 . La durée du stress pour l'évaluation s'est poursuivie pendant 3600 s [23]. Les contraintes thermiques de polarisation de grille positive (PBTS) ont été testées à un V gs de 30 V et un V ds de 15 V et la température du substrat a été fixée à 60 °C. La durée du stress pour l'évaluation s'est poursuivie pendant 3 600 s [24].

Résultats et discussion

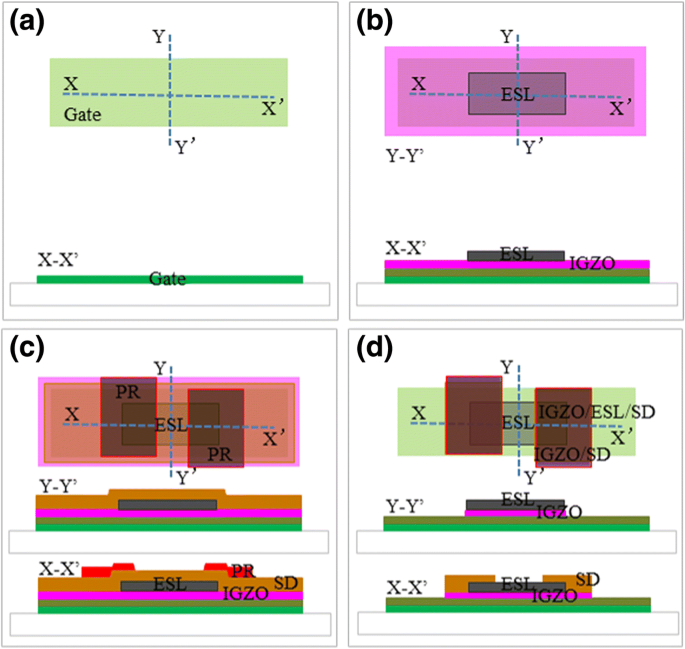

Le TFT basé sur a-IGZO fabriqué via le processus CL-ES montre le même numéro de masque que celui du processus BCE (Fig. 1). Comparé au TFT basé sur a-IGZO avec structure BCE, le TFT basé sur a-IGZO avec structure CL-ES présente deux avantages :-couche et nano-couche ES séquentiellement, puis forme un nano-masque ESL par la méthode de gravure à sec. Ce nano-masque ESL nouvellement formé avec 100 nm peut empêcher l'exposition du nano-film a-IGZO à un agent de gravure, un décapant ou une résine photosensible. Par conséquent, la contamination aux interfaces inter-couches est efficacement évitée [25]. (2) Dans le même temps, le nano-film a-IGZO n'est pas protégé par la couche ES mais bombardé par CF4 plasma lors de la formation du nano-masque ESL, devient ainsi un conducteur. Cela forme naturellement le contact ohmique entre l'électrode S/D du processus suivant et le semi-conducteur a-IGZO. Pour une autre partie, une gravure simultanée de la nano-couche S/D et a-IGZO peut être une allocation de superposition de la couche ESL-(métallisation a-IGZO + S/D), ce qui pourrait diminuer les deux erreurs de processus de superposition de l'a- Couche de métallisation IGZO-ESL et ES-S/D dans le procédé ESL conventionnel (Fig. 2). Le nombre de superpositions des couches a-IGZO, ES et S/D est réduit, ce qui a entraîné une diminution de la taille du dispositif TFT qui a réduit la capacité parasite. La structure planaire de résultat est similaire à la structure BCE (Fig. 3a, b).

(Couleur en ligne) Schémas de la méthode de formation simultanée pour le canal TFT et l'électrode S/D dans le processus CL-ES. un La première étape qui forme l'électrode de grille. b La deuxième étape qui forme la couche d'arrêt de gravure. c La troisième étape qui forme le motif photo S/D. d La quatrième étape qui forme l'électrode S/D et le motif actif

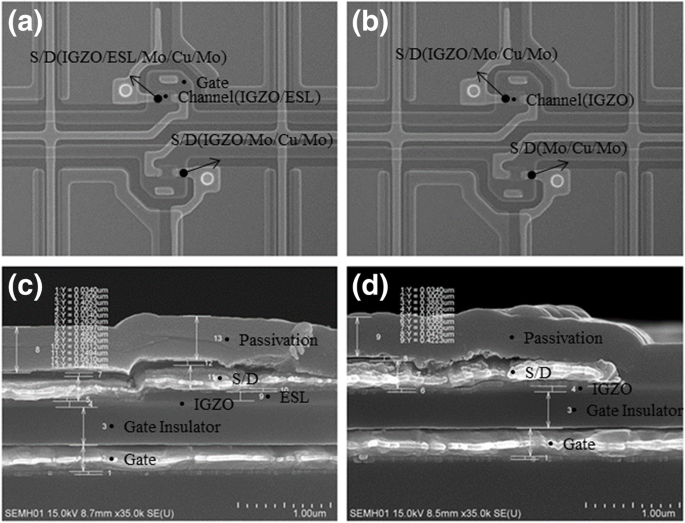

(Couleur en ligne) Images SEM de a-IGZO TFT (a , b vue de dessus ; c , d vue latérale) avec structure CL-ES (a , c ) et la structure BCE (b , d )

La figure 3 montre les images SEM des TFT basés sur a-IGZO avec une structure CL-ES (Fig. 3a, c) et une structure BCE (Fig. 3b, d). De la vue de dessus, il est difficile d'identifier les différences entre la structure CL-ES et la structure BCE (Fig. 3a, b). De la vue latérale, une nano-couche ES peut être trouvée entre la nano-couche a-IGZO et la couche d'électrode S/D dans la structure CL-ES (Fig. 3c). Pendant ce temps, une couche de passivation peut être trouvée sur le dessus de la nano-couche a-IGZO dans la structure BCE (Fig. 3d). Dans le processus CL-ES présenté, une nano-couche a-IGZO d'une épaisseur de 30 nm est déposée. De plus, les dommages lors de la gravure humide sont négligeables. Pour le processus BCE, une nano-couche a-IGZO de 70 nm est déposée, car la couche a-IGZO a besoin d'une compensation pour la perte de gravure. La différence entre les épaisseurs des nano-couches a-IGZO dans les structures CL-ES et BCE peut être observée sur les images SEM (Fig. 3c, d).

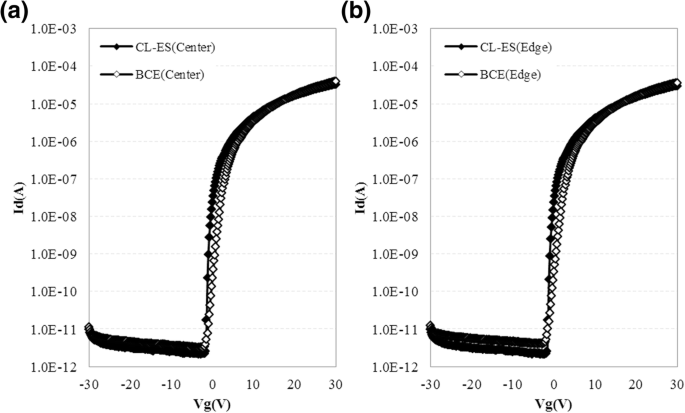

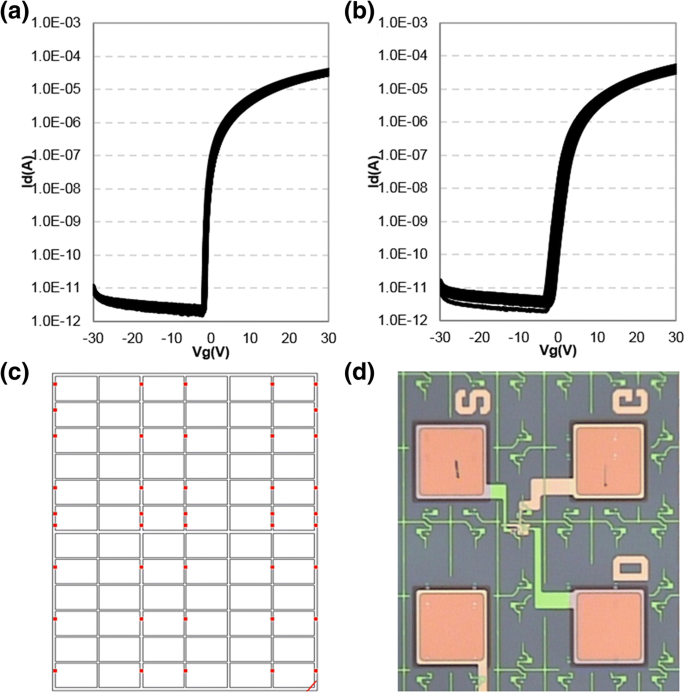

Les caractéristiques I-V d'un TFT basé sur un IGZO avec une structure CL-ES et une structure BCE sont comparées (Fig. 4). La mobilité des électrons de saturation, la tension de seuil, la valeur d'oscillation de tension sous le seuil (SS) et d'autres valeurs caractéristiques sont résumées dans le tableau 1. Notez que les valeurs résumées dans le tableau 1 sont le nombre moyen dérivé du centre et du bord d'un substrat de verre de génération 8,5 . Le TFT basé sur a-IGZO avec structure CL-ES réalise V ème de − 0,8 V, valeur SS de 0,18 V/déc et mobilité électronique à saturation de 8,05 cm 2 /Vs. Dans le TFT basé sur a-IGZO avec structure BCE, les résultats correspondants sont V ème de + 0,5 V, valeur SS de 0,77 V/déc et mobilité électronique à saturation de 6,03 cm 2 /Vs. Par rapport à la structure BCE, la structure CL-ES montre une amélioration des performances de l'appareil. Cependant, la caractéristique de courant du dispositif TFT basé sur a-IGZO avec structure CL-ES est inférieure à celle du dispositif structuré BCE. Cela est dû au fait que les structures de canaux TFT sont différentes dans les structures CL-ES et BCE. Généralement, la longueur du canal TFT structuré BCE correspond à la distance entre les électrodes métalliques S/D, et la longueur du canal mesurée dans cette étude est de 5 um [21]. Dans la structure CL-ES, les électrodes sont en contact avec le nano-film a-IGZO qui est étiré sur le côté du nano-masque ESL. Par conséquent, la longueur du canal est décidée par la distance entre les a-IGZO définis sur les côtés de l'arrêt de gravure, mais non déterminé par la distance entre les électrodes. La longueur de canal du dispositif actuel de structure CL-ES est mesurée à 10 um.

(Couleur en ligne) Comparaison de la caractéristique I-V des TFT a-IGZO avec la structure CL-ES et BCE au centre (a ) et bord (b ) de substrat de verre de génération 8.5

Comme indiqué dans le tableau 1, les valeurs mesurées de I sur /Je désactivé rapport (~ 10 6 , voir le tableau 1) sont environ 10 fois plus petites que la valeur typique (> 10 7 ) de TFT basés sur a-IGZO. En effet, l'équipement de mesure utilisé ici est destiné à la production en série de la génération 8.5. De longs câbles sont nécessaires pour ces mesures, car la taille de l'équipement industriel est importante. Les longs câbles ont entraîné une augmentation du bruit de mesure. Dans les tests de fiabilité suivants, un équipement de mesure à plus petite échelle est utilisé et les dispositifs TFT individuels sont utilisés comme spécimen pour la mesure. De cette façon, le I mesuré sur /Je désactivé les ratios sont tous supérieurs à 10 7 (voir ci-dessous).

Le processus CL-ES est soigneusement conçu pour empêcher la couche de canal a-IGZO d'être exposée à un agent de gravure, une résine photosensible ou un décapant. Pendant le processus qui produit le processus CL-ES, l'isolant de grille, la nano-couche a-IGZO et la nano-couche ES, chaque interface intercouche est en contact uniquement avec de l'eau DI à des fins de nettoyage. Par conséquent, la contamination chimique est négligeable dans la couche isolante et la nano-couche a-IGZO [25, 26]. Cependant, le processus BCE expose non seulement la couche de canal aux produits chimiques, mais implique également une contamination par diffusion d'ions Cu, car le canal a-IGZO est directement exposé au métal Cu. Ceci est également évité dans le dispositif avec la structure CL-ES. La région du canal du nano-film a-IGZO est bien protégée par le nano-masque ESL. La faible contamination chimique dans le processus CL-ES peut conduire à une faible densité de pièges porteurs à l'interface entre la nano-couche a-IGZO et la couche isolante, résultant en une excellente valeur SS. Cette faible contamination chimique du dispositif TFT à base d'a-IGZO via le processus CL-ES contribue également à améliorer l'uniformité et la reproductibilité du TFT a-IGZO, qui sont très importantes dans la production industrielle [27, 28].

La figure 5 montre la caractéristique I-V mesurée des TFT avec une structure CL-ES et une structure BCE dérivée de 42 points de mesure sur un substrat de génération 8,5. Le TFT basé sur a-IGZO avec la structure CL-ES a un V ème plage de 0,72 V, tandis que celle du dispositif à structure BCE est de 2,14 V (tableau 1). En d'autres termes, l'uniformité des performances de l'appareil est considérablement améliorée par la structure CL-ES.

(Couleur en ligne) a Structure CL-ES. b Caractéristique de transfert I-V des TFT de la structure BCE. c 42 points de mesure. d la photo de TFT. Le tout mesuré sur un substrat de génération 8.5

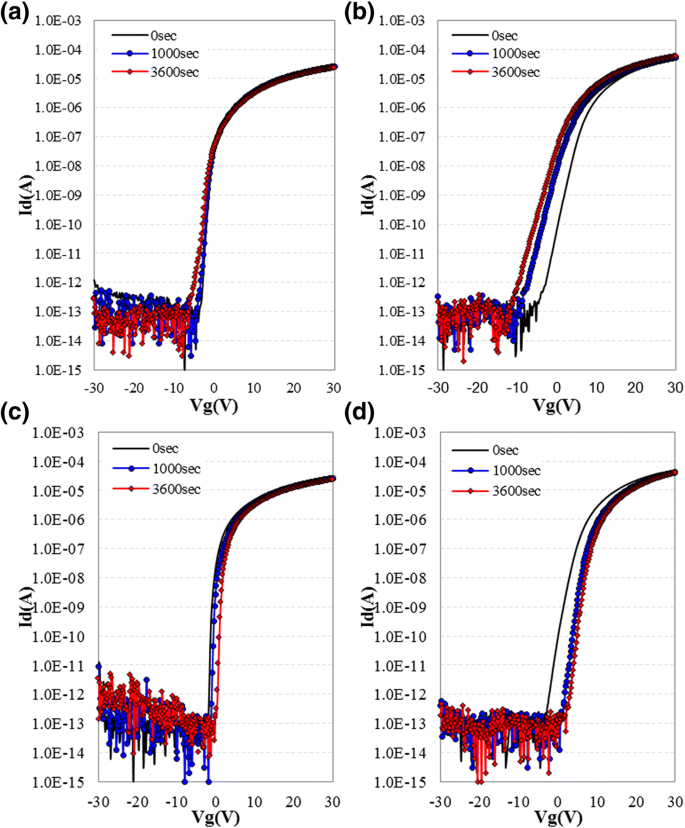

Les figures 6a, b montrent le décalage caractéristique I-V du dispositif structuré CL-ES et du dispositif structuré BCE obtenu lors des tests NBTIS, respectivement. Les résultats des tests NBTIS sont résumés dans le tableau 2. Dans la condition de stress décrite dans le tableau 2, le V ème le décalage du dispositif structuré CL-ES et du dispositif structuré BCE sont de - 0,51 et - 3,88 V, respectivement. De plus, le décalage en courant, le décalage hors courant et la variance de la valeur SS du dispositif structuré CL-ES sont tous inférieurs à ceux du dispositif structuré BCE (tableau 2) ; cela est dû au fait qu'un dispositif à base d'a-IGZO avec une structure CL-ES peut empêcher efficacement la contamination d'a-IGZO et une densité de piège à porteur inférieure du canal TFT a-IGZO. En particulier, lorsque l'on examine le résultat des 1000 premières s de stress, aucun changement de valeur SS n'est observé dans le dispositif structuré CL-ES. Ce phénomène est comparable à l'augmentation de 0,16 V/déc de la valeur SS du dispositif à structure BCE, car il montre que les sites défectueux, qui peuvent former des pièges à porteurs à la surface du nano-film a-IGZO constituant le canal arrière CL-ES TFT, ne sont pas créés en plus par les contraintes électriques et d'éclairage. Ces résultats prouvent pleinement que le dispositif structuré CL-ES est beaucoup plus stable que le dispositif structuré BCE. Les figures 6c, d montrent le décalage de courbe I-V des TFT structurés CL-ES et BCE obtenus à partir des tests PBTS. Les résultats détaillés des tests PBTS sont résumés dans le tableau 3. Le TFT structuré CL-ES et le TFT structuré BCE ont tous deux diminué le courant ionique au cours de l'évaluation PBTS. Ceci est causé par le décalage de V ème dans le sens positif. Au cours de l'évaluation PBTS, le rapport de courant ionique résiduel [(dernier ion/ion initial) × 100] du TFT structuré CL-ES avec un V relativement plus petit ème le décalage positif (+ 1,94 V) se situe au niveau de 88,2 %. Comparé au ratio de courant ionique résiduel du TFT structuré BCE de 41,3 %, le TFT structuré CL-ES est nettement supérieur. Cela montre la différence de capacité importante lors de la conception du circuit de commande de porte sur un réseau (GOA). Contrairement au NBTIS, la valeur SS du TFT structuré CL-ES n'a pas de variation significative ((∆SS 0,06 V/dec), ou plutôt diminue (∆SS − 0,86) comme celle du TFT structuré BCE. Cela est peut-être dû à la porteurs, s'accumulent dans l'espace interne et l'interface entre l'isolant de grille et le nano-film a-IGZO par polarisation de grille positive, remplissant le site de piège de porteur au stade précoce, provoquant une diminution du phénomène de piège de porteur.De plus, le phénomène de décalage de tension de seuil se produit par charge de porteur piégée près de l'interface entre l'isolant de grille et le nano-film a-IGZO. Le petit décalage de tension de seuil du TFT structuré CL-ES représente que l'interface et l'espace intérieur de l'a-IGZO sont remarquablement propres. En conclusion, les tests PBTS ont également suggère que la structure et le processus CL-ES conduisent à une meilleure fiabilité de l'appareil.

(Couleur en ligne) Dérive caractéristique de transfert I-V de CL-ES (a , c ) et BCE (b , d ) TFT obtenu de NBITS (a , b ) et les tests PBTS (c , d )

Conclusions

En conclusion, un processus CL-ES nouvellement développé a été développé avec succès pour fabriquer un fond de panier TFT basé sur un IGZO avec cinq masques pour un affichage avancé. Le processus CL-ES présente les avantages d'une structure de couche d'arrêt de gravure tout en maintenant le même nombre de masques et de zones de dispositifs similaires qu'un processus BCE, ce qui résout le problème du nombre accru de masques et de la zone occupée dans les dispositifs TFT à arrêt de gravure conventionnels. . Un nano-masque ESL nouvellement formé et une gravure simultanée de la nano-couche a-IGZO et de la nano-couche d'électrode S/D permettent une uniformité et une stabilité élevées du dispositif pour un affichage sur grande surface. En ce qui concerne les performances électriques, la reproductibilité et la fiabilité des performances du dispositif d'un TFT basé sur un IGZO avec une structure CL-ES sont bien meilleures que celles du dispositif structuré BCE. L'appareil TFT basé sur a-IGZO a un V ème distribution sur 42 points de mesure TFT sur substrat de verre de génération 8,5 de 0,72 V, mobilité électronique à saturation de 8,05 cm 2 /V s et une valeur SS de 0,18 V/déc. D'après les résultats d'évaluation de la fiabilité obtenus du NBTIS et du PBTS, V ème les variances avant et après la contrainte des TFT CL-ES a-IGZO sont de − 0,51 et 1,94 V après 3600 s de contrainte, respectivement. Les écarts de la valeur SS sont de 0,33 et 0,06 V/déc. Par conséquent, en surmontant les obstacles technologiques et économiques, la technique CL-ES présentée ouvrira la voie à la prochaine génération de produits d'affichage à haute résolution et à grand panneau.

Abréviations

- a-IGZO :

-

Oxyde d'indium-gallium-zinc amorphe

- AM-LCD :

-

Affichage à cristaux liquides à matrice active

- BCE :

-

Gravure du canal arrière

- ESL :

-

Couche d'arrêt de gravure

- GOA :

-

Lecteur Gate sur la baie

- NBTIS :

-

Contrainte d'éclairage de la température de polarisation négative

- PBTS :

-

Contrainte de température de polarisation positive

- SiNx :

-

Nitrure de silicium

- SiOx :

-

Oxyde de silicium

- SS :

-

Balançoire sous le seuil

- TFT :

-

Transistor à couche mince

- LCD TN :

-

Affichage à cristaux liquides nématiques torsadés

Nanomatériaux

- Utilisation de technologies sans eau dans le processus de teinture

- Commutateur de sélection de démarrage matériel à l'aide de Pico

- Utilisation de l'efficacité globale de l'équipement

- Stratégies de gestion des performances des actifs

- Utiliser la gestion des performances des actifs pour maximiser la valeur des actifs

- Ingénierie des procédés de revêtement par immersion et optimisation des performances pour les appareils électrochromes à trois états

- Composite hybride nanostructuré silice/or-cellulose Amino-POSS par procédé Sol-Gel et ses propriétés

- Utiliser une imprimante 3D pour améliorer votre processus de fabrication - Vidéo

- Avantages de l'utilisation de VIA dans les pads