Les solutions CXL 2.0 /PCIe 5.0 débloquent les goulots d'étranglement hétérogènes de calcul et de données

La startup de semi-conducteurs fabuleuse Astera Labs a annoncé de nouvelles solutions de connectivité CXL 2.0 et PCIe 5.0 spécialement conçues pour déverrouiller des architectures de calcul hétérogènes et gérer les charges de travail sensibles à la latence dans le centre de données. La société a déclaré que l'objectif de ces nouvelles solutions est de résoudre les goulots d'étranglement des performances à l'échelle du système dans les applications centrées sur les données.

La prolifération des données et l'intégration de charges de travail spécialisées - comme l'intelligence artificielle (IA) et l'apprentissage automatique (ML) - nécessitent des accélérateurs spécialement conçus pour fonctionner côte à côte avec des processeurs à usage général sur la même carte mère ou dans le même rack tout en partageant un espace mémoire commun. L'interconnexion CXL 2.0 est essentielle pour permettre de telles topologies système cohérentes avec le cache.

Le premier produit du nouveau portefeuille d'Astera Labs est son portefeuille de resynchronisation intelligente Aries Compute Express Link (CXL 2.0) (PT5161LX, PT5081LX) pour la connectivité CXL.io à faible latence, qui est activement échantillonné auprès de clients stratégiques. Le PDG de l'entreprise, Jitendra Mohan, a déclaré : « Avec notre expansion dans l'écosystème CXL, Astera Labs fait un nouveau pas de géant pour fournir des solutions spécialement conçues qui permettent de débloquer des topologies complexes de calcul hétérogène et de système de désagrégation composable. »

La spécification CXL 2.0 a été publiée par le CXL Consortium en novembre 2020. CXL est une interconnexion standard ouverte de l'industrie offrant une cohérence et une sémantique de mémoire utilisant une connectivité à bande passante élevée et à faible latence entre le processeur hôte et les périphériques tels que les accélérateurs, les mémoires tampons et les puces. Périphériques d'E/S. La spécification CXL 2.0 ajoute la prise en charge de la commutation pour le fan-out pour se connecter à plus de périphériques; mise en commun de la mémoire pour une utilisation plus efficace de la mémoire et fourniture de capacité de mémoire à la demande ; et la prise en charge de la mémoire persistante. Tout cela tout en préservant les investissements de l'industrie en prenant en charge la rétrocompatibilité totale avec CXL 1.1 et 1.0.

Le président du CXL Consortium, Barry McAuliffe, a déclaré :« En tant que membre du CXL Consortium, Astera Labs a apporté son expertise en matière de connectivité à l'avancement de la norme CXL. C'est formidable de voir sa première implémentation de silicium CXL arriver sur le marché pour soutenir un écosystème CXL à croissance rapide. »

Nouvelles solutions PCIe 5.0 en collaboration avec Intel

Astera Labs a également annoncé la disponibilité d'un nouveau mode à faible latence dans son portefeuille de resynchronisation intelligente Aries pour la connectivité PCIe avec les processeurs évolutifs Intel Xeon. Ce développement est le résultat d'une étroite collaboration avec Intel Corporation pour réduire davantage la latence des liaisons PCIe jusqu'à moins de 10 n et améliorer les performances des charges de travail centrées sur les données. Astera Labs a affirmé qu'il était le premier fournisseur à démontrer l'interopérabilité robuste de PCIe 5.0 avec les processeurs Intel Xeon Scalable nommés "Sapphire Rapids".

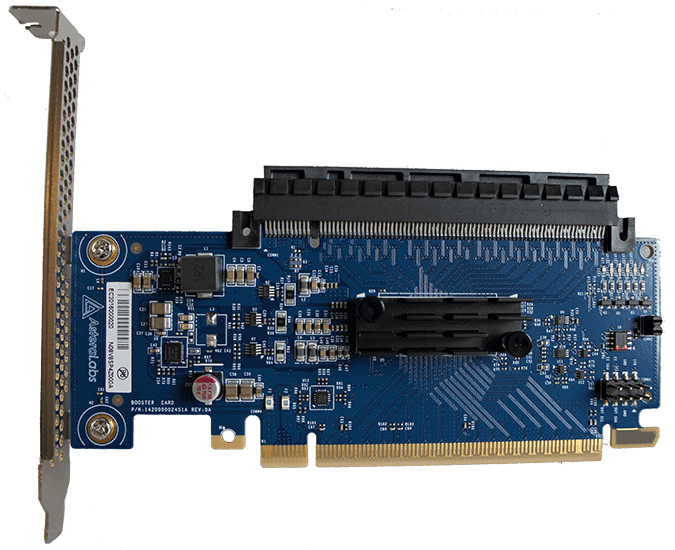

Une nouvelle carte d'extension plug-and-play Smart Retimer pour les applications PCIe/CXL, appelée Equinox, est également lancée en même temps. Également développées en partenariat avec Intel, la carte et le micrologiciel spécialement conçu à cet effet simplifieront le développement de systèmes compatibles PCIe 5.0 avec les derniers processeurs Xeon Scalable d'Intel. Cela représente la transition d'Astera Labs pour offrir des cartes plug-and-play faciles à utiliser pour mettre en œuvre rapidement des topologies de système complexes.

« PCIe Gen5 et CXL sont des technologies fondamentales pour les charges de travail de calcul hétérogènes et les architectures de centres de données d'aujourd'hui et de demain », a déclaré Zane Ball, vice-président de l'entreprise et directeur général de l'ingénierie et de l'architecture des centres de données chez Intel. "Intel collabore avec des leaders de l'écosystème comme Astera Labs pour réduire considérablement la latence d'interconnexion PCIe et CXL sur la prochaine plate-forme Intel Xeon Scalable nommée "Sapphire Rapids" et des plates-formes supplémentaires."

Contenus associés :

- Resynchronisation USB4 via USB-C

- Créer des interconnexions hautes performances avec plusieurs générations PCIe

- Xilinx cible le déchargement du centre de données avec du matériel « composable »

- Comment la superinformatique de périphérie transformera le grand déluge de données

Embarqué

- Problèmes juridiques liés au cloud computing et à leurs solutions

- DATA MODUL :solutions d'affichage dynamique orientées client présentées à l'ISE

- Micropuce :les tampons d'horloge sont conformes aux normes DB2000Q/QL ainsi qu'aux spécifications PCIe Gen 4 et 5 à faible gigue

- Apacer :SSD PCIe NVMe Gen3, la prochaine étape logique pour le stockage de qualité industrielle

- Swissbit :solutions de sécurité matérielles pour protéger les données et les appareils

- TECHWAY :plate-forme Kintex-7 FPGA PCIe pour augmenter les performances de débit de données avec 12 liens HSS

- Stratégie et solutions de l'armée pour la maintenance conditionnelle

- Les avantages de l'adaptation des solutions IIoT et d'analyse de données pour l'EHS

- Lutter contre les inondations dans les zones urbaines avec des solutions de réseau IoT