Conception et mise en œuvre de cartes de commutation d'interconnexion FDR haute densité

De nos jours, le taux de transmission du réseau d'interconnexion informatique haute performance avec l'application de la transmission série à haut débit s'est développé en FDR (Fourteen Data Rate, 14Gb/s), la 4ème génération du SDR primaire (Single Data Rate, 2.5Gb/ s), DDR (Double Data Rate, 5Gb/s) et QDR (Quad Data Rate, 10Gb/s). La conception de PCB (carte de circuit imprimé) avec interconnexion et carte de commutation et cartes d'interface qui sont essentielles à la formation d'Internet est entrée dans le domaine de la haute vitesse et de la haute fréquence FDR. Étant donné que le temps de montée du signal FDR a été considérablement réduit à l'ampleur de 10ps, une série de problèmes concernant l'intégrité du signal sont devenus les éléments clés pour déterminer la possibilité de mise en œuvre de fonctionnalités et un fonctionnement fiable, tels que l'atténuation, la diaphonie, la réflexion, les interférences électromagnétiques, etc. Sur la base des caractéristiques des puces d'interconnexion FDR, notamment plusieurs ports, plusieurs canaux, plusieurs catégories de puissance et une consommation d'énergie élevée, plusieurs puces d'interconnexion doivent toujours être intégrées sur une seule carte d'interconnexion afin d'augmenter le débit. Sur une carte avec un espace limité, d'une part, certaines exigences doivent être satisfaites, notamment la disposition des composants et la dissipation thermique, le routage à haute densité, la transmission longue distance à l'arrière de la carte et l'intégrité de toutes sortes de signaux. D'autre part, certains éléments doivent être pris en considération, notamment la période de conception des PCB, les limites de la technique de fabrication des PCB et le contrôle des coûts. Par conséquent, il est extrêmement difficile de mettre en œuvre la conception et de vérifier la simulation. Basé sur un exemple de conception de PCB d'interconnexion FDR et de carte de commutation, cet article propose des méthodes d'optimisation en termes de sélection de matériaux de substrat, de conception d'empilement, de règles de routage et de conception anti-interférence afin de résoudre le problème d'intégrité de toutes sortes de signaux dans le processus de conception de PCB haute vitesse FDR.

Attribut d'atténuation et sélection du matériau de substrat

Pour les signaux haute fréquence FDR, la perte de ligne de transmission est le problème concernant l'intégrité du signal. Lorsque les signaux FDR sont transmis du terminal émetteur au terminal récepteur le long des canaux d'interconnexion, étant donné que l'atténuation haute fréquence est beaucoup plus importante que l'atténuation basse fréquence, une déformation importante s'est produite sur la forme d'onde du signal arrivant au terminal récepteur. La déformation est principalement classée en deux aspects :l'oscillation de tension des signaux a fortement diminué tandis qu'une mauvaise dégradation s'est produite jusqu'au front de montée du signal. Le premier limite la distance de transmission des signaux tandis que le second conduit à des interférences entre codes. La perte de ligne de transmission A peut être considérée comme la somme de la perte de conducteur Acond et la perte diélectrique Adiel comme indiqué dans la formule (1) :A =Adiel + Acond .

La perte de conducteur fait référence à la perte causée par la résistance série sur le conducteur en cuivre entre le chemin du signal et le chemin de retour. Dans la situation de haute fréquence, l'effet de peau fait circuler le courant à la surface des conducteurs en cuivre environnants. Avec l'augmentation de la résistance série équivalente des conducteurs en cuivre, la perte de conducteur augmentera avec l'augmentation de la fréquence qui est positivement proportionnelle à la racine carrée de la fréquence, qui est illustrée dans la formule (2) : .

.

La perte diélectrique fait référence à la perte générée par le milieu du matériau du substrat, principalement déterminée par l'attribut du matériau et sans rapport avec la construction géométrique, y compris la largeur du conducteur, positive proportionnelle à la fréquence, qui est illustrée dans la formule (3) : .

.

Sur la base de la formule (2), l'augmentation de la largeur de ligne est capable de réduire la perte de conducteur. Cependant, dans la conception pratique des PCB, la largeur des conducteurs ne peut jamais être indéfiniment large en raison de la limitation de l'espacement entre les broches, la carte, le nombre de couches de signal et l'impédance. La largeur/l'espacement/la largeur des conducteurs couramment appliqués dans la conception FDR est généralement de 7 mil/7 mil/7 mil ou 8 mil/10 mil/8 mil. Lorsque la largeur du conducteur est la même, la perte du conducteur est positivement proportionnelle à la longueur du conducteur, sans aucune relation avec le matériau. Par conséquent, pour réduire la perte de transmission globale, seule la perte diélectrique doit être prise en compte. Sur la base de la formule (3), la perte diélectrique est proportionnelle au facteur de dissipation et l'application de petits facteurs de dissipation peut être utile pour réduire la perte diélectrique, entraînant la perte de transmission globale.

Le tableau 1 répertorie les paramètres d'attribut de trois matériaux de carte haute vitesse ordinaires et les valeurs de perte calculées selon les formules (1), (2) et (3) lorsque le taux de transmission est de 14 Gb/s, la largeur du conducteur de 8 mil et l'impédance de 50 Ω.

| Paramètres du matériau de la carte | FR4 | Nelco4000-13SI | Megtron6 |

| ADMIN@MFGROBOTS.COM | 0.02 | 0.008 | 0.004 |

| ADMIN@MFGROBOTS.COM | 4.10 | 3.200 | 3.600 |

| Acond @7GHz/po | 0.24 | 0.240 | 0.240 |

| Adiel @7GHz/po | 0.65 | 0.230 | 0.120 |

| ADMIN@MFGROBOTS.COM/in | 0,89 | 0.470 | 0.360 |

| ADMIN@MFGROBOTS.COM/30in | 27.00 | 14 000 | 11 000 |

| Coût relatif | 1.00 | 3.500 | 8 000 |

On peut indiquer qu'avec un taux de transmission de 14 Gb/s et une longueur de transmission de 30 pouces, la perte de transmission globale du Nelco4000-13SI est d'environ 14 dB tandis que l'atténuation de l'oscillation de tension que la puce FDR typique peut supporter est comprise entre 20 dB et 25dB. Par conséquent, ce type de matériau de carte peut être appliqué dans la conception de cartes de commutation d'interconnexion FDR avec une distance de transmission inférieure à 30 pouces. Cependant, l'atténuation de transmission globale de FR4 est d'environ 27 dB et FR4 ne peut pas être appliqué pour la conception FDR de conception longue distance, mais les cartes d'interface d'interconnexion FDR avec une courte distance de transmission sont autorisées à sélectionner FR4 pour réduire le coût. Quant au Megtron6 dont l'atténuation globale de transmission est la plus faible, il présente le coût le plus élevé et son application en FDR entraîne une augmentation des frais d'architecture du système. En conclusion, pour les PCB haute fréquence, le matériau de la carte est la base et la sélection du matériau de la carte détermine la longueur de transmission des signaux.

Mise en page et conception de la pile

Pour la conception des circuits imprimés, la structure et l'empilement des circuits imprimés doivent d'abord être pris en considération. Habituellement, le modèle et la forme de la carte de circuit imprimé ont été déterminés et la détermination du nombre de piles réside dans la fréquence du signal, la densité des broches de la carte de circuit imprimé, le coût de fabrication de la carte PCB, la période de fabrication et les exigences de fiabilité. Les cartes de commutation d'interconnexion FDR ont une fréquence et une densité élevées et l'application de cartes multicouches est l'étape nécessaire pour réduire les interférences. De plus, la détermination du numéro de pile est cruciale.

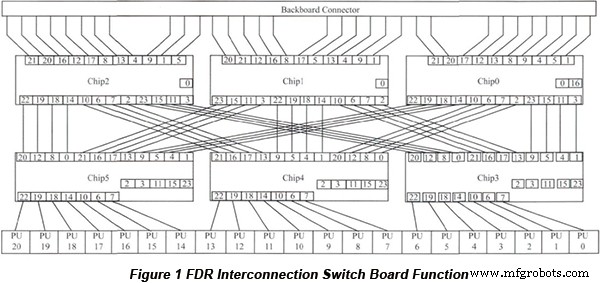

Il y a 24 ports sur la puce d'interconnexion FDR et chaque port comporte 8 canaux Tx et 8 canaux Rx dans la méthode de fonctionnement de l'intercouplage. 6 puces d'interconnexion et 3 puces de liaison descendante sont appliquées par la carte d'interconnexion FDR et 32 ports sont accessibles via le connecteur de la carte mère. 3 puces de liaison montante accèdent à 21 ports via des fibres optiques QSFP (Quad Small Form-factor Pluggable). La puce de liaison montante et la puce de liaison descendante sont connectées entre elles via 4 ports, comme illustré à la figure 1.

FDR comprend le package de BGA (Ball Grid Array) avec une zone de 50 mm x 50 mm, 1157 broches et un espacement de 1,0 mm et les broches P/N aux ports de Tx et Rx sont réparties selon 3 cercles concentriques. Théoriquement, 3 couches de signal peuvent être appliquées pour faire sortir toutes les broches de tous les ports du BGA. Avec les deux éléments suivants considérés, deux couches de signal peuvent être utilisées pour accéder à un groupe de broches de cercles concentriques.

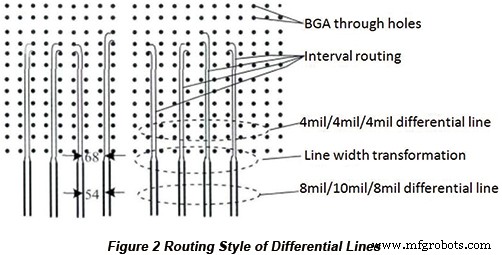

a. En raison de la limitation de l'espacement, la largeur de ligne/espacement/largeur des lignes différentielles est de 4mil/4mil/4mil et il sera étendu à 8mil/10mil/8mil sortant de BGA et la distance entre les paires de lignes différentielles ne doit pas être inférieure à 50 millions. Par conséquent, une paire de lignes différentielles doit occuper une largeur de 2 mm et 48 paires de signaux se trouvent le long du bord avec la plus grande densité. Il est donc difficile de mettre en œuvre cette méthode.

b. L'espacement entre les broches BGA est de 1 mm. Si une couche de signal est appliquée pour accéder à un groupe de signaux circulaires concentriques, l'espacement entre les paires de lignes différentielles sous BGA n'est que de 14 mil, ce qui est loin des 50 mil requis. De plus, la longueur maximale de routage parallèle n'est que de 20 mm, ce qui générera une certaine diaphonie.

Pour éviter les facteurs négatifs mentionnés ci-dessus, deux couches de signal sont appliquées pour accéder à un groupe de signaux circulaires concentriques et le signal différentiel à chaque couche de signal doit être sorti du BGA selon un espacement de 50 mil. Par conséquent, au moins 6 couches sont requises par les cartes d'interconnexion FDR pour que tous les signaux différentiels sortent du BGA. Avec la quantité de connectivité et de routage de la carte et une surface de carte suffisante pour le condensateur de couplage d'échange pris en compte, 8 signaux internes et une pile de 22 couches sont appliqués.

Analyse de la diaphonie et mesures de réduction

La diaphonie est la première considération en termes de conception de circuits à haute vitesse et haute densité. Lorsque la tension et le courant dans la ligne offensive changent, le couplage électromagnétique se produit par capacité mutuelle et inductance mutuelle entre la ligne offensive et la ligne victime. La diaphonie circulant vers le terminal de transmission le long de la ligne victime est appelée diaphonie proche du terminal tandis que la diaphonie circulant vers le terminal de réception le long de la ligne victime est appelée diaphonie lointaine. D'une manière générale, la tension de bruit globale sur la ligne victime doit être contrôlée à moins de 5 % de la tension du signal. Il est préférable de contrôler le budget de diaphonie de la ligne offensive à un seul bord à moins de 1 % avec une autre source de bruit et une ligne offensive autour des deux côtés de la ligne victime.

Les points clés à suivre en termes de réduction de la diaphonie incluent :

a. L'espacement entre la ligne offensive et la ligne victime doit être agrandi et la longueur du cheminement parallèle doit être réduite.

b. La masse intégrée est appliquée pour être le chemin de retour des signaux. Selon la loi empirique, pour la ligne triplaque de 50Ω, lorsque l'espacement est de trois fois la largeur de ligne, la paradiaphonie est d'environ 0,5%. Pour une ligne microruban de 50 Ω, lorsque l'espacement est égal à trois fois la largeur de la ligne, la paradiaphonie est d'environ 1 %. La diaphonie distante sur les lignes à bande ou les lignes microruban entièrement intégrées est presque nulle et la polarité de diaphonie distante des lignes de transmission microruban est négative avec une amplitude relativement grande car l'influence du couplage inductif est plus grande que le couplage capacitif.

• Routage par intervalles

Dans cette conception, l'impédance différentielle de la ligne différentielle à grande vitesse est de 100Ω. Basé sur le solveur de champ Si9000, la largeur de ligne/l'espacement/la largeur de ligne est calculé à 8mil/10mil/8mil. Plus la ligne est large, plus l'atténuation est petite et l'espacement de 10mil est de maintenir l'impédance différentielle de 100Ω. Ce type de ligne différentielle est appliqué en dehors de la zone de la puce BGA. Afin de réduire la diaphonie, l'espacement entre deux paires de lignes différentielles n'est pas inférieur à 80 mil. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Technologie industrielle

- Comment documenter les câbles et les harnais

- Qu'est-ce qu'un marteau perforateur ? - Types, conception et fonctionnement

- Cartes de circuits imprimés personnalisées de haute technologie

- Lignes directrices pour la conception RF et micro-ondes

- Matériaux et conception de PCB pour haute tension

- Capacités de courbure Flex et Rigid-Flex dans la conception de circuits imprimés

- Reculs et solutions dans la conception de circuits imprimés RF

- Tungstène

- Le processus de conception et de mise en œuvre de l'automatisation de l'usine