Une introduction rapide aux langages Verilog et HDL

Introduction :

Dans cet article, nous allons vous présenter VHDL et Verilog. Nous étudierons également la structure de base d'un module Verilog et nous familiariserons avec le type de données Verilog "wire" et sa forme vectorielle. Nous vous expliquerons également la différence fondamentale entre Verilog et VHDL.

Qu'est-ce que Verilog ?

Verilog est un type de langage de description de matériel (HDL), normalisé sous la norme IEEE 1364. Il est le plus couramment utilisé pour décrire les circuits et systèmes électroniques, utilisés dans la conception et la vérification des circuits numériques.

Qu'est-ce que le VHDL ?

VHDL est également un type de langage de description de matériel (HDL) utilisé dans l'automatisation de la conception électronique pour décrire le comportement et la structure des systèmes électroniques et est particulièrement adapté comme langage pour décrire la structure et le comportement des conceptions de matériel électronique numérique ainsi que circuits numériques conventionnels.

Ai-je besoin à la fois de Verilog et de VHDL ?

Avant de continuer, voyons si nous avons besoin de ces deux langues ? Les deux sont des outils puissants utilisés dans la conception de circuits numériques complexes, mais vous êtes libre d'en maîtriser un que vous souhaitez utiliser. Vous devez cependant avoir une compréhension de base des deux langues.

L'évolution de Verilog

Verilog a été conçu en 1984 chez Gateway Design Automation. En 1987, VHDL est devenu une norme IEEE tandis que Verilog est entré en scène en 1995. Aujourd'hui, ce sont tous deux de puissants HDL (Hardware Description Languages). Le mot « Verilog » est dérivé des mots « vérification » et « logique ». En effet, le langage a d'abord été utilisé comme outil de simulation et de vérification.

Nous allons maintenant discuter de certains concepts de Verilog.

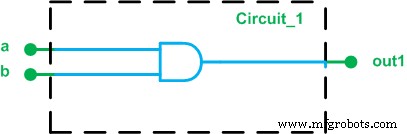

Exemple 1 :

Dans cet exemple, écrivons le code Verilog du circuit illustré ci-dessous.

Il y a deux entrées et une sortie est affichée et les ports ont une largeur d'un bit. Le circuit montre une fonction ET à partir des deux entrées résultant en une sortie sur le port out1. La description Verilog peut être affichée comme suit :

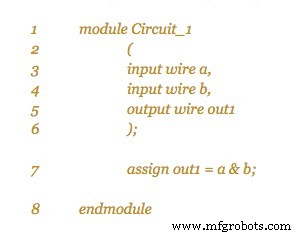

Lignes 1 et 8 :

Les mots clés 'module' et 'endmodule' sont utilisés pour spécifier les lignes entre eux qui décrivent le Circuit_1.

Lignes 2 à 6 :

Ces lignes précisent l'interface de 'Circuit_1' avec son environnement. Les mots clés 'input' et 'output' indiquent les ports d'entrée et de sortie. Après cela, le mot-clé 'wire' spécifie un type de données Verilog qui représente un fil physique dans la conception. Il y a trois fils a, b et out1 dans notre module.

Ligne 7 :

La ligne décrit la fonctionnalité AND du circuit avec l'opérateur AND au niveau du bit "&". Le mot-clé ‘attribuer ; est utilisé pour mettre a &b sur le port de sortie. Ceci est également connu sous le nom d'affectation continue car il est toujours actif chaque fois que l'expression change sur le côté droit, le côté gauche est réévalué, c'est-à-dire que sa sortie est mise à jour en permanence.

Comparaison de l'exemple 1 avec le code VHDL :

La figure ci-dessous montre les descriptions Verilog et VHDL pour le module Circuit_1.

En VHDL, nous devons inclure des bibliothèques qui définissent les types de données et les opérateurs. Par conséquent, le code VHDL est plus descriptif. Cependant, dans certains cas, cela est avantageux comme dans la modélisation de systèmes de niveau supérieur.

Système à quatre valeurs de Verilog :

Quatre valeurs sont utilisées dans les types de données Verilog :

- 0 :logique faible/faux

- 1 :logique élevée/vrai

- z :pour l'état à haute impédance (également utilisé pour décrire la sortie d'un tampon à trois états)

- x :valeur inconnue

Le type de données VHDL std_logic peut prendre neuf valeurs différentes, mais les valeurs couramment utilisées sont '0', '1', 'Z' et '-' ('-' indique une valeur inconnue).

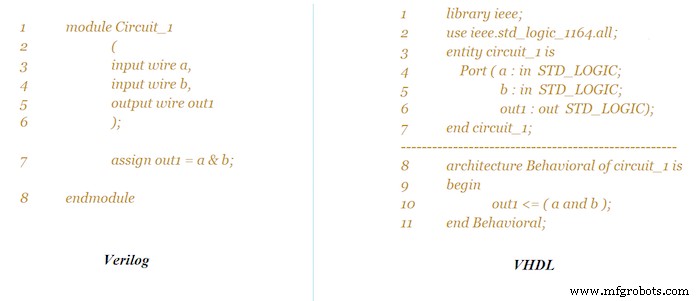

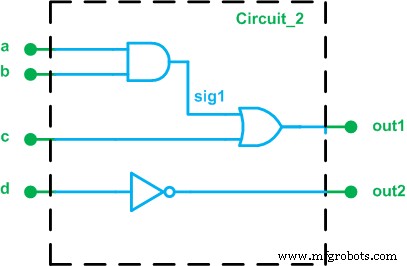

Exemple 2 :

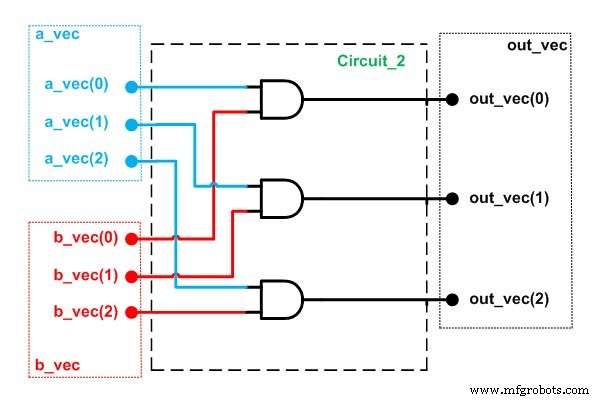

Dans l'exemple suivant, écrivons le code Verilog du circuit (Circuit_2) illustré dans la figure ci-dessous.

Le code Verilog suivant décrit le circuit illustré :

Les éléments utilisés sont similaires à ceux de notre exemple précédent, cependant, un signal interne est défini à la ligne 10. Le mot clé 'wire' spécifie le type de données de cette connexion. L'opérateur au niveau du bit "~" est utilisé pour NOT et "|" pour les opérations OR. L'opérateur au niveau du bit '^' est utilisé pour l'opération XOR.

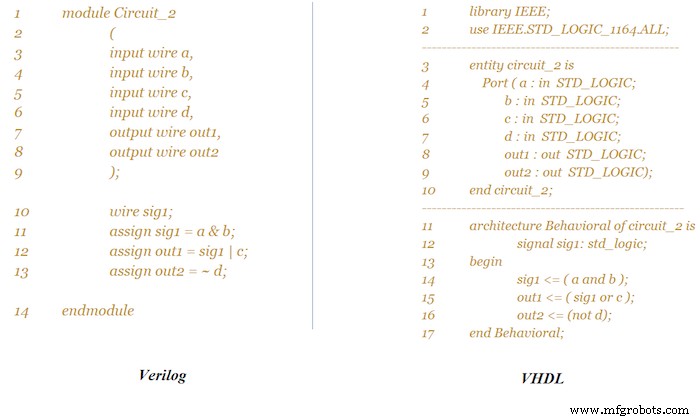

La figure suivante montre les descriptions Verilog et VHDL pour le module Circuit_2 afin que vous puissiez observer les différences.

Exemple 3 :

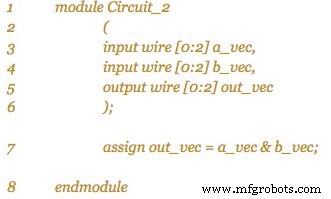

Pour notre troisième et dernier exemple, nous donnerons le code Verilog pour le schéma présenté dans la figure suivante : Vous remarquerez que les ports d'entrée rouge et bleu sont combinés avec l'opérateur AND. Le résultat est affiché par le port de sortie. Nous pouvons regrouper les signaux et les traiter comme un vecteur qui rendra notre code compact et lisible. Nous pouvons décrire le circuit ci-dessus en utilisant le code Verilog. Nous pouvons également facilement étendre le code du Listing 1 pour décrire ce circuit.

Vous remarquerez que les ports d'entrée rouge et bleu sont combinés avec l'opérateur AND. Le résultat est affiché par le port de sortie. Nous pouvons regrouper les signaux et les traiter comme un vecteur qui rendra notre code compact et lisible. Nous pouvons décrire le circuit ci-dessus en utilisant le code Verilog. Nous pouvons également facilement étendre le code du Listing 1 pour décrire ce circuit.

Gardez à l'esprit que la plage d'index des vecteurs peut être ascendante comme indiqué ([0:2]) ou descendante ([2:0]). Le format décroissant est généralement moins sujet aux erreurs et peut être utilisé à la place.

Technologie industrielle

- Une introduction aux œillets et à leur fonctionnement

- La chaîne d'approvisionnement et l'apprentissage automatique

- Kevlar 101 :qu'est-ce que c'est et quels sont les avantages ?

- La symbiose du commerce électronique et de la brique et du mortier

- Les roues du châssis tournent en rond… Pas

- Le guide rapide et sale des types de couplage de pompe

- Quelle est la différence entre l'industrie 4.0 et l'industrie 5.0 ?

- Les nombreux types de polyuréthane et leur utilisation

- Qu'est-ce qu'une fraiseuse et à quoi sert-elle ?