Fonction de porte de base

Pièces et matériaux

- Porte NAND quadruple 4011 (catalogue Radio Shack n° 276-2411)

- Interrupteur DIP à huit positions (catalogue Radio Shack n° 275-1301)

- LED graphique à barres à dix segments (catalogue Radio Shack n° 276-081)

- Une batterie 6 volts

- Deux résistances de 10 kΩ

- Trois résistances de 470

Attention ! Le 4011 IC est CMOS, et donc sensible à l'électricité statique !

Lectures complémentaires

Leçons En Circuits Électriques , Volume 4, chapitre 3 :« Portes logiques »

Objectifs d'apprentissage

- Objectif d'une résistance « pulldown »

- Comment déterminer expérimentalement la table de vérité d'une porte

- Comment connecter des portes logiques ensemble

- Comment créer différentes fonctions logiques en utilisant des portes NAND

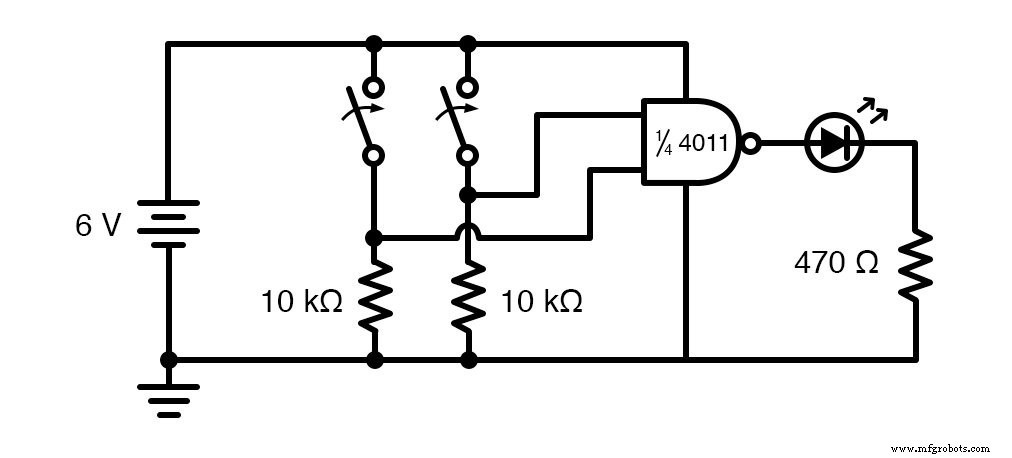

Diagramme schématique de la fonction de porte de base

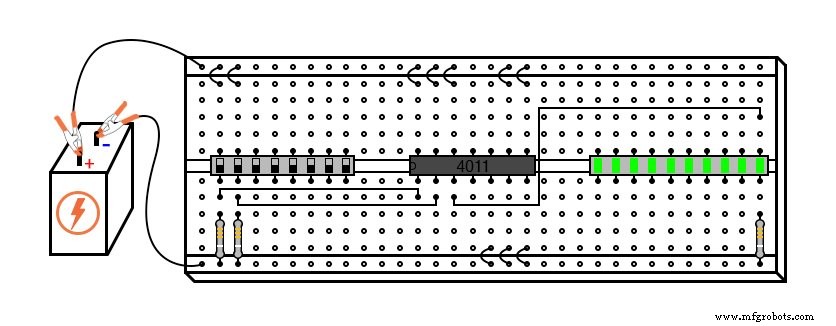

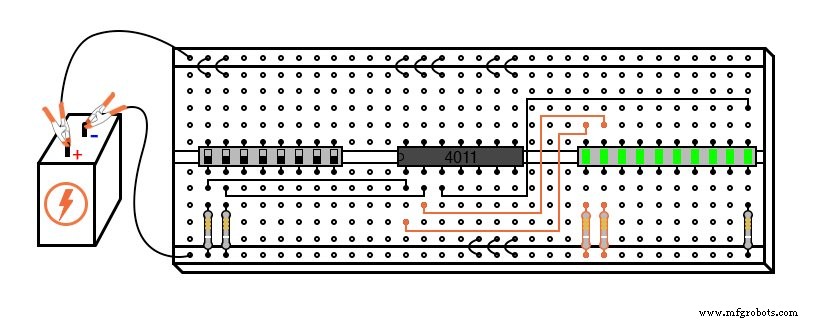

Illustration de la fonction de porte de base

Instructions d'expérimentation

Pour commencer, connectez une seule porte NAND à deux commutateurs d'entrée et à une LED, comme indiqué. Au début, l'utilisation d'un interrupteur à 8 positions et d'un bargraphe à LED à 10 segments peut sembler excessive puisque seuls deux interrupteurs et une LED sont nécessaires pour montrer le fonctionnement d'une seule porte NAND. Cependant, la présence de ces commutateurs et LED supplémentaires rend très pratique l'extension du circuit et contribue à rendre la disposition du circuit à la fois propre et compacte.

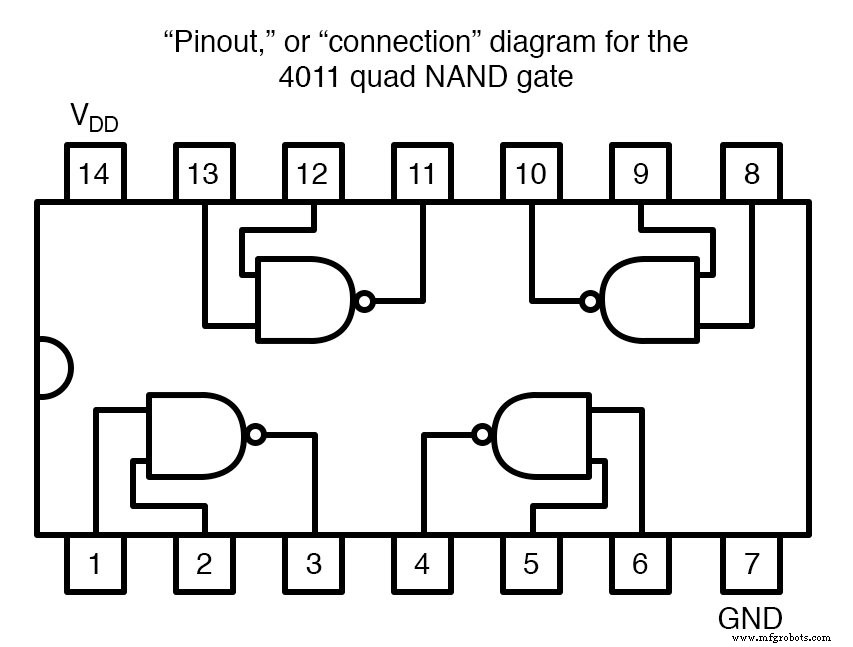

Il est fortement recommandé d'avoir une fiche technique pour le 4011 puce disponible lorsque vous construisez votre circuit. Ne vous contentez pas de suivre l'illustration ci-dessus ! Il est important que vous développiez l'habileté de lire les fiches techniques, en particulier les schémas de «brochage» lors de la connexion des bornes IC à d'autres éléments de circuit. Le schéma de connexion de la fiche technique est une information essentielle à avoir. Montré ici est ma propre interprétation de ce que n'importe quel 4011 la fiche technique montre :

Dans l'illustration de la maquette, j'ai montré le circuit construit à l'aide de la porte NAND en bas à gauche :les broches 1 et 2 sont les entrées et la broche 3 est la sortie. Les broches 14 et 7 conduisent le courant continu vers les quatre circuits de porte à l'intérieur de la puce IC, "VDD " représentant le côté positif de l'alimentation (+V), et "Gnd" représentant le côté négatif de l'alimentation (-V), ou la masse. Parfois, la borne d'alimentation négative sera étiquetée « VSS " au lieu de " Gnd " sur une fiche technique, mais cela signifie la même chose.

Les circuits logiques numériques n'utilisent pas d'alimentations séparées comme le font les amplificateurs opérationnels. Comme les circuits d'amplificateurs opérationnels, cependant, la terre est toujours le point de référence implicite pour toutes les mesures de tension. Si je devais parler d'un signal « élevé » présent sur une certaine broche de la puce, je voudrais dire qu'il y avait une tension maximale entre cette broche et le côté négatif de l'alimentation (masse).

Notez comment toutes les entrées des portes inutilisées à l'intérieur du 4011 puce sont connectés soit à VDD ou au sol. Ce n'est pas une erreur, mais un acte de conception intentionnelle. Depuis le 4011 est un circuit intégré CMOS, et les entrées du circuit CMOS ne sont pas connectées (flottantes ) peut assumer n'importe quel niveau de tension simplement en interceptant une charge électrique statique d'un objet à proximité, laissant les entrées flottantes signifie que ces portes inutilisées peuvent recevoir des combinaisons aléatoires de signaux « élevés » et « bas ».

Pourquoi est-ce indésirable, si nous n'utilisons pas ces portes ? Qui se soucie des signaux qu'ils reçoivent, si nous ne faisons rien avec leurs sorties ? Le problème est que si des signaux de tension statique apparaissent aux entrées de grille qui ne sont pas complètement « élevés » ou complètement « bas », les transistors internes des grilles peuvent commencer à s'allumer de manière à tirer un courant excessif. Au pire, cela pourrait endommager la puce.

Au mieux, cela signifie une consommation d'énergie excessive. Peu importe si nous choisissons de connecter ces entrées gate inutilisées « high » (VDD ) ou « bas » (masse), tant que nous les connectons à l'un de ces deux endroits. Dans l'illustration de la maquette, je montre toutes les principales entrées connectées à VDD , et toutes les entrées du bas (des portes inutilisées) connectées à la terre. Cela a été fait simplement parce que ces trous de rail d'alimentation étaient plus proches et ne nécessitaient pas de longs cavaliers !

Veuillez noter qu'aucune des sorties de porte inutilisées ont été connectés à VDD ou au sol, et pour cause ! Si je devais faire cela, je forcerais peut-être une porte à assumer l'état de sortie opposé à celui qu'elle essaie d'atteindre, ce qui est une façon compliquée de dire que j'aurais créé un court-circuit. Imaginez une porte censée produire un niveau logique « élevé » (pour une porte NAND, cela serait vrai si l'une de ses entrées était « bas »).

Si une telle porte avait sa borne de sortie directement connectée à la terre, elle ne pourrait jamais atteindre un état « haut » (étant rendue électriquement commune à la terre via la connexion du fil de liaison). Au lieu de cela, son transistor de sortie supérieur (canal P) serait activé en vain, fournissant un courant maximal à une charge inexistante. Cela endommagerait très probablement le portail ! Les bornes de sortie de porte, de par leur nature même, génèrent leurs propres niveaux logiques et ne « flottent » jamais de la même manière que les entrées de porte CMOS.

Les deux résistances de 10 kΩ sont placées dans le circuit pour éviter les conditions d'entrée flottantes sur la grille utilisée. Avec un interrupteur fermé, l'entrée respective sera directement connectée à VDD et donc être « élevé ». Avec un interrupteur ouvert, le 10 kΩ "pulldown La résistance " fournit une connexion résistive à la terre, assurant un état " bas " sécurisé à la borne d'entrée de la porte. De cette façon, l'entrée ne sera pas sensible aux tensions statiques parasites.

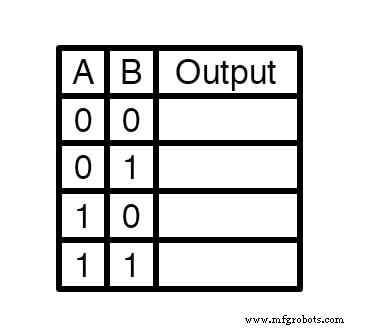

Avec la porte NAND connectée aux deux commutateurs et à une LED comme indiqué, vous êtes prêt à développer une « table de vérité » pour la porte NAND. Même si vous savez déjà à quoi ressemble une table de vérité de porte NAND, voici un bon exercice d'expérimentation :découvrir les principes comportementaux d'un circuit par induction. Dessinez une table de vérité sur une feuille de papier comme celle-ci :

Le « A » et « B » les colonnes représentent respectivement les deux commutateurs d'entrée. Lorsque l'interrupteur est allumé, son état est « haut » ou 1. Lorsque l'interrupteur est éteint, son état est « bas » ou 0, comme le garantit sa résistance de rappel. La sortie du gate, bien sûr, est représentée par la LED :qu'elle soit allumée (1) ou éteinte (0). Après avoir placé les commutateurs dans toutes les combinaisons d'états possibles et enregistré l'état de la LED, comparez la table de vérité résultante avec ce que devrait être la table de vérité d'une porte NAND.

Comme vous pouvez l'imaginer, ce circuit de maquette ne se limite pas à tester les portes NAND. Tout type de porte peut être testé avec deux commutateurs, deux résistances pulldown et une LED pour indiquer l'état de la sortie. Assurez-vous simplement de vérifier le schéma de « brochage » de la puce avant de la remplacer broche par broche à la place du 4011 . Toutes les puces de porte « quad » n'ont pas les mêmes affectations de broches !

Amélioration supplémentaire

Une amélioration que vous voudrez peut-être apporter à ce circuit est d'affecter quelques LED pour indiquer l'état de l'entrée, en plus de la LED affectée pour indiquer la sortie. Cela rend le fonctionnement un peu plus intéressant à observer, et a l'avantage supplémentaire d'indiquer si un interrupteur ne se ferme pas (ou ne s'ouvre pas) en affichant le vrai signal d'entrée à la porte, plutôt que de vous forcer à déduire l'état d'entrée à partir de la position du commutateur :

FEUILLE DE TRAVAIL CONNEXE :

-

Feuille de travail de base sur les portes logiques

Technologie industrielle