Comment créer un vecteur de signal en VHDL :std_logic_vector

Le std_logic_vector type peut être utilisé pour créer des bus de signaux en VHDL. Le std_logic est le type le plus couramment utilisé en VHDL, et le std_logic_vector en est la version tableau.

Alors que le std_logic est idéal pour modéliser la valeur pouvant être portée par un seul fil, il n'est pas très pratique pour implémenter des collections de fils allant vers ou depuis des composants. Le std_logic_vector est un type composite, ce qui signifie qu'il s'agit d'une collection de sous-éléments. Signaux ou variables du std_logic_vector type peut contenir un nombre arbitraire de std_logic éléments.

Cet article de blog fait partie de la série de didacticiels VHDL de base.

La syntaxe pour déclarer std_logic_vector signaux est :signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

ousignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

où <name> est un nom arbitraire pour le signal et <initial_value> est une valeur initiale facultative. Le <lsb> est l'indice du bit le moins significatif, et <msb> est l'index du bit le plus significatif.

Le to ou downto spécifie la direction de la plage du bus, essentiellement son endianess. Bien que les deux fonctionnent aussi bien, il est plus courant pour le concepteur VHDL de déclarer des vecteurs en utilisant downto . Par conséquent, je vous recommande de toujours utiliser downto lorsque vous déclarez des vecteurs de bits pour éviter toute confusion.

Le code VHDL pour déclarer un signal vectoriel pouvant contenir un octet :signal MySlv : std_logic_vector(7 downto 0);

Le code VHDL pour déclarer un signal vectoriel pouvant contenir un bit :signal MySlv : std_logic_vector(0 downto 0);

Le code VHDL pour déclarer un signal vectoriel qui peut contenir zéro bit (une plage vide ):signal MySlv : std_logic_vector(-1 downto 0);

Exercice

Dans ce tutoriel vidéo, nous allons apprendre à déclarer std_logic_vector signaux et leur donner des valeurs initiales. Nous apprenons également à itérer sur les bits d'un vecteur à l'aide d'une boucle For pour créer un registre à décalage :

Le code final que nous avons créé dans ce tutoriel :

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

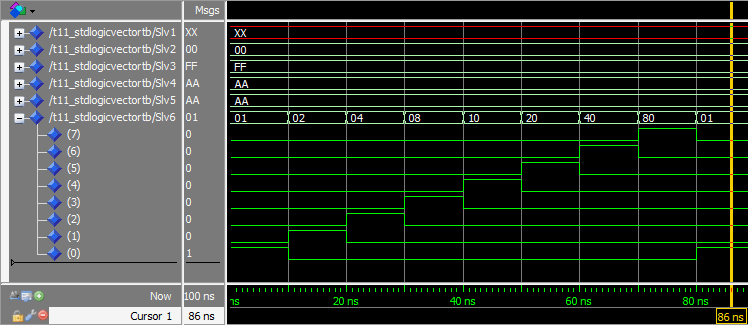

La fenêtre de forme d'onde dans ModelSim après avoir appuyé sur run et zoomé sur la timeline :

Analyse

Dans cet exercice, nous avons déclaré six std_logic_vector bus, chacun long de huit bits (un octet).

Signal Slv1 a été déclaré sans valeur initiale. Le bus est vu avec la valeur XX dans la capture d'écran de la forme d'onde. En effet, la valeur affichée sur le bus est en hexadécimal et XX indique une valeur non hexadécimale. Mais lorsque nous avons étendu le bus dans la forme d'onde, nous avons pu voir que les bits individuels étaient bien des U.

Signal Slv2 a été déclaré en utilisant une valeur initiale de tous les 0. Au lieu de spécifier la valeur exacte pour chaque bit, nous avons utilisé (other => '0') à la place de la valeur initiale. C'est ce qu'on appelle un agrégat mission. La partie importante est qu'il définira tous les bits du vecteur sur ce que vous spécifiez, quelle que soit sa longueur.

Signal Slv3 a été déclaré en utilisant une affectation agrégée pour donner à tous les bits la valeur initiale de 1. Nous pouvons voir FF affiché sur ce signal dans la forme d'onde, qui est hexadécimal pour huit 1.

Signal Slv4 a été déclaré avec une valeur initiale spécifiée en hexadécimal, AA. Chaque chiffre hexadécimal a une longueur de 4 bits, nous devons donc fournir deux chiffres (AA) pour notre vecteur qui a une longueur de 8 bits.

Signal Slv5 déclare exactement la même valeur initiale que Slv4 , mais maintenant nous l'avons spécifié comme valeur binaire 10101010. Nous pouvons voir sur la forme d'onde que les deux signaux ont la valeur hexadécimale AA.

Signal Slv6 a été déclaré avec une valeur initiale composée uniquement de zéros, à l'exception du bit le plus à droite qui était '1' . Nous avons utilisé un processus pour créer un registre à décalage à partir de ce signal. Le registre à décalage, comme son nom l'indique, décale le contenu du vecteur d'une place vers la gauche toutes les 10 nanosecondes.

Notre processus se réveille toutes les 10 ns et la boucle For décale tous les bits du vecteur d'une place vers la gauche. Le dernier bit est replacé dans le premier index par le Slv6(Slv6'right) <= Slv6(Slv6'left); déclaration. Dans la forme d'onde, nous pouvons voir le '1' ondulation à travers le vecteur.

Ceci est une visualisation de la façon dont le '1' se propage à travers notre registre à décalage :

En utilisant le 'left' et 'right attributs, nous avons rendu notre code plus générique. Si nous changeons la largeur de Sig6 , le processus fonctionnera toujours. C'est une bonne pratique de conception d'utiliser des attributs là où vous le pouvez au lieu de coder en dur des valeurs.

Vous vous demandez peut-être s'il existe d'autres attributs que vous pouvez utiliser, et il y en a. Je n'en parlerai pas davantage dans cette série de tutoriels, car je les considère comme des fonctionnalités VHDL avancées.

À emporter

- Les vecteurs de N bits doivent être déclarés en utilisant

std_logic_vector(N-1 downto 0) - Un vecteur peut être attribué dans son ensemble ou les bits qu'il contient peuvent être consultés individuellement

- Tous les bits d'un vecteur peuvent être mis à zéro en utilisant l'affectation agrégée

(others => '0') - Le code peut être rendu plus générique en utilisant des attributs tels que

'leftet'right

Répondez au Quiz VHDL de base – partie 2 »

ou

Passez au tutoriel suivant »

VHDL

- Exemples de conversions VHDL

- Signé ou non signé en VHDL

- Comment créer une liste de chaînes en VHDL

- Comment créer un banc d'essai piloté par Tcl pour un module de verrouillage de code VHDL

- Comment arrêter la simulation dans un testbench VHDL

- Comment créer un contrôleur PWM en VHDL

- Comment générer des nombres aléatoires en VHDL

- Comment créer un banc d'essai d'auto-vérification

- Comment créer une liste chaînée en VHDL