Registres à décalage :conversion en entrée parallèle, sortie en série (PISO)

Les registres à décalage d'entrée/sortie parallèle font tout ce que font les précédents registres à décalage d'entrée/sortie série, ainsi que les données d'entrée à tous les étages simultanément.

Le registre à décalage entrée parallèle/sortie série stocke les données, les décale horloge par horloge et les retarde du nombre d'étages multiplié par la période d'horloge.

De plus, l'entrée parallèle/la sortie série signifie vraiment que nous pouvons charger des données en parallèle dans toutes les étapes avant que tout changement ne commence.

C'est un moyen de convertir les données d'un parallèle formater en série format. Par format parallèle, nous entendons que les bits de données sont présents simultanément sur des fils individuels, un pour chaque bit de données, comme indiqué ci-dessous.

Par format série, nous entendons que les bits de données sont présentés séquentiellement dans le temps sur un seul fil ou circuit comme dans le cas de la « sortie de données » sur le schéma fonctionnel ci-dessous.

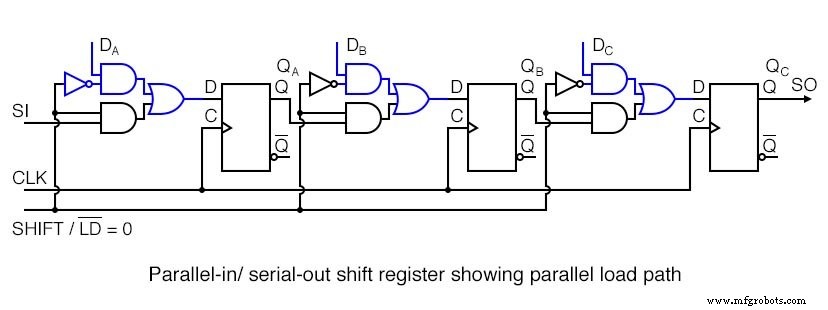

Ci-dessous, nous examinons de près les détails internes d'un registre à décalage à entrée parallèle/sortie série à 3 étages.

Une étape se compose d'un type D Flip-Flop pour le stockage, et un sélecteur AND-OR pour déterminer si les données seront chargées en parallèle, ou décaler les données stockées vers la droite.

En général, ces éléments seront répliqués pour le nombre d'étapes nécessaires. Nous montrons trois étapes en raison des limitations d'espace.

Quatre, huit ou seize bits sont normaux pour des pièces réelles.

Ci-dessus, nous montrons le chemin de charge parallèle lorsque SHIFT/LD' est logiquement bas. Les portes NAND supérieures desservant DA DB DC sont activés, en passant des données aux entrées D de type D Tongs QA QB DC respectivement.

Au prochain front d'horloge positif, les données seront cadencées de D à Q des trois FF. Trois bits de données seront chargés dans QA QB DC en même temps.

Le type de charge parallèle qui vient d'être décrit, où les données se chargent sur une impulsion d'horloge est appelée charge synchrone car le chargement des données est synchronisé avec l'horloge.

Cela doit être différencié de la charge asynchrone où le chargement est contrôlé par les broches prédéfinies et claires des tongs qui ne nécessitent pas d'horloge.

Une seule de ces méthodes de chargement est utilisée au sein d'un appareil individuel, la charge synchrone étant plus courante dans les appareils plus récents.

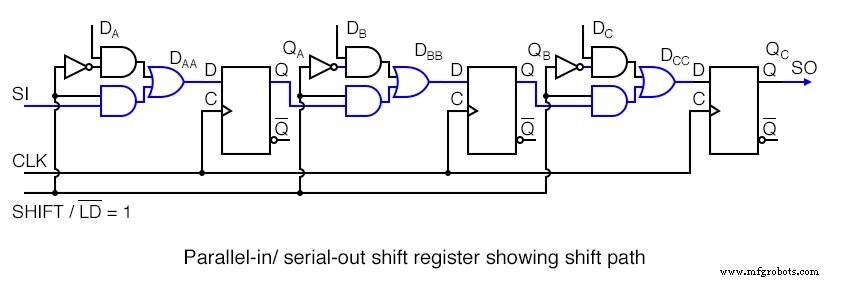

Le chemin de décalage est indiqué ci-dessus lorsque SHIFT/LD' est au niveau logique haut. Les portes ET inférieures des paires alimentant la porte OU sont activées nous donnant une connexion de registre à décalage de SI à DA , QR à DB , QB à DC , QC à SO. Les impulsions d'horloge entraîneront le décalage vers la droite des données en SO sur des impulsions successives.

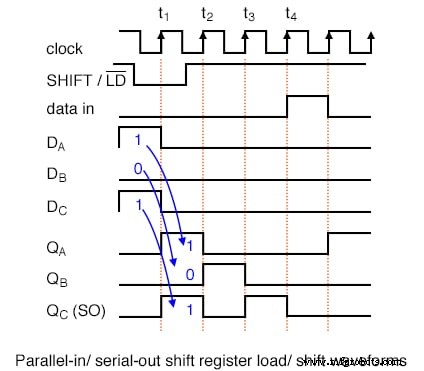

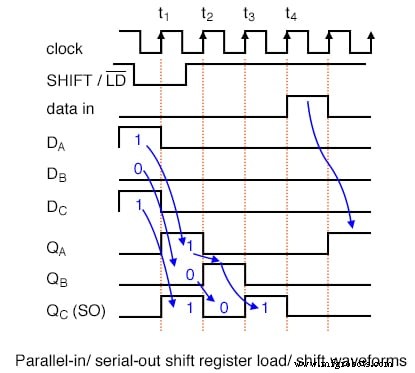

Les formes d'onde ci-dessous montrent à la fois le chargement parallèle de trois bits de données et le décalage en série de ces données. Données parallèles à DA DB DC est converti en données série à SO.

Ce que nous avons décrit précédemment avec des mots pour le chargement et le décalage parallèles est maintenant défini comme des formes d'onde ci-dessus.

À titre d'exemple, nous présentons 101 aux entrées parallèles DAA DBB DCC . Ensuite, le SHIFT/LD' diminue, ce qui permet de charger des données plutôt que de déplacer des données.

Il doit être bas peu de temps avant et après l'impulsion d'horloge en raison des exigences de configuration et de maintien. Il est considérablement plus large qu'il ne doit l'être.

Cependant, avec la logique synchrone, il est pratique de l'élargir. Nous aurions pu faire le SHIFT/LD' bas actif sur presque deux horloges de large, bas presque une horloge avant t1 et retour haut juste avant t3 .

Le facteur important est qu'il doit être faible autour de l'heure t1 pour permettre le chargement parallèle des données par l'horloge.

Notez qu'à t1 les données 101 à DA DB DC est cadencé de D à Q des tongs comme indiqué à QA QB QC à l'instant t1 .

C'est le chargement parallèle des données synchrone avec l'horloge.

Maintenant que les données sont chargées, nous pouvons les décaler à condition que SHIFT/LD' soit élevé pour permettre le décalage, ce qui est antérieur à t2 .

À t2 les données 0 à QC est décalé de SO qui est le même que le QC forme d'onde. Il est soit déplacé dans un autre circuit intégré, soit perdu s'il n'y a rien de connecté au SO.

Les données à QB , un 0 est déplacé vers QC . Le 1 à QA est décalé dans QB . Avec "données dans" un 0 , QR devient 0 . Après t2 , QR QB QC =010 .

Après t3 , QR QB QC =001 . Ce 1 , qui était à l'origine présent à QA après t1 , est désormais présent chez SO et QC .

Le dernier bit de données est transféré vers un circuit intégré externe s'il existe. Après t4 toutes les données du chargement parallèle ont disparu.

A l'horloge t5 nous montrons le déplacement d'une donnée 1 présent sur le SI, entrée série.

Q :Pourquoi fournir des broches SI et SO sur un registre à décalage ?

R :Ces connexions nous permettent de mettre en cascade des étages de registre à décalage pour fournir des décalages plus importants que ceux disponibles dans un seul boîtier IC (circuit intégré). Ils permettent également des connexions série vers et depuis d'autres circuits intégrés tels que des microprocesseurs.

Examinons de plus près les registres à décalage entrée parallèle/sortie série disponibles sous forme de circuits intégrés, avec l'aimable autorisation de Texas Instruments.

Pour les fiches techniques complètes des appareils, suivez ces liens.

Périphériques à entrée parallèle/sortie série

- SN74ALS166 registre à décalage 8 bits entrée parallèle/sortie série, charge synchrone

- Registre à décalage 8 bits entrée parallèle/sortie série SN74ALS165, charge asynchrone

- CD4014B registre à décalage 8 bits entrée parallèle/sortie série, charge synchrone

- Registre à décalage 16 bits entrée parallèle/sortie série SN74LS647, charge synchrone

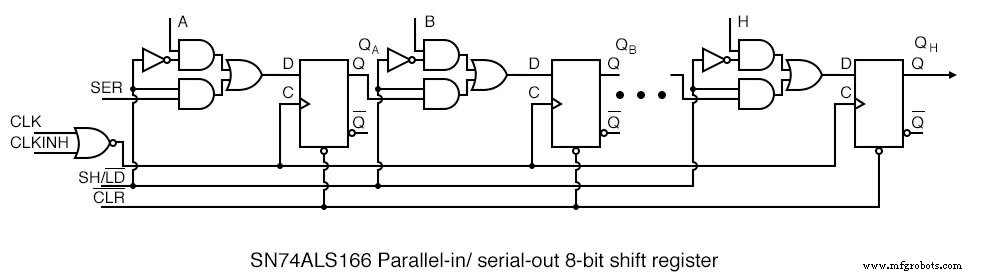

Le SN74ALS166 illustré ci-dessus est la correspondance la plus proche d'une pièce réelle avec les chiffres précédents du levier de vitesses parallèle-in/série.

Notons les modifications mineures apportées à notre figure ci-dessus. Tout d'abord, il y a 8 étapes. Nous n'en montrons que trois.

Les 8 étapes sont indiquées sur la fiche technique disponible sur le lien ci-dessus. Le fabricant étiquette les entrées de données A, B, C, etc. en H.

La commande SHIFT/LOAD est appelée SH/LD’. Il est abrégé de notre terminologie précédente, mais fonctionne de la même manière :charge parallèle si faible, décalage si élevé.

L'entrée de décalage (entrée de données série) est SER sur l'ALS166 au lieu de SI. L'horloge CLK est commandée par un signal d'inhibition CLKINH.

Si CLKINH est haut, l'horloge est inhibée ou désactivée. Sinon, cette « partie réelle » est la même que ce que nous avons examiné en détail.

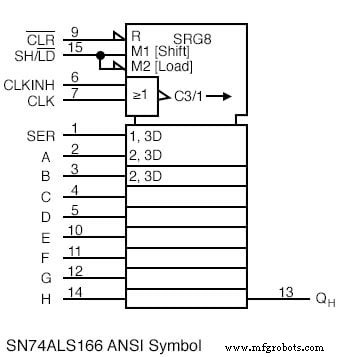

Ci-dessus se trouve le symbole ANSI (American National Standards Institute) pour le SN74ALS166 tel qu'indiqué sur la fiche technique.

Une fois que nous savons comment fonctionne la pièce, il est pratique de masquer les détails dans un symbole. Il existe de nombreuses formes générales de symboles.

L'avantage du symbole ANSI est que les étiquettes fournissent des indications sur le fonctionnement de la pièce.

Le grand bloc cranté en haut du '74ASL166 est la section de contrôle du symbole ANSI. Il y a une réinitialisation signalée par R .

Il existe trois signaux de contrôle :M1 (Maj), M2 (Charge), et C3/1 (flèche) (horloge bloquée). L'horloge a deux fonctions.

Tout d'abord, C3 pour déplacer des données parallèles partout où un préfixe de 3 apparaît. Deuxièmement, chaque fois que M1 est affirmé, comme indiqué par le 1 de C3/1 (flèche) , les données sont décalées comme indiqué par la flèche pointant vers la droite.

La barre oblique (/) est un séparateur entre ces deux fonctions. Les étapes à 8 équipes, comme indiqué par le titre SRG8 , sont identifiés par les entrées externes A, B, C, à H .

Le 2, 3D interne indique que les données, D , est contrôlé par M2 [Charger] et C3 horloge. Dans ce cas, on peut conclure que les données parallèles sont chargées de manière synchrone avec l'horloge C3 .

L'étage supérieur à A est un bloc plus large que les autres pour accueillir l'entrée SER .

La légende 1, 3D implique que SER est contrôlé par M1 [Maj] et C3 horloge. Ainsi, nous prévoyons de pointer les données à SER lors du déplacement par opposition au chargement parallèle.

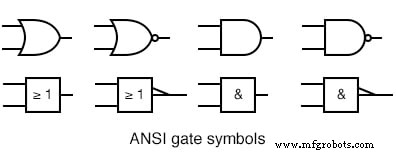

La porte de base ANSI/IEEE symboles rectangulaires sont fournis ci-dessus à des fins de comparaison avec les symboles de forme plus familiers afin que nous puissions déchiffrer le sens de la symbologie associée au CLKIN H et CLK broches sur le symbole ANSI SN74ALS166 précédent.

Le CLK et CLKINH alimentent un OU porte sur le symbole ANSI SN74ALS166. OU est indiqué par => sur le symbole rectangulaire inséré.

Le long triangle à la sortie indique une horloge. S'il y avait une bulle avec la flèche, cela aurait indiqué un décalage sur le front d'horloge négatif (de haut en bas).

Comme il n'y a pas de bulle avec la flèche d'horloge, le registre se décale sur le front d'horloge positif (transition bas à haut).

La flèche longue, après la légende C3/1 pointer vers la droite indique un décalage vers la droite, qui se trouve en bas du symbole.

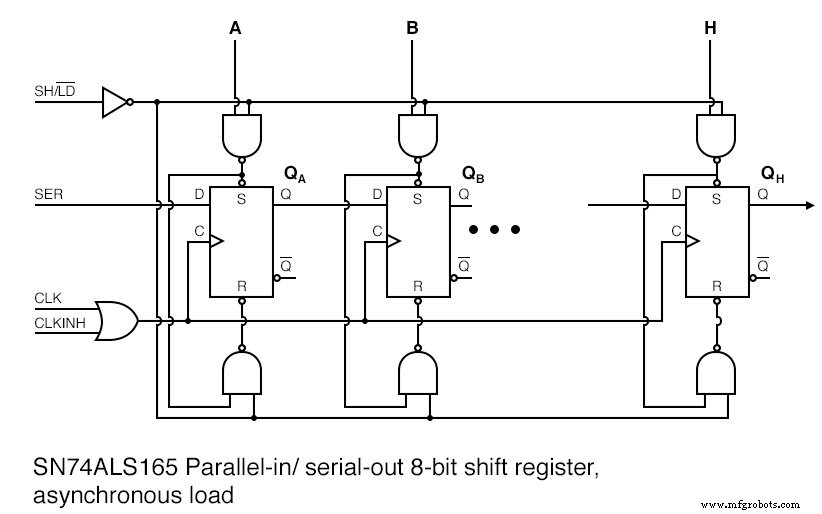

Une partie de la logique interne du registre à décalage de charge asynchrone à entrée parallèle/sortie série SN74ALS165 est reproduite à partir de la fiche technique ci-dessus.

Voir le lien au début de cette section pour le diagramme complet. Nous n'avons pas examiné le chargement asynchrone des données jusqu'à présent.

Tout d'abord, le chargement est accompli par application de signaux appropriés à l'Ensemble (prédéfini) et Réinitialiser (effacer) les entrées des Flip-Flops.

La NAND supérieure les portes alimentent l'Ensemble broches des FF et également en cascade dans la NAND inférieure portail alimentant le Reset broches des FF.

La NAND inférieure gate inverse le signal en partant du Set épingler sur Réinitialiser épingle.

Tout d'abord, SH/LD' doit être tiré Bas pour activer la NAND supérieure et inférieure portes.

Si SH/LD’ étaient à un niveau logique élevé à la place, l'onduleur alimente une logique faible à tous les NAND les portes forceraient un Élevé en relâchant le Set « actif bas » et Réinitialiser broches de tous les FF.

Il n'y aurait aucune possibilité de charger les FF.

Avec SH/LD’ tenue Faible , nous pouvons alimenter, par exemple, une donnée 1 à l'entrée parallèle A , qui s'inverse en zéro au niveau de la NAND supérieure sortie porte, réglage FF QA à un 1 .

Le 0 au Set la broche est alimentée à la NAND inférieure porte où il est inversé en un 1 , en relâchant la Réinitialiser broche de QA .

Ainsi, une donnée A=1 définit QA =1 . Comme rien de tout cela ne nécessitait l'horloge, le chargement est asynchrone par rapport à l'horloge.

Nous utilisons un registre à décalage de chargement asynchrone si nous ne pouvons pas attendre qu'une horloge charge les données en parallèle, ou s'il n'est pas pratique de générer une seule impulsion d'horloge.

La seule différence dans l'alimentation d'une donnée 0 à l'entrée parallèle A c'est qu'il s'inverse en un 1 hors de la porte supérieure libérant Set .

Ce 1 à Set est inversé en 0 à la porte inférieure, en tirant sur Reset à un Faible , qui réinitialise QA =0 .

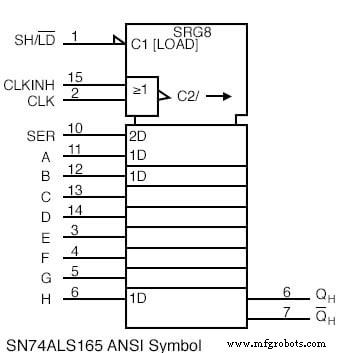

Le symbole ANSI pour le SN74ALS166 ci-dessus a deux contrôles internes C1 [CHARGER] et C2 horloge du OU fonction de (CLKINH, CLK ).

SRG8 dit levier de vitesses à 8 étages. La flèche après C2 indique un déplacement vers la droite ou vers le bas. SER l'entrée est fonction de l'horloge comme indiqué par l'étiquette interne 2D .

Les entrées de données parallèles A, B, C à H sont fonction de C1 [LOAD], indiqué par l'étiquette interne 1D .

C1 est affirmé lorsque sh/LD’ =0 grâce à l'inverseur demi-flèche à l'entrée.

Comparez cela au contrôle des entrées de données parallèles par l'horloge du précédent ANSI synchrone SN75ALS166. Notez les différences dans les étiquettes de données ANSI.

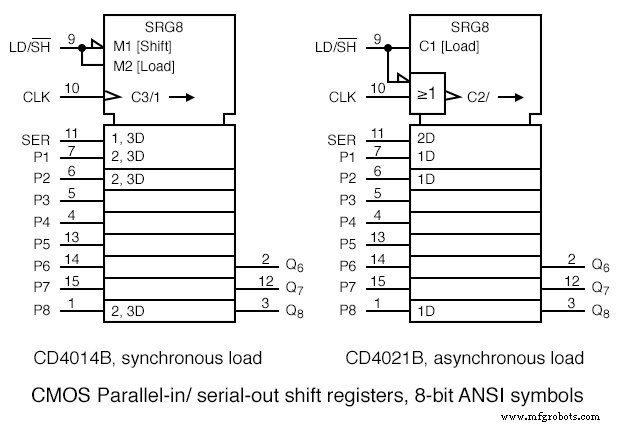

Sur le CD4014B ci-dessus, M1 est affirmé lorsque LD/SH'=0 . M2 est affirmé lorsque LD/SH’=1 .

Horloge C3/1 est utilisé pour le chargement parallèle des données en 2, 3D quand M2 est actif comme indiqué par le 2,3 étiquettes de préfixe.

Épingles P3 à P7 sont censés avoir le smae interne 2,3 préfixe les étiquettes en tant que P2 et P8 . Chez SER , le 1,3D le préfixe implique que M1 et horloge C3 sont nécessaires pour saisir des données série.

Le décalage vers la droite a lieu lorsque M1 actif est comme indiqué par le 1 dans la flèche C3/1 .

Le CD4021B est une pièce similaire à l'exception du chargement parallèle asynchrone des données, comme l'implique l'absence de 2 préfixe dans l'étiquette de données 1D pour les broches P1, P2, à P8.

Bien sûr, préfixe 2 dans l'étiquette 2D à l'entrée SER dit que les données sont synchronisées dans cette broche. Le OU l'encart de la porte montre que l'horloge est contrôlée par LD/SH' .

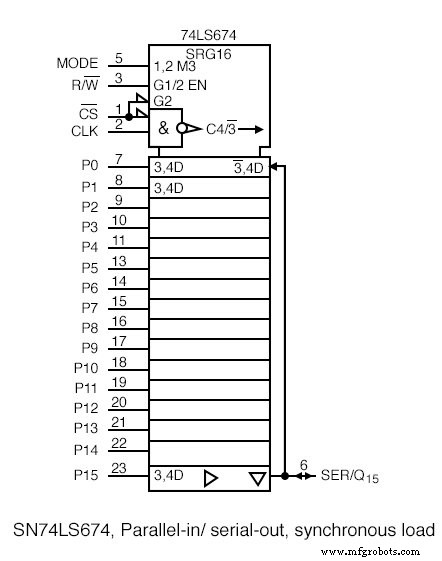

L'étiquette interne SN74LS674 ci-dessus SRG 16 indique un registre à décalage de 16 bits.

Le MODE l'entrée dans la section de contrôle en haut du symbole est étiquetée 1,2 M3 . Interne M3 est une fonction de l'entrée MODE et G1 et G2 comme indiqué par le 1,2 précédent M3 .

L'étiquette de base G indique un ET fonction d'un tel G contributions. Saisie R/W' est étiqueté en interne G1/2 EN .

Ceci est une activation FR (contrôlé par G1 ET G2 ) pour les appareils à trois états utilisés ailleurs dans le symbole.

Nous notons que CS' sur (broche 1) est interne G2 . Chip sélectionnez CS' est aussi ET ed avec l'entrée CLK pour donner l'horloge interne C4 .

La bulle à l'intérieur de la flèche d'horloge indique que l'activité est sur le front d'horloge négatif (transition haute à basse).

La barre oblique (/) est un séparateur impliquant deux fonctions pour l'horloge. Avant la barre oblique, C4 indique le contrôle de n'importe quoi avec un préfixe de 4 .

Après la barre oblique, le 3' (flèche) indique un déplacement. Le 3’ de C4/3’ implique un décalage lorsque M3 est désactivé (MODE=0 ). La flèche longue indique un décalage vers la droite (vers le bas).

En descendant sous la section de contrôle jusqu'à la section de données, nous avons des entrées externes P0-P15 , broches (7-11, 13-23).

Le préfixe 3,4 de l'étiquette interne 3,4D indique que M3 et l'horloge C4 contrôler le chargement des données parallèles.

Le D signifie Données. Cette étiquette est supposée s'appliquer à toutes les entrées parallèles, bien qu'elle ne soit pas explicitement écrite.

Repérez l'étiquette 3',4D à droite du P0 (broche7) stade. Le complémenté-3 indique queM3=MODE=0 entrées (quarts) SER/Q15 (broche5) à l'heure de l'horloge, (4 de 3',4D) correspondant à l'horloge C4 .

En d'autres termes, avec MODE=0 , nous déplaçons les données dans Q0 de l'entrée série (broche 6). Toutes les autres étapes se décalent vers la droite (vers le bas) à l'heure de l'horloge.

En se déplaçant vers le bas du symbole, le triangle pointant vers la droite indique un tampon entre Q et la broche de sortie.

Le triangle pointant vers le bas indique un périphérique à trois états. Nous avons précédemment indiqué que le tristate est contrôlé par enable EN , qui est en fait G1 ET G2 de la section de contrôle.

Si R/W=0 , le tri-état est désactivé, et nous pouvons déplacer les données dans Q0 via SER (broche 6), un détail que nous avons omis ci-dessus. Nous avons en fait besoin de MODE=0, R/W'=0, CS'=0

La logique interne du SN74LS674 et un tableau résumant le fonctionnement des signaux de commande sont disponibles dans le lien dans la liste à puces, en haut de la section.

Si R/W'=1 , le tristate est activé, Q15 décale SER/Q15 (broche 6) et recircule vers le Q0 étape via le fil de droite vers 3',4D .

Nous avons supposé que CS' était bas, nous donnant l'horloge C4/3' et G2 à EN capable les trois états.

Applications pratiques

Une application d'un registre à décalage entrée parallèle/sortie série consiste à lire des données dans un microprocesseur.

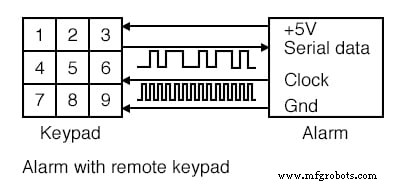

L'alarme ci-dessus est contrôlée par un clavier à distance. Le boîtier d'alarme fournit +5V et terre au clavier à distance pour l'alimenter.

L'alarme lit le clavier distant toutes les quelques dizaines de millisecondes en envoyant des horloges de décalage au clavier qui renvoie des données série indiquant l'état des touches via un registre à décalage entrée/sortie parallèle.

Ainsi, nous lisons neuf interrupteurs à clé avec quatre fils. Combien de fils faudrait-il si nous devions faire fonctionner un circuit pour chacune des neuf touches ?

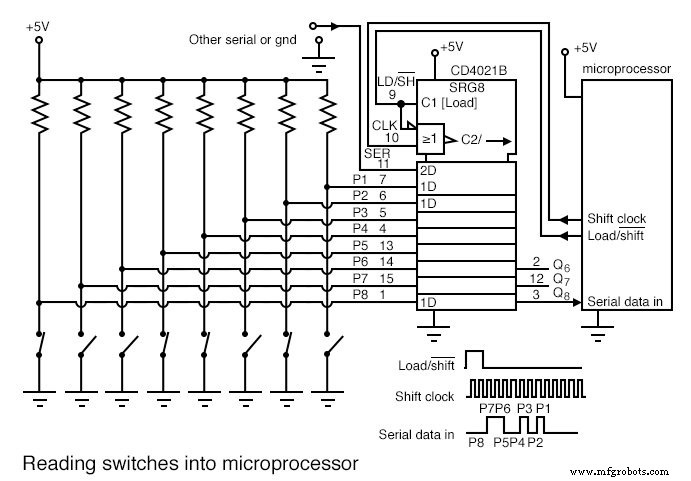

Une application pratique d'un registre à décalage entrée parallèle/sortie série consiste à lire de nombreuses fermetures de commutateur dans un microprocesseur sur quelques broches seulement.

Certains microprocesseurs bas de gamme n'ont que 6 broches d'E/S (entrée/sortie) disponibles sur un boîtier à 8 broches.

Ou, nous avons peut-être utilisé la plupart des broches sur un boîtier à 84 broches. Nous pouvons vouloir réduire le nombre de fils autour d'un circuit imprimé, d'une machine, d'un véhicule ou d'un bâtiment.

Cela augmentera la fiabilité de notre système. Il a été rapporté que les fabricants qui ont réduit le nombre de fils dans une automobile produisent un produit plus fiable.

Dans tous les cas, seules trois broches du microprocesseur sont nécessaires pour lire 8 bits de données à partir des commutateurs de la figure ci-dessus.

Nous avons choisi un dispositif de chargement asynchrone, le CD4021B car il est plus facile de contrôler le chargement des données sans avoir à générer une seule horloge de chargement parallèle.

Les entrées de données parallèles du registre à décalage sont tirées jusqu'à +5V avec une résistance sur chaque entrée.

Si tous les commutateurs sont ouverts, tous les 1 s sera chargé dans le registre à décalage lorsque le microprocesseur déplacera le LD/SH’ ligne de bas en haut, puis de nouveau bas en prévision du changement.

Toute fermeture d'interrupteur appliquera la logique 0 s aux entrées parallèles correspondantes. Le modèle de données à P1-P7 sera chargé en parallèle par le LD/SH'=1 généré par le logiciel du microprocesseur.

Le microprocesseur génère des impulsions de décalage et lit un bit de données pour chacun des 8 bits.

Ce processus peut être effectué entièrement avec un logiciel, ou des microprocesseurs plus gros peuvent avoir une ou plusieurs interfaces série pour effectuer la tâche plus rapidement avec du matériel.

Avec LD/SH’=0 , le microprocesseur génère un 0 à 1 transition sur la ligne d'horloge de décalage , puis lit un bit de données sur les Données série dans ligne. Ceci est répété pour tous les 8 bits.

Le SER La ligne du registre à décalage peut être pilotée par un autre circuit CD4021B identique si davantage de contacts de commutation doivent être lus.

Dans ce cas, le microprocesseur génère 16 impulsions de décalage. Plus probablement, il sera piloté par quelque chose d'autre compatible avec ce format de données série, par exemple, un convertisseur analogique-numérique, un capteur de température, un lecteur de clavier, une mémoire série en lecture seule.

Quant aux fermetures d'interrupteurs, il peut s'agir de fins de course sur le chariot d'une machine, d'un capteur de surchauffe, d'un interrupteur reed magnétique, d'un interrupteur de porte ou fenêtre, d'un pressostat air ou eau, ou encore d'un interrupteur optique à semi-conducteurs. /P>

FICHES DE TRAVAIL CONNEXES :

- Feuille de travail des registres à décalage

Technologie industrielle