Registres à décalage :entrée série, sortie série

Les registres à décalage d'entrée et de sortie série retardent les données d'un temps d'horloge pour chaque étape.

Ils stockeront un peu de données pour chaque registre. Un registre à décalage d'entrée et de sortie série peut avoir une longueur de 1 à 64 bits, plus long si les registres ou les packages sont en cascade.

Ci-dessous se trouve un registre à décalage à un étage recevant des données qui ne sont pas synchronisées avec l'horloge du registre.

Les « données entrantes » au D broche de type D FF (Flip-Flop) ne change pas de niveau lorsque l'horloge passe de bas en haut.

Nous pouvons souhaiter synchroniser les données avec une horloge à l'échelle du système dans une carte de circuit imprimé pour améliorer la fiabilité d'un circuit logique numérique.

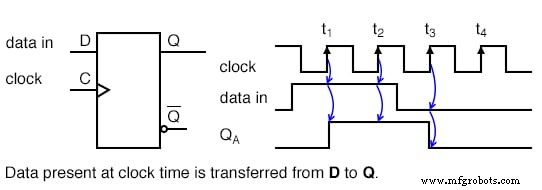

Le point évident (par rapport à la figure ci-dessous) illustré ci-dessus est que toutes les « données entrantes » sont présentes au D broche de type D FF est transféré de D à la sortie Q à l'heure de l'horloge.

Étant donné que notre exemple de registre à décalage utilise des éléments de stockage sensibles aux fronts positifs, la sortie Q suit le D entrée lorsque l'horloge passe de bas en haut, comme indiqué par les flèches vers le haut sur le diagramme ci-dessus.

Il n'y a aucun doute sur le niveau logique présent au moment de l'horloge car les données sont stables bien avant et après le front d'horloge.

C'est rarement le cas dans les registres à décalage à plusieurs étages. Mais, c'était un exemple facile pour commencer. Nous ne sommes concernés que par le front d'horloge positif, bas à haut.

Le front descendant peut être ignoré. Il est très facile de voir Q suivre D à l'heure ci-dessus.

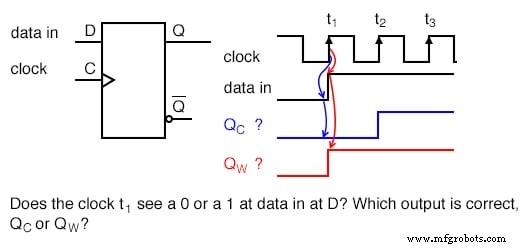

Comparez cela au diagramme ci-dessous où les « données entrantes » semblent changer avec le front d'horloge positif.

Étant donné que les « données entrantes » semblent changer à l'heure t1 ci-dessus, qu'est-ce que le type D FF voir à l'heure ?

La réponse courte et simplifiée est qu'il voit les données qui étaient présentes à D avant l'horloge.

C'est ce qui est transféré à Q à l'heure t1 . La forme d'onde correcte est QC . À t1 Q passe à zéro s'il n'est pas déjà zéro.

Le D le registre ne voit pas de un jusqu'au temps t2 , auquel moment Q devient élevé.

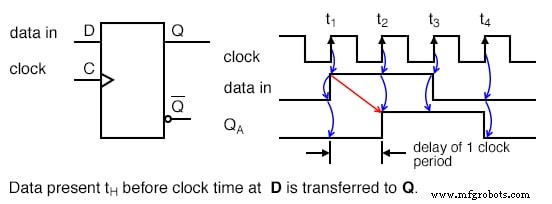

Étant donné que les données ci-dessus sont présentes à D est cadencé à Q à l'heure de l'horloge, et Q ne peut pas changer jusqu'à la prochaine heure d'horloge, le D FF retarde les données d'une période d'horloge, à condition que les données soient déjà synchronisées avec l'horloge. Le QA la forme d'onde est la même que "data in" avec un délai d'une période d'horloge.

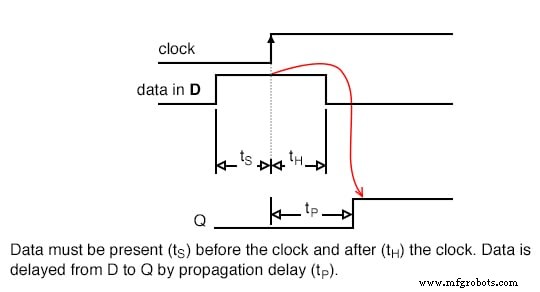

Un regard plus détaillé sur ce que l'entrée de type D Flip-Flop voit à l'heure de l'horloge suit.

Reportez-vous à la figure ci-dessous. Étant donné que les « données entrantes » semblent changer à l'heure de l'horloge (ci-dessus), nous avons besoin de plus d'informations pour déterminer ce que le D FF voit.

Si les « données entrantes » proviennent d'un autre étage de registre à décalage, un autre même type D FF, nous pouvons tirer quelques conclusions sur la base de la fiche technique informations.

Les fabricants de logique numérique mettent à disposition des informations sur leurs pièces dans des fiches techniques, auparavant uniquement disponibles dans une collection appelée data book .

Les recueils de données sont toujours disponibles ; cependant, le site Web du fabricant est la source moderne.

Les données suivantes ont été extraites de la fiche technique CD4006b pour un fonctionnement à 5VDC , qui sert d'exemple pour illustrer le timing. [*]

- tS =100 ns

- tH =60ns

- tP =200-400ns typ/max

tS est l'heure d'installation , les données d'heure doivent être présentes avant l'heure de l'horloge. Dans ce cas, les données doivent être présentes à D 100 ns avant l'horloge.

De plus, les données doivent être conservées pendant temps de conservation tH =60ns après l'heure de l'horloge. Ces deux conditions doivent être remplies pour cadencer de manière fiable les données de D à Q de la tong.

Il n'y a aucun problème à respecter le temps d'installation de 60 ns car les données à D a été là pendant toute la période d'horloge précédente s'il provient d'un autre étage de registre à décalage.

Par exemple, à une fréquence d'horloge de 1 Mhz, la période d'horloge est de 1000 µs, beaucoup de temps.

Les données seront en fait présentes pendant 1000 µs avant l'horloge, ce qui est bien supérieur au minimum requis tS de 60ns.

Le temps de maintien tH =60ns est atteint car D connecté à Q d'un autre étage ne peut pas changer plus rapidement que le délai de propagation de l'étage précédent tP =200ns.

Le temps de maintien est respecté tant que le délai de propagation du D précédent FF est supérieur au temps de maintien.

Données à D entraîné par une autre étape Q ne changera pas plus vite que 200ns pour le CD4006b.

Pour résumer, la sortie Q suit l'entrée D presque à l'heure de l'horloge si les bascules sont mises en cascade dans un registre à décalage à plusieurs étages.

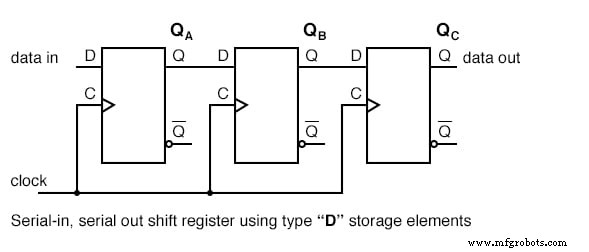

Trois types D Les bascules sont montées en cascade Q à D et les horloges sont mises en parallèle pour former un registre à décalage à trois étages au-dessus.

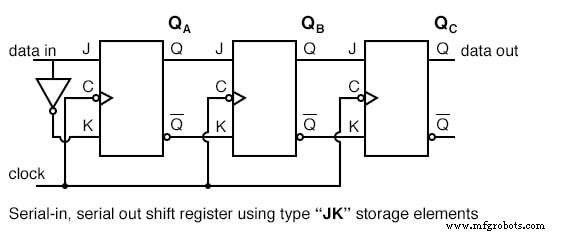

Tapez JK Les bascules ont mis en cascade Q à J, Q' à K avec des horloges en parallèle pour produire une forme alternative du registre à décalage ci-dessus.

Un registre à décalage d'entrée/sortie série a une entrée d'horloge, une entrée de données et une sortie de données du dernier étage.

En général, les autres sorties d'étage ne sont pas disponibles. Sinon, il s'agirait d'un registre à décalage à entrée série et sortie parallèle.

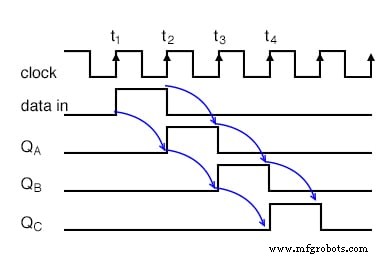

Les formes d'onde ci-dessous sont applicables à l'une ou l'autre des deux versions précédentes du registre à décalage d'entrée et de sortie série.

Les trois paires de flèches montrent qu'un registre à décalage à trois étages stocke temporairement 3 bits de données et les retarde de trois périodes d'horloge de l'entrée à la sortie.

A l'heure t1 un « données entrantes » de 0 est cadencé à partir de D à Q des trois étapes. En particulier, D de l'étape A voit une logique 0 , qui est cadencé à QA où il reste jusqu'au temps t2 .

A l'heure t2 un « données entrantes » de 1 est cadencé à partir de D à QA . Aux stades B et C , un 0 , alimenté par les étages précédents est cadencé à QB et QC .

A l'heure t3 un « données entrantes » de 0 est cadencé à partir de D à QA . QR devient faible et reste faible pour les horloges restantes en raison du fait que les "données entrantes" sont 0 . QB monte à t3 en raison d'un 1 de l'étape précédente. QC est toujours faible après t3 en raison d'un creux de l'étape précédente.

QC monte enfin à l'horloge t4 en raison de l'alimentation élevée de D de l'étape précédente QB . Toutes les étapes précédentes ont 0 s déplacé en eux. Et, après la prochaine impulsion d'horloge à t5 , toute logique 1 s aura été déplacé, remplacé par 0 s

Périphériques d'entrée/sortie série

Nous allons examiner de plus près les pièces suivantes disponibles sous forme de circuits intégrés, avec l'aimable autorisation de Texas Instruments.

Pour les fiches techniques complètes des appareils, suivez les liens.

- CD4006b Registre à décalage d'entrée/sortie série 18 bits

- CD4031b Registre à décalage d'entrée/sortie série 64 bits

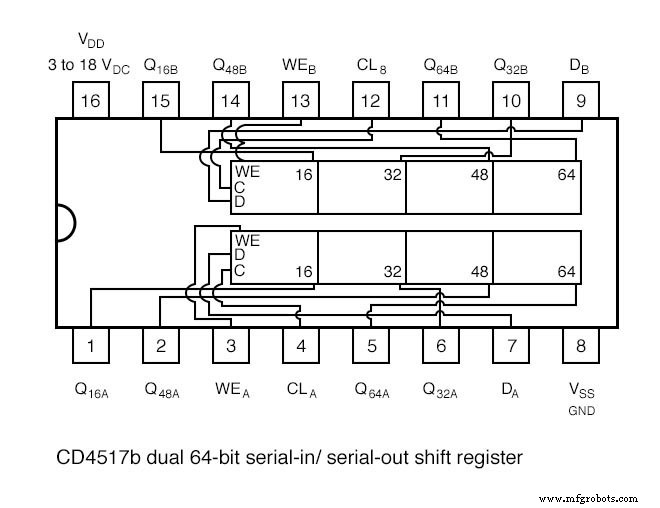

- CD4517b double registre à décalage entrée/sortie série 64 bits

Les registres à décalage d'entrée/sortie série suivants sont des CMOS de la série 4000 (Complementary Metal Oxide Semiconductor) pièces de la famille.

En tant que tel, ils accepteront un VDD , alimentation positive de 3-Volts à 15-Volts. Le VSS la broche est mise à la terre.

La fréquence maximale de l'horloge de décalage, qui varie avec VDD , est de quelques mégahertz.

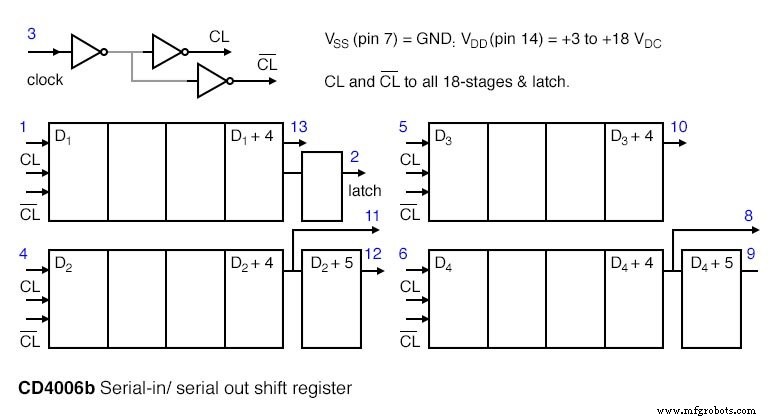

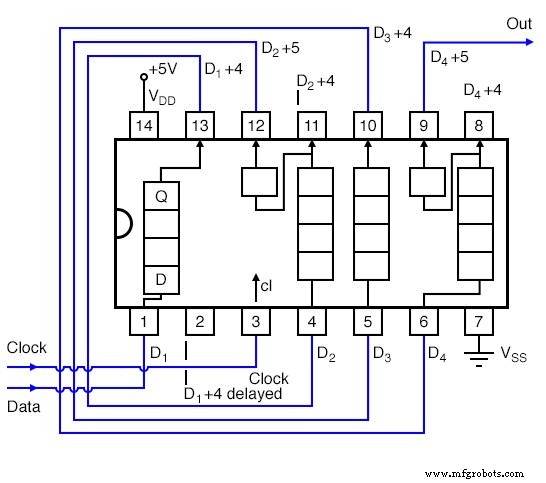

Le CD4006b 18 bits se compose de deux étages de 4 bits et de deux autres étages de 5 bits avec une prise de sortie à 4 bits.

Ainsi, les étages de 5 bits pourraient être utilisés comme registres à décalage de 4 bits.

Pour obtenir un registre à décalage complet de 18 bits, la sortie d'un registre à décalage doit être mise en cascade à l'entrée d'un autre et ainsi de suite jusqu'à ce que tous les étages créent un seul registre à décalage, comme indiqué ci-dessous.

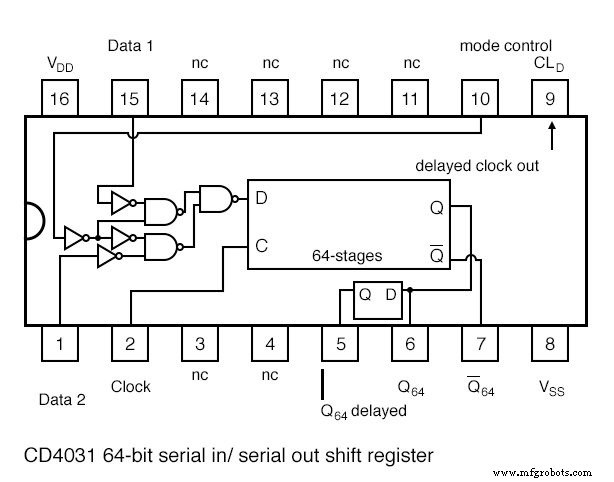

Un registre à décalage d'entrée/sortie série CD4031 64 bits est illustré ci-dessous.

Un certain nombre de broches ne sont pas connectées (nc). Q et Q' sont tous deux disponibles à partir de la 64e étape, en fait Q64 et Q'64 .

Il existe également un Q64 « retardé » à partir d'un demi-étage qui est retardé d'un demi-cycle d'horloge. Une caractéristique majeure est un sélecteur de données qui se trouve à l'entrée des données dans le registre à décalage.

Le « contrôle de mode » sélectionne entre deux entrées :les données 1 et les données 2. Si le « contrôle de mode » est élevé, les données seront sélectionnées à partir de « données 2 » pour l'entrée dans le registre à décalage.

Dans le cas où le « contrôle de mode » est au niveau logique bas, la « donnée 1 » est sélectionnée. Des exemples sont illustrés dans les deux figures ci-dessous.

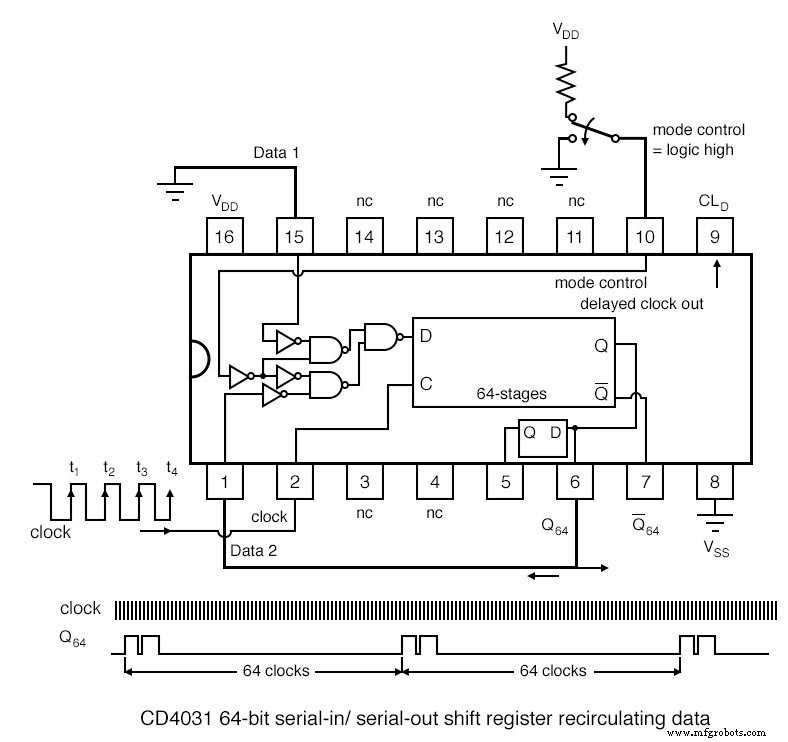

Les "données 2" ci-dessus sont câblées au Q64 sortie du registre à décalage. Avec un « contrôle de mode » élevé, le Q64 la sortie est renvoyée à l'entrée de données du levier de vitesses D.

Les données seront recirculées de la sortie à l'entrée. Les données se répéteront toutes les 64 impulsions d'horloge comme indiqué ci-dessus.

La question qui se pose est de savoir comment ce modèle de données est-il entré dans le registre à décalage en premier lieu ?

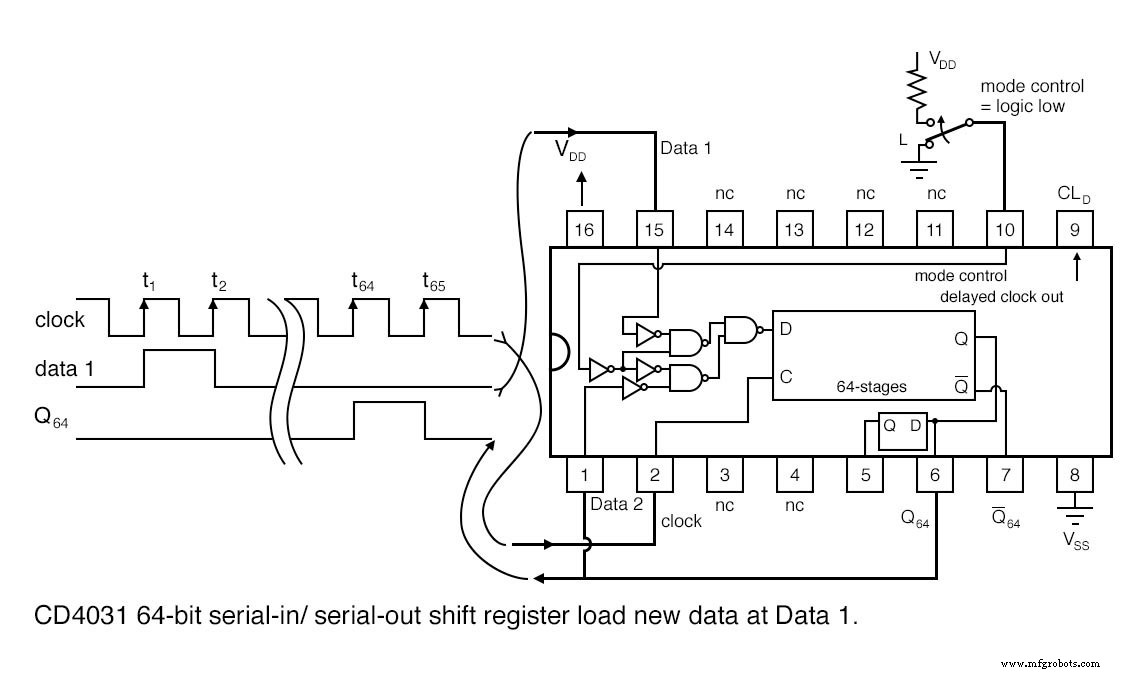

Avec le « contrôle de mode » bas, le CD4031 « données 1 » est sélectionné pour être entré dans le levier de vitesses.

La sortie, Q64 , n'est pas remis en circulation car la porte inférieure du sélecteur de données est désactivée .

Par désactivé, nous entendons que la "sélection de mode" logique basse inversée deux fois à un niveau bas à la porte NAND inférieure l'empêche de transmettre tout signal sur la broche inférieure (données 2) à la sortie de la porte.

Ainsi, il est désactivé.

Un double registre à décalage de 64 bits CD4517b est illustré ci-dessus. Notez les robinets aux 16e, 32e et 48e étages.

Cela signifie que les registres à décalage de ces longueurs peuvent être configurés à partir de l'un des décaleurs 64 bits.

Bien entendu, les décaleurs 64 bits peuvent être mis en cascade pour produire un registre à décalage 80 bits, 96 bits, 112 bits ou 128 bits.

L'horloge CLA et CLB doivent être mis en parallèle lors de la mise en cascade des deux manettes. NOUSB et NOUSB sont mis à la terre pour les opérations de changement de vitesse normales.

Les entrées de données dans les registres à décalage A et B sont DA et DB respectivement.

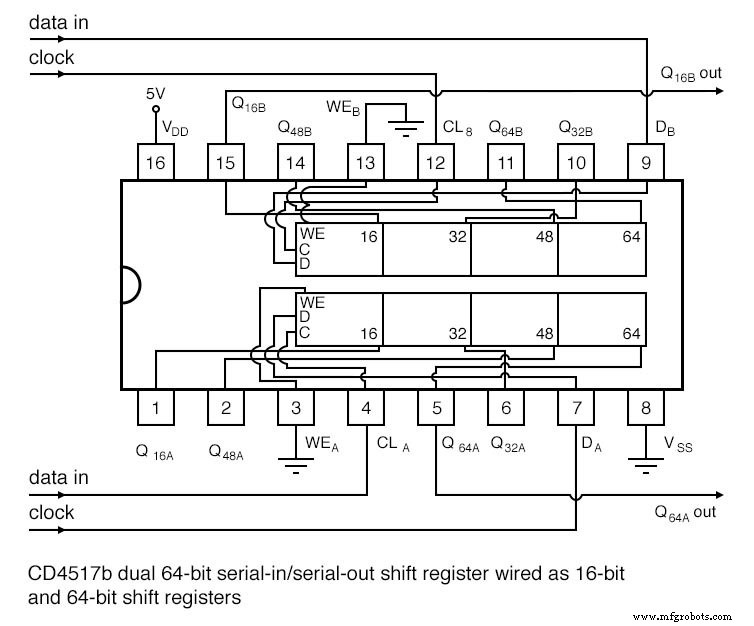

Supposons que nous ayons besoin d'un registre à décalage de 16 bits.

Cela peut-il être configuré avec le CD4517b ? Que diriez-vous d'un registre à 64 décalages de la même pièce ?

Ci-dessus, nous montrons un CD4517b câblé comme un registre à décalage 16 bits pour la section B.

L'horloge de la section B est CLB . Les données sont pointées à CLB . Et les données retardées de 16 horloges sont supprimées de Q16B . NOUSB , l'autorisation d'écriture est mise à la terre.

Ci-dessus, nous montrons également le même CD4517b câblé comme un registre à décalage 64 bits pour la section indépendante A.

L'horloge de la section A est CLA . Les données entrent à CLA . Les données retardées de 64 impulsions d'horloge sont récupérées à partir de Q64A . NOUSA , l'autorisation d'écriture pour la section A est mise à la terre.

FICHES DE TRAVAIL CONNEXES :

- Feuille de travail des registres à décalage

Technologie industrielle